Home > Hiring!

Welcome to OWL: Unleash Your Potential with UROP

What's UROP

The Undergraduate Research Opportunities Program (UROP) is a HKUST signature program designed to provide undergraduate students with an exciting opportunity to engage in academic research, thereby helping them to develop insightful perspectives on their areas of interest and advance the frontiers of knowledge.

Launched in 2005, UROP has been well received by both students and faculty members. It is now offered in three semesters (Fall, Spring and Summer) throughout the academic year, which allows students to immerse themselves in a variety of tailor-made research projects under the supervision of world-class researchers.

Please explore this website to obtain up-to-date information on upcoming research opportunities at OWL and to learn how UROP can provide you with a challenging and intellectually stimulating experience.

UROP Projects at OWL

1. Optical transmitter design.

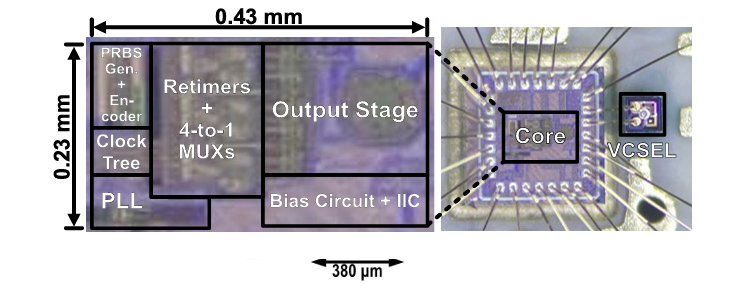

This project aims to optimize a vertical-cavity surface-emitting laser (VCSEL) transmitter integrated circuit (IC) for next-generation optical communications, leveraging the design platform and resources of HKUST's Optical Wireless Lab (OWL). Students will systematically study the principles of VCSEL-based optical communication, analyze existing transmitter modules (including multiplexer, clock tree, and output driver) implemented in a 40-nm process, and migrate the design to a 28-nm technology node. The work involves comprehensive pre- and post-layout simulation to verify functionality and evaluate the performance improvements achieved through technology scaling. The following figure shows our previous related work: A 56-Gb/s PAM-4 VCSEL Transmitter. Click the title for more information.

We also provide some open-source circuits and simulation results here for your reference:

Fig 1. Die photograph of our previous related work: A 56-Gb/s PAM-4 VCSEL Transmitter.

2. Millimeter-wave transceiver design.

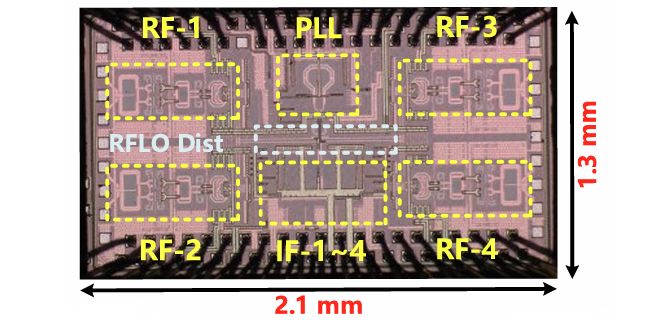

This project focuses on simulating and optimizing an existing phased-array transmitter for mmWave 5G/6G and satellite communication. Students will study transmitter fundamentals, migrate key blocks—including power amplifiers, mixers, and variable-gain amplifiers—from TSMC 40-nm to 28-nm CMOS technology, and perform pre- and post-layout simulations to verify functionality and assess performance gains from technology scaling. The figure below shows our previous related work: A 28-GHz Phased-Array Transceiver. Click the title for more information.

We also provide some open-source circuits and simulation results here for your reference:

Fig 2. Die photograph of our previous related work: A 28-GHz Phased-Array Transceiver.

3. Multi-phase clock generator design.

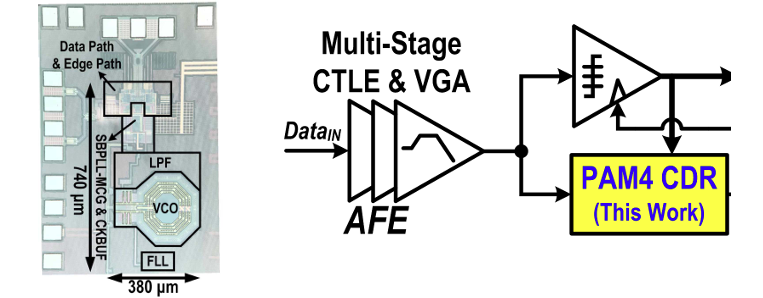

This project optimizes a multiphase clock generator (MCG) for next-generation wireline communications using HKUST's OWL lab resources. Students will analyze and migrate existing MCG blocks—phase detector, charge pump, frequency detector, and ring oscillator—from TSMC 40-nm to 28-nm CMOS technology. The work includes pre- and post-layout simulation to verify functionality and evaluate performance improvements achieved through technology scaling. The figure below shows the die photograph and the simplified block diagram of our previous related work: A 32-Gb/s 0.46-pJ/bit PAM4 CDR. Click the title for more information.

We also provide some open-source circuits and simulation results here for your reference:

Fig 3. Die photograph and the simplified block diagram of our previous related work: A 32-Gb/s 0.46-pJ/bit PAM4 CDR.