# Advanced Wireline and Optical Communication IC Design 高级有线及光通信 IC 设计

Prof. C. Patrick Yue 俞捷教授

**ECE ICDC OWL**

芯动力人才计划®第 125 期国际名家讲堂

# Integrated Circuit Design Center 芯 片設計研究中心

# **Key Research Areas**

→ VLSI architectures for deep learning

and digital baseband applications

**RF Integrated Circuits** and Systems

→ mm-wave/sub-THz IC, visible light communication and optical transceiver

→ vision, temperature, humidity and gas sensors

wireless power transfer and energy harvesting IC

**VLSI System**

→ low-voltage and lowpower analog IC for IoT

→ embedded system security, performance and power efficient multicore system

Source: Qualcomm

# **HKUST ICDC Faculty Profiles**

- 14 faculty (6 Fellows of IEEE, 1 Fellow of Optica, ACM & FAAAS)

- 100 post-docs, RAs, PhD and MPhil students

Patrick YUE Stanford FIEEE, FOptica

Wing Hung KI UCLA

Tim CHENG UC Berkeley FIEEE

Yuan XIE Princeton FIEEE, FACM, FAAAS

Mansun CHAN UC Berkeley FIEEE

Ricky LEE Purdue FIFFE

Yihan ZHANG Columbia

Wei ZHANG Princeton

Howard LUONG UC Berkeley FIEEE

Chi Ying TSUI

George YUAN UPenn

Khawar SARFRAZ HKUST

Zhiyao XIE Duke

Fengbin TU Tsinghua

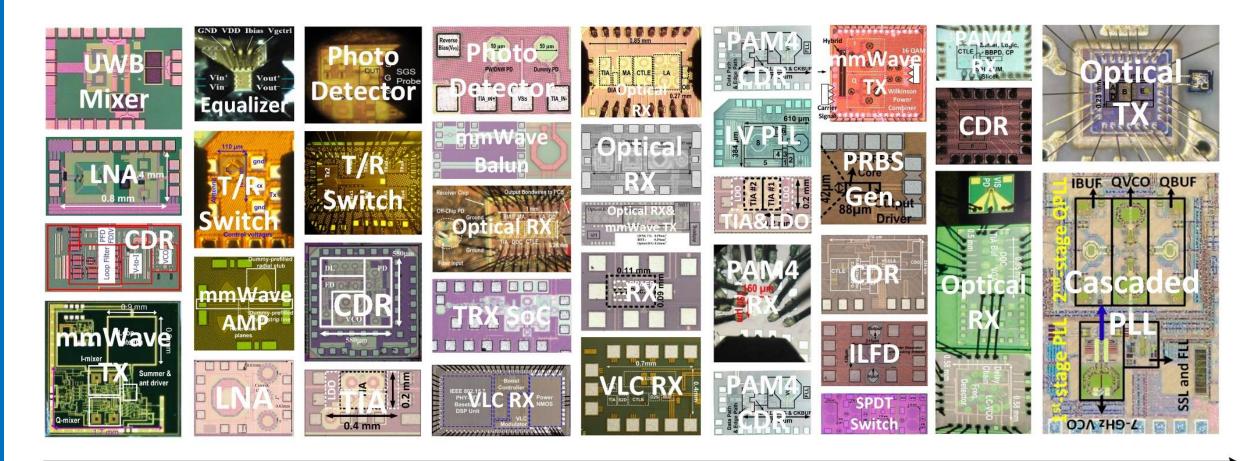

# Optical Wireless Lab (OWL 99) Chip Gallery

2007~2013 2014 2015 2016 2017 2018 2019 2020 2021 2022 2023

# **Chip Testing Demo**

港科大光电无线实验室个人主页-哔哩哔哩视频 (bilibili.com)

28-GHz 中频移相相控阵芯片演示

#### **Short Course Outline**

- Background, Application, and Trend (<u>BAT</u>)

- Transmitter (Tx) [Tx Ref]

- Receiver (Rx) [Rx Ref]

- Clock & Data Recovery (<u>CDR</u>) [<u>CDR Ref</u>]

- Practical Implementation Techniques (PIT) [PIT Ref]

Acknowledgements (OWL 99 Alumni)

# Acknowledgements (OWL Turrent Members)

# Background, Applications, and Trends for High-Speed Serial Links

- Applications

- Characteristics of the Architecture

- Technology Choices

- Performance Metric

- Trends

# Wireline and Optical Transmitter

- Architecture

- VCSEL Transmitter

- MRM Transmitter

- MZM Transmitter

- Wireline Transmitter

- Key Circuits

- Multiplexer (GitHub: <u>4-to1-MUX-for-28Gbaud-Optical-TX</u>)

- Output Driver

- Pre-emphasis

- Practical Issues

- EMI Suppression Due to CM Noise to Reduce Radiation Emissions

# Wireline and Optical Receiver

- Motivation

- Electrical vs Optical Link

- Architecture

- Wireline vs Optical Receiver

- ADC-Based Receiver

- Key Circuits

- PD Interface

- Multiple Peaking in TIA

- Modified Cherry-Hooper Amplifier

- FFE and DFE Implementation

- Practical Issues

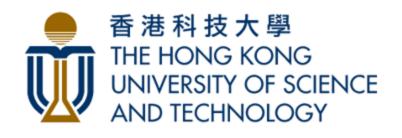

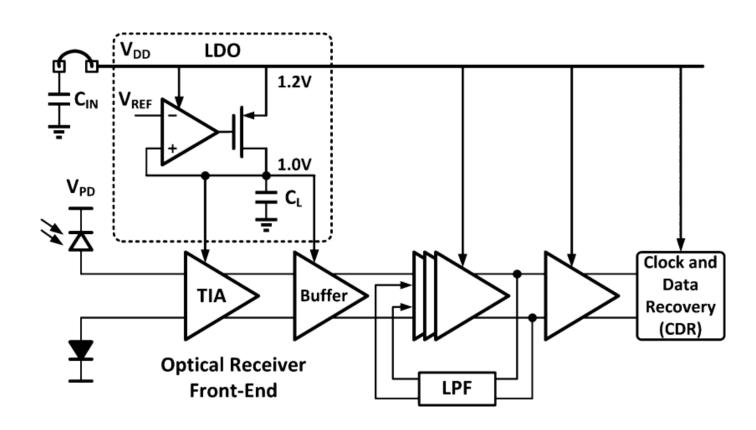

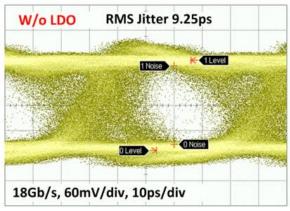

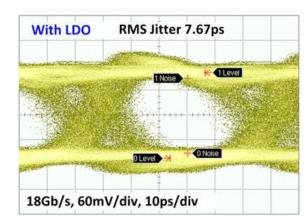

- On-Chip LDO for Improved Sensitivity

- Conclusion

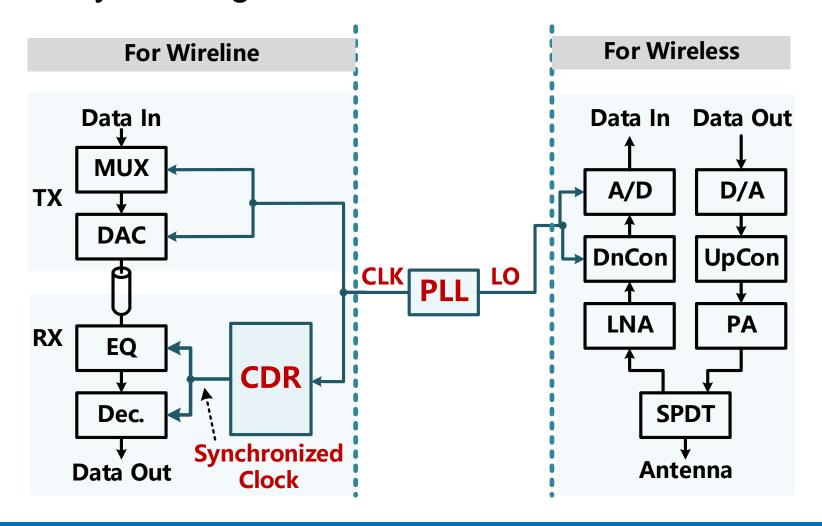

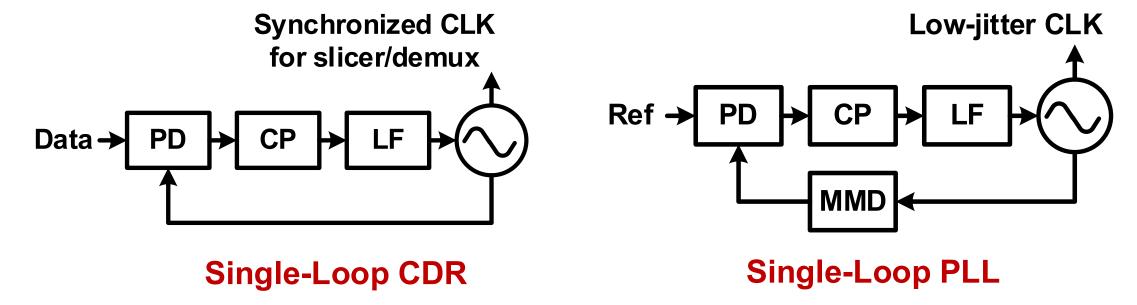

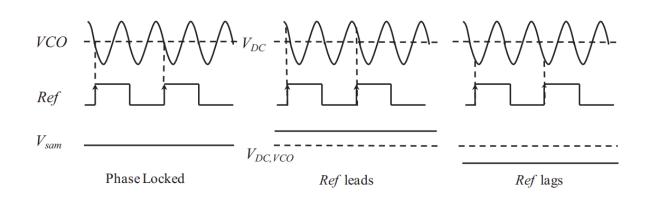

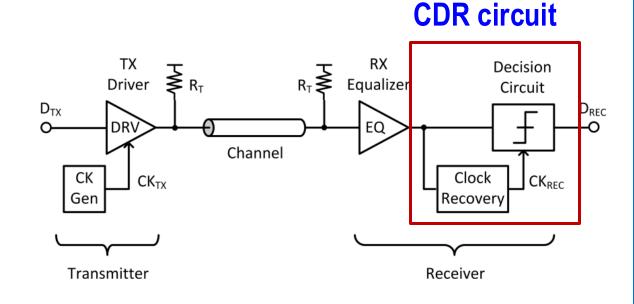

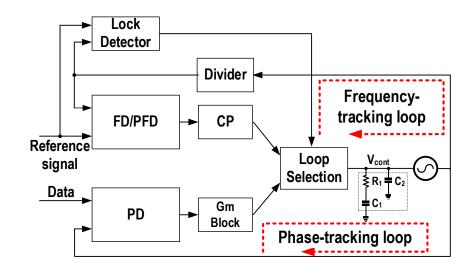

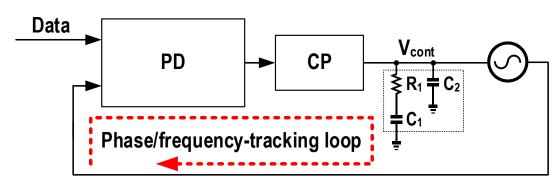

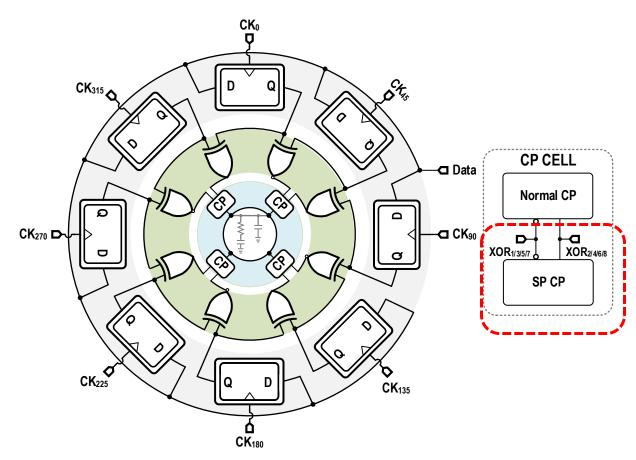

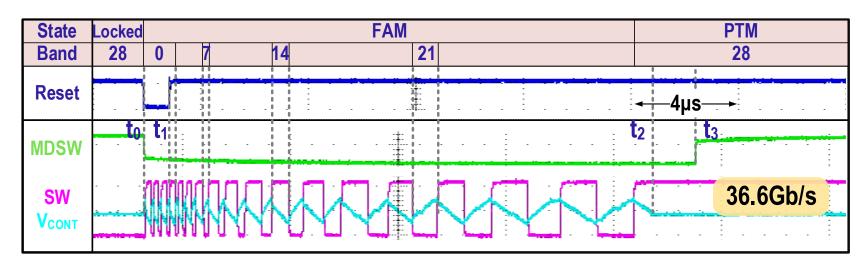

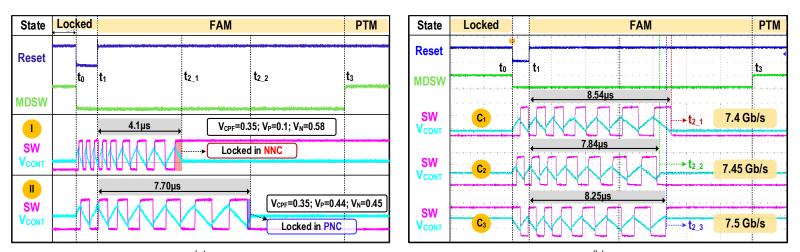

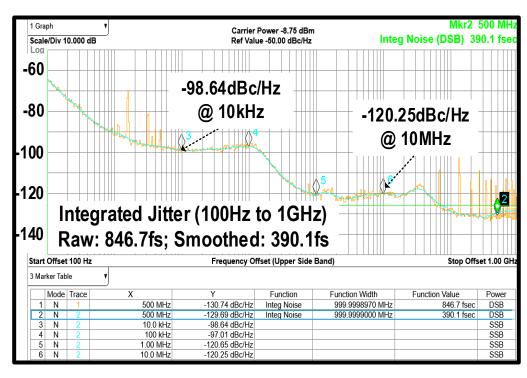

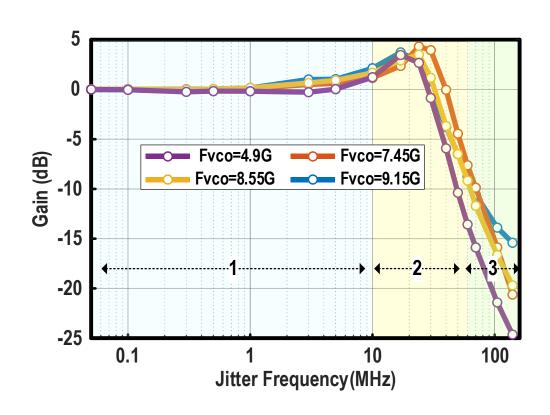

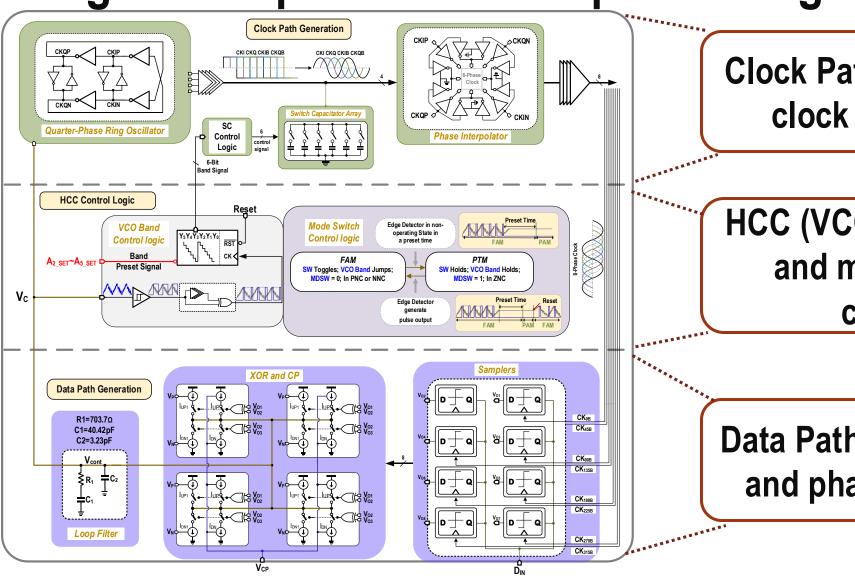

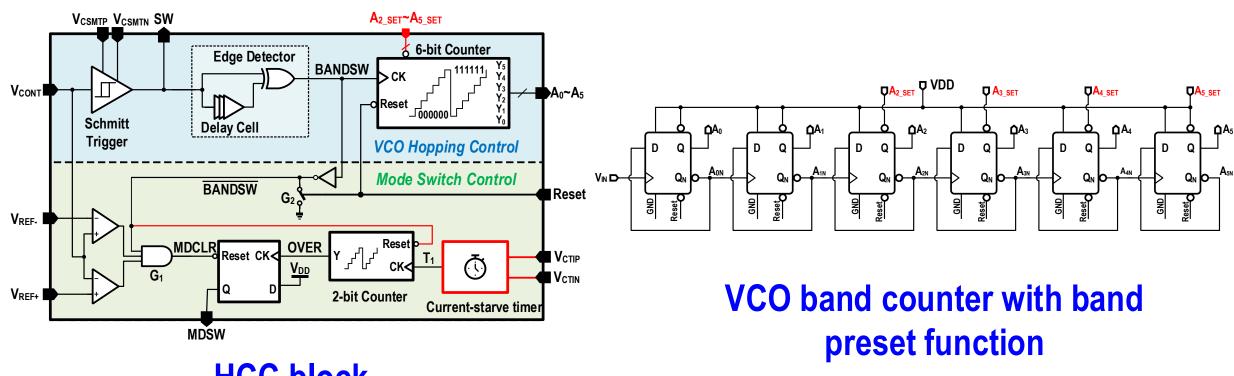

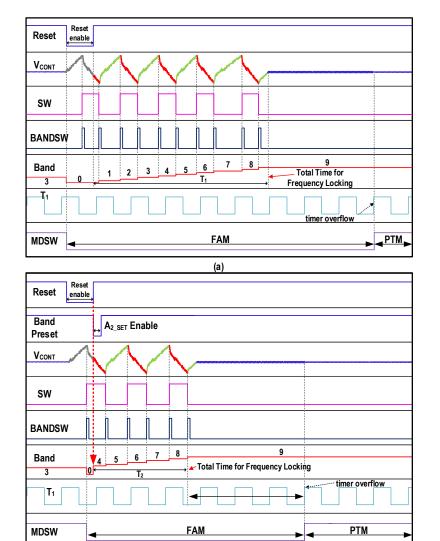

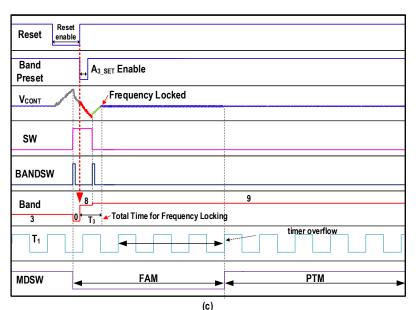

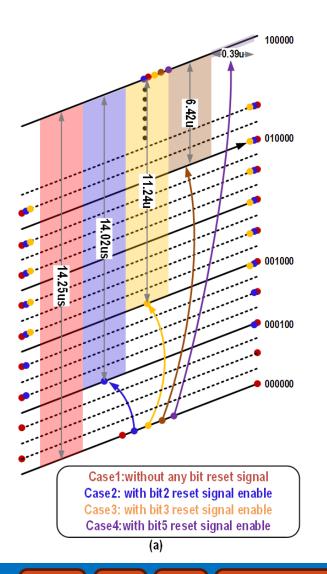

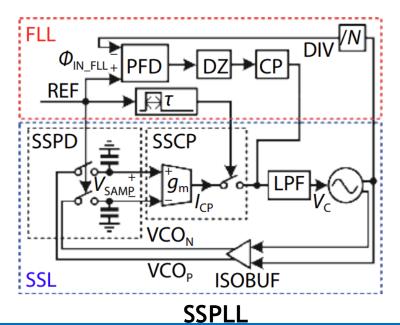

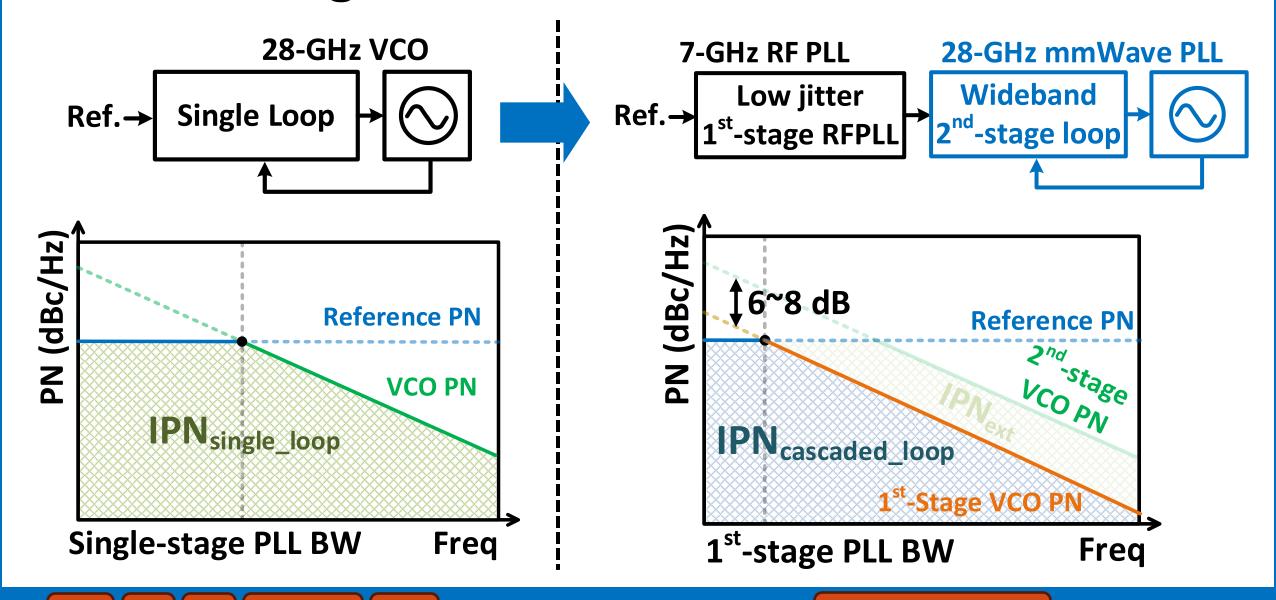

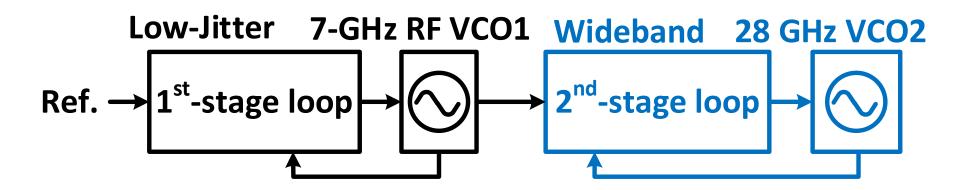

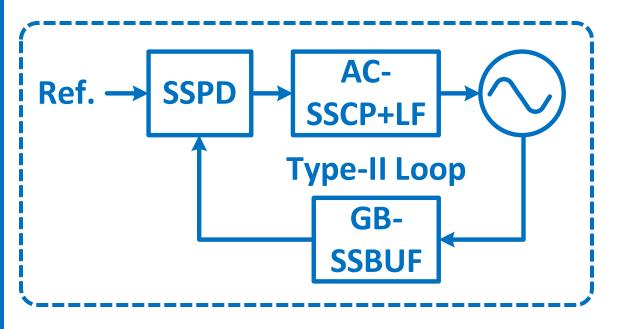

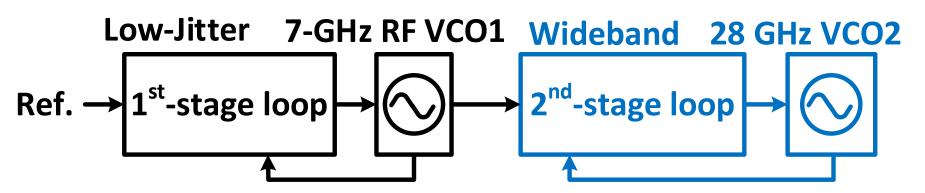

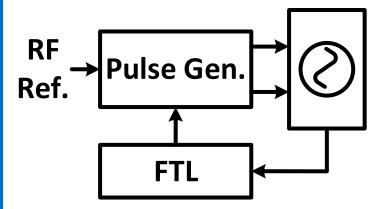

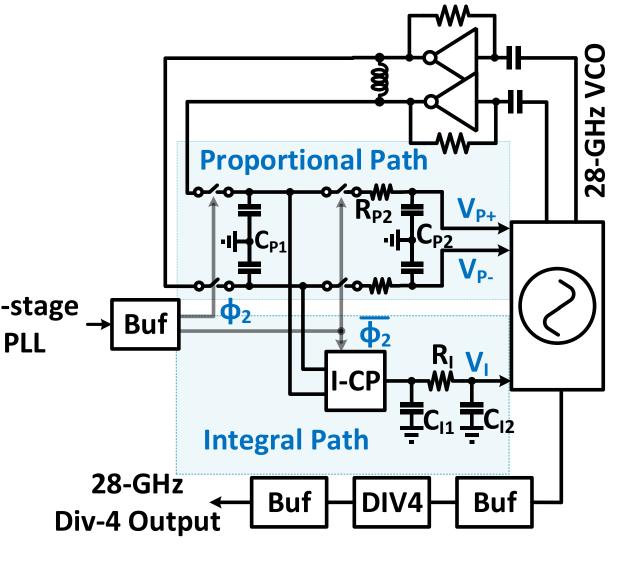

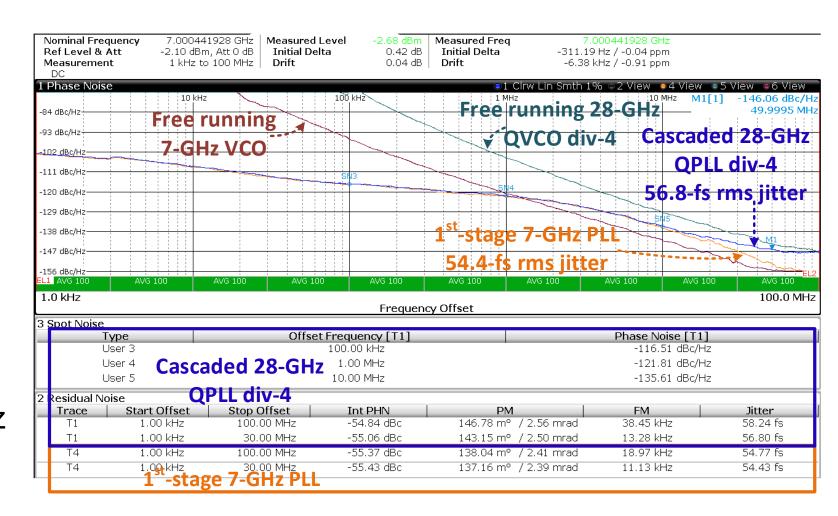

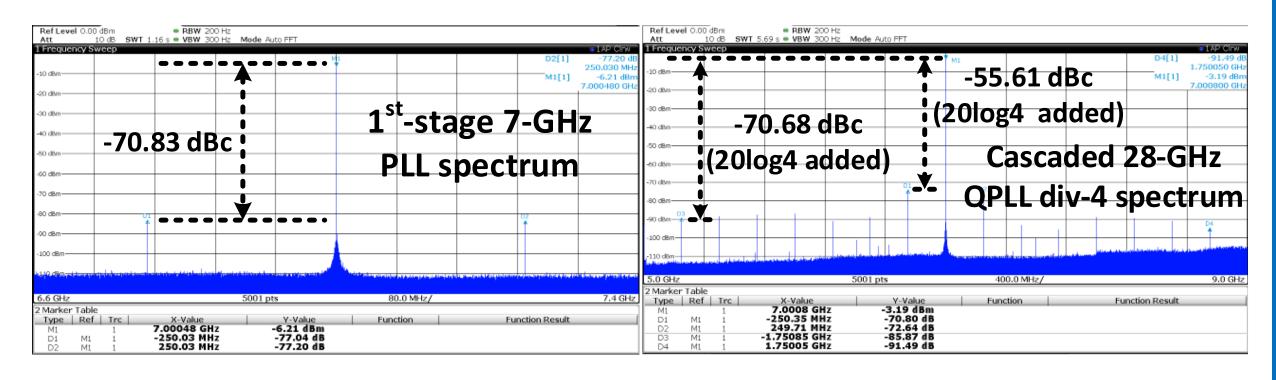

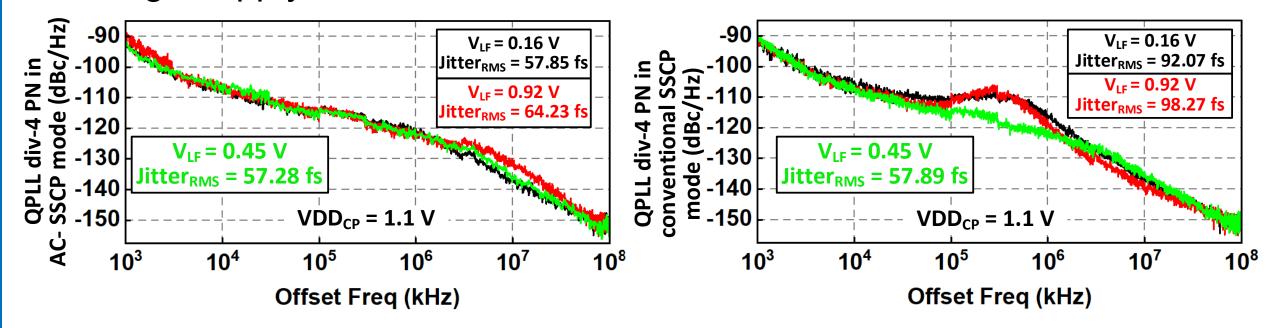

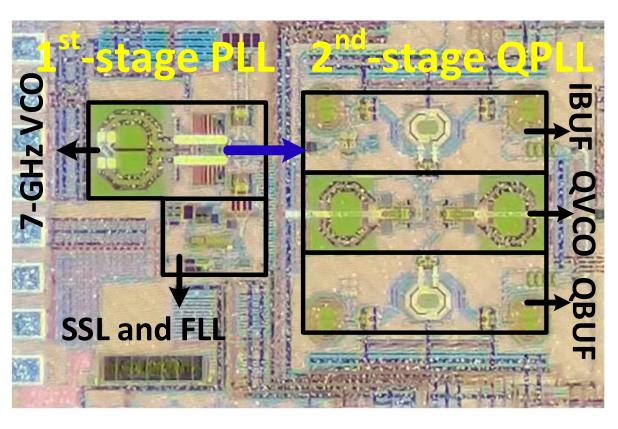

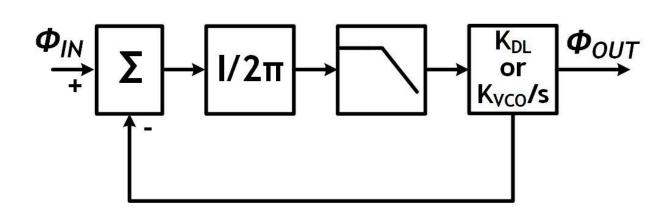

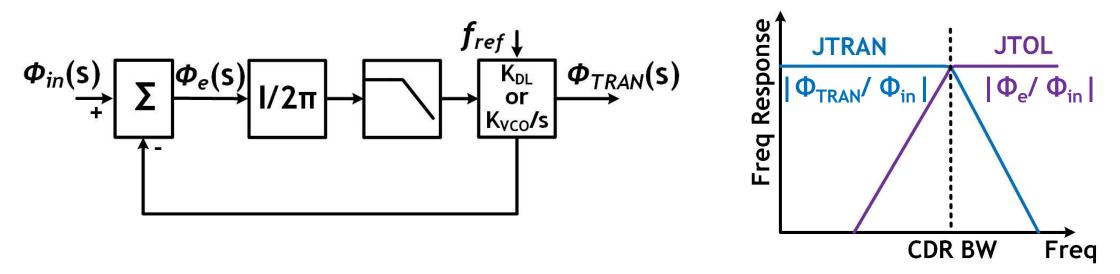

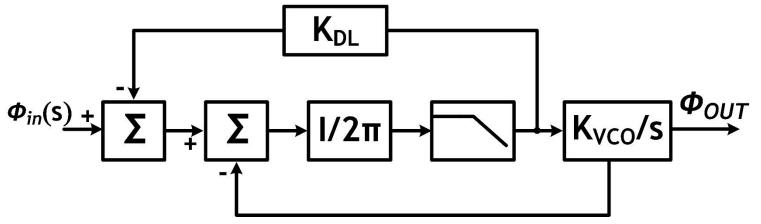

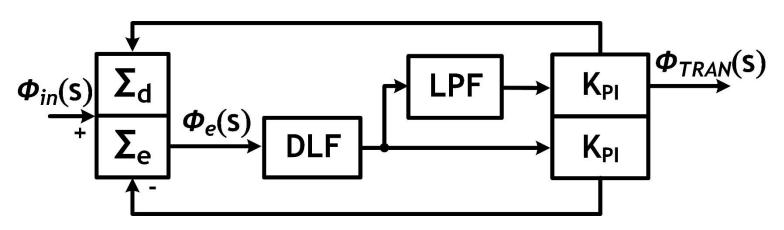

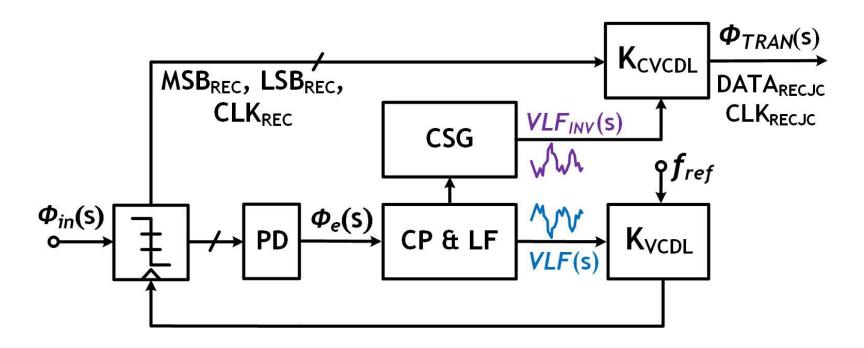

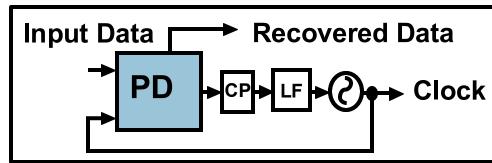

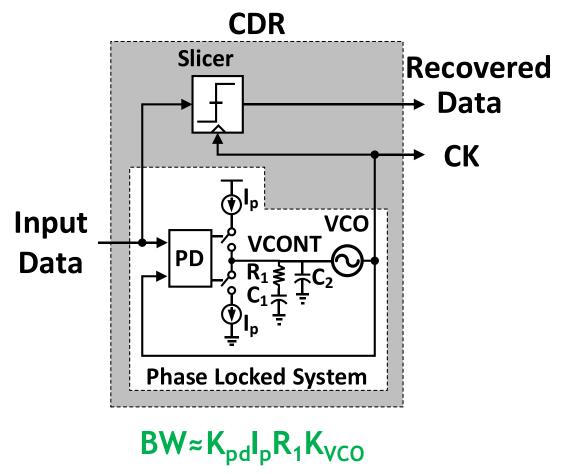

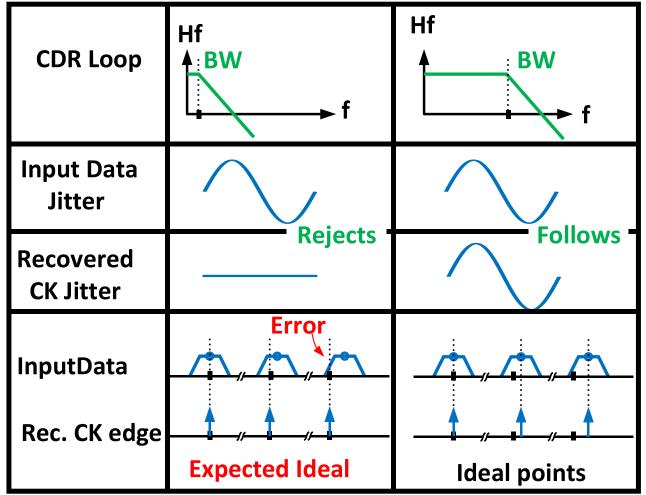

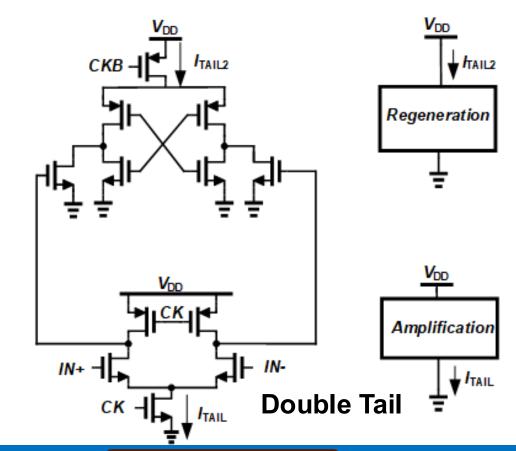

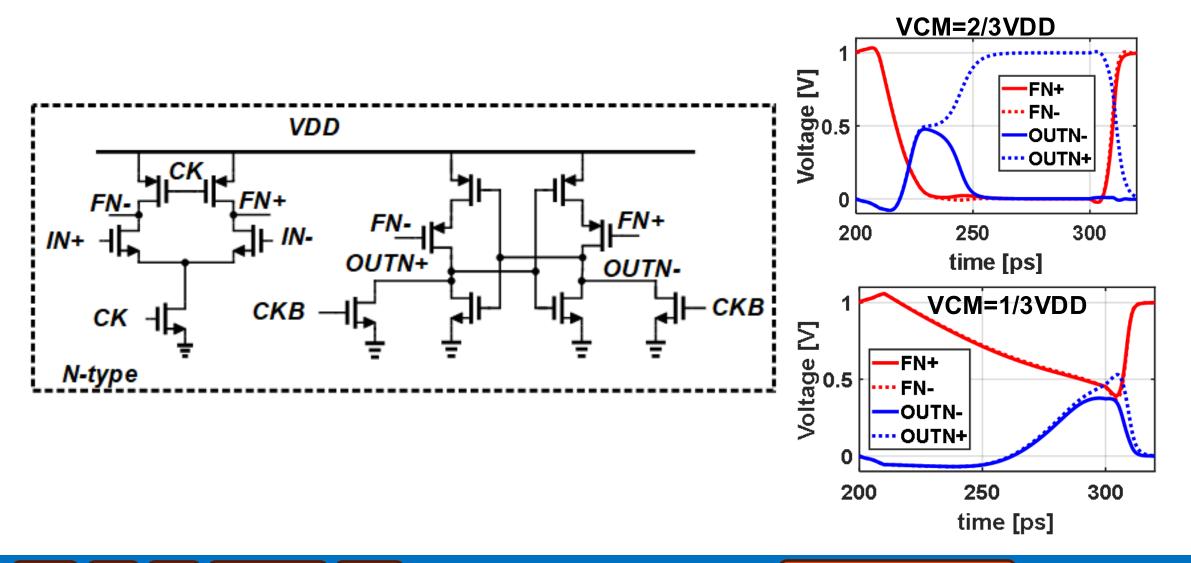

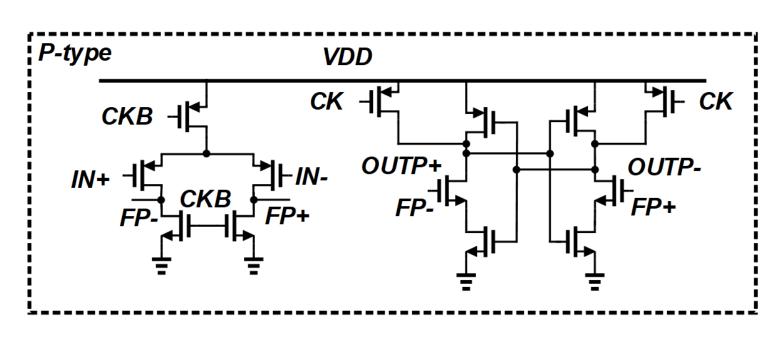

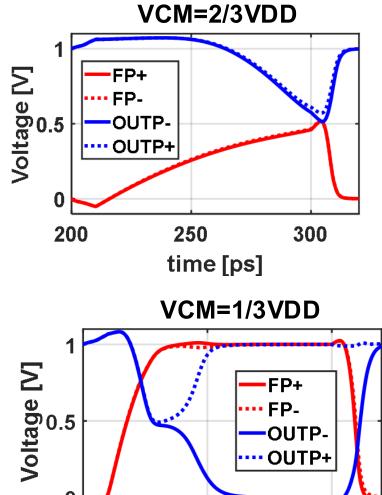

## Clock and Data Recovery and Clock Generation

- Architecture

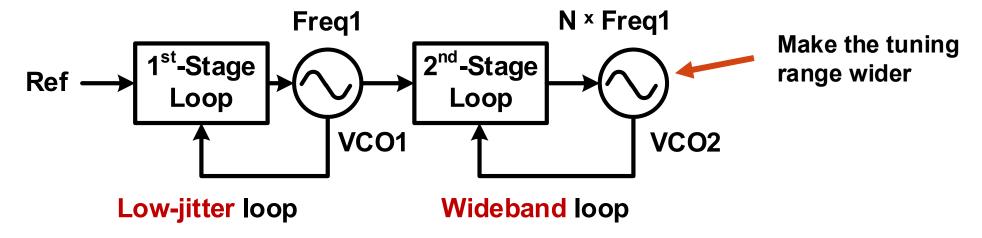

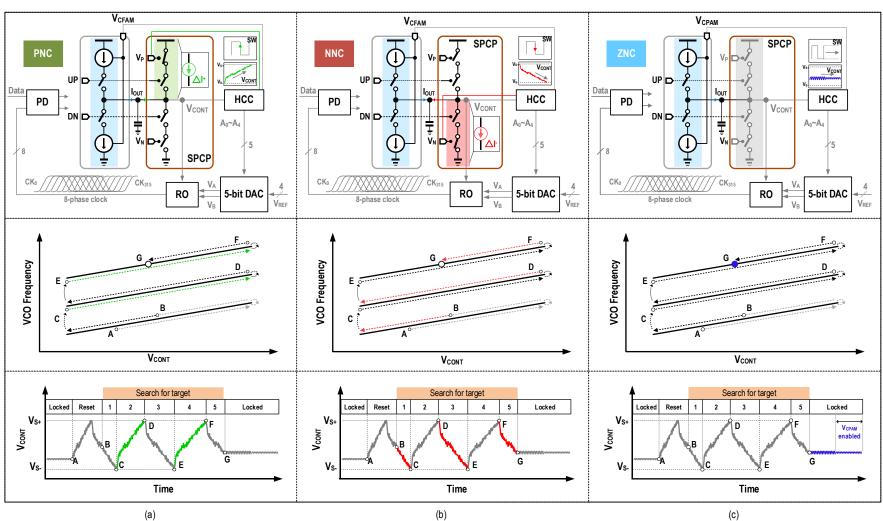

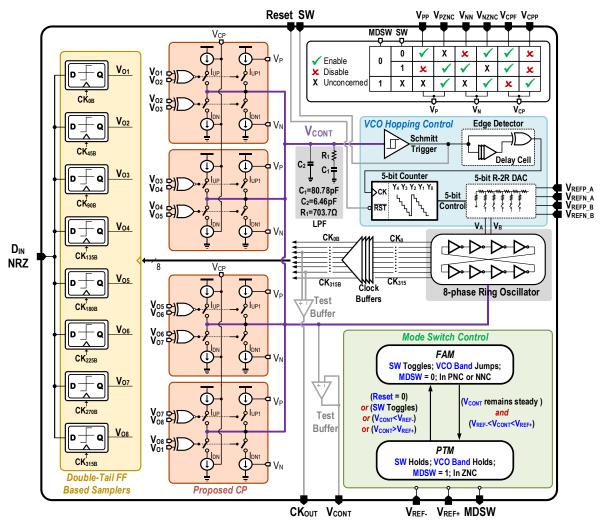

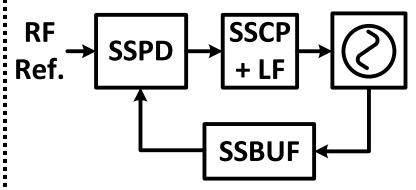

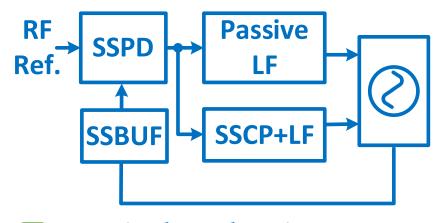

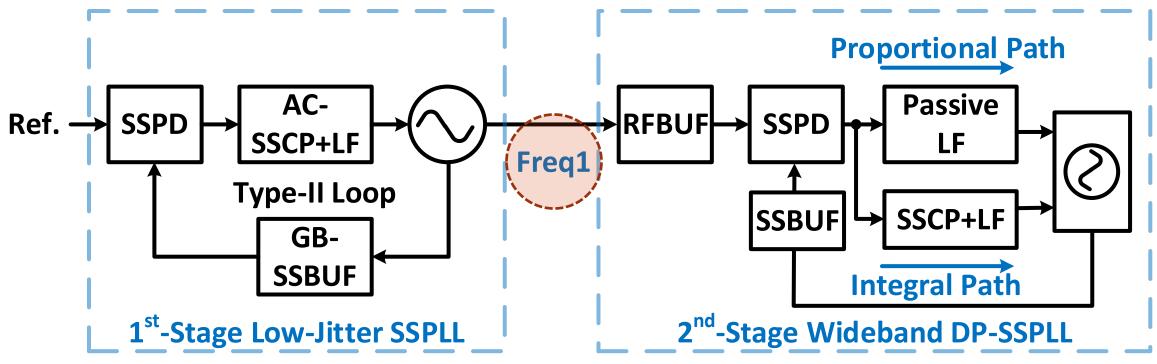

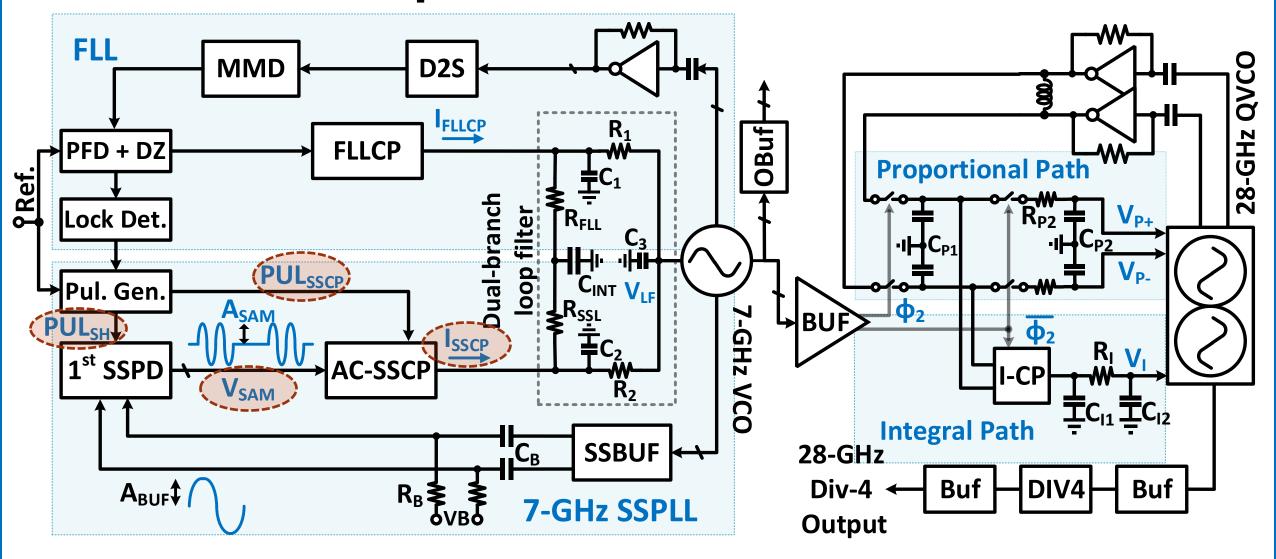

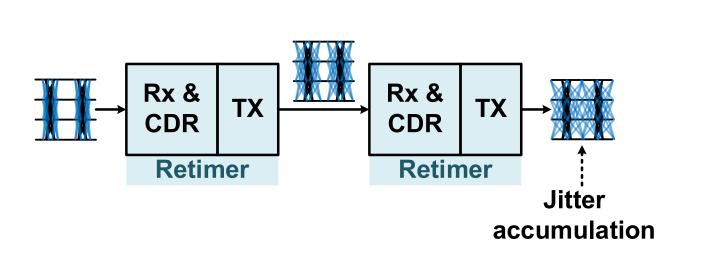

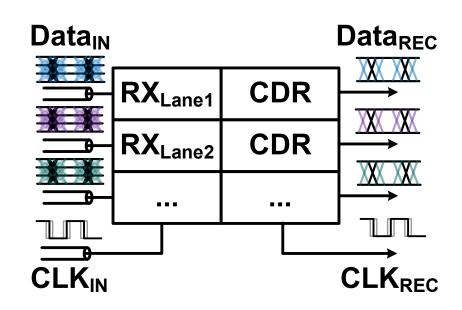

- Overview of CDR and PLL Loop Configuration

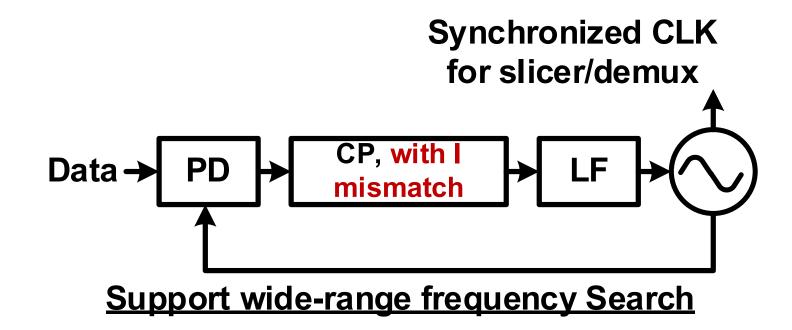

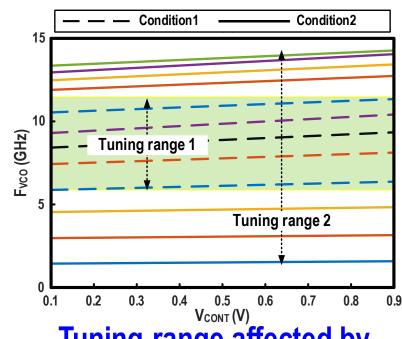

- Why Single Loop? How to Achieve Wide Capture Range Via Single Loop

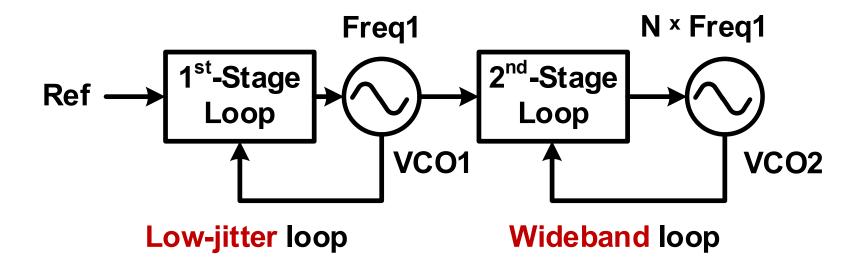

- Why Dual Loop? Cascaded or Parallel? How Loop Parameters Are Determined

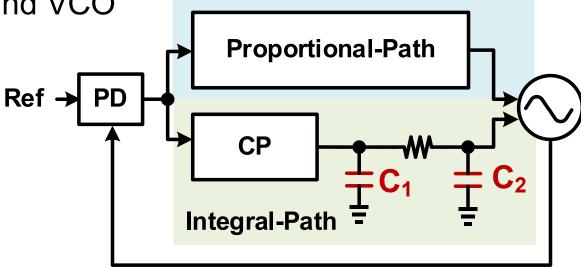

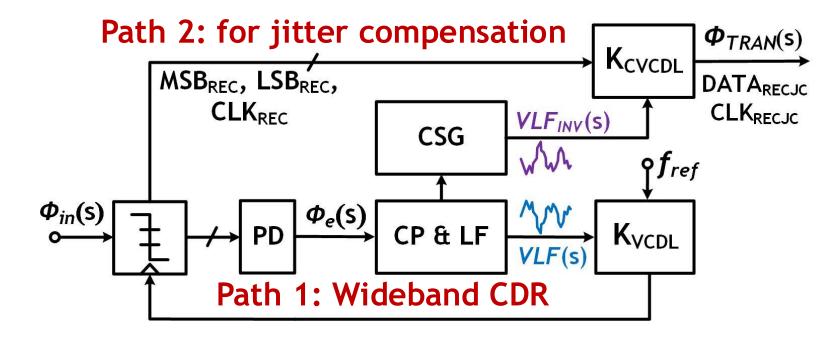

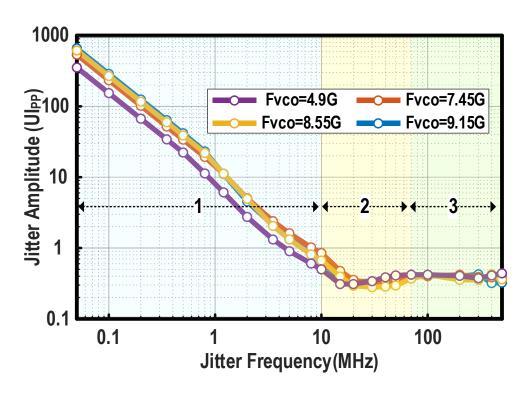

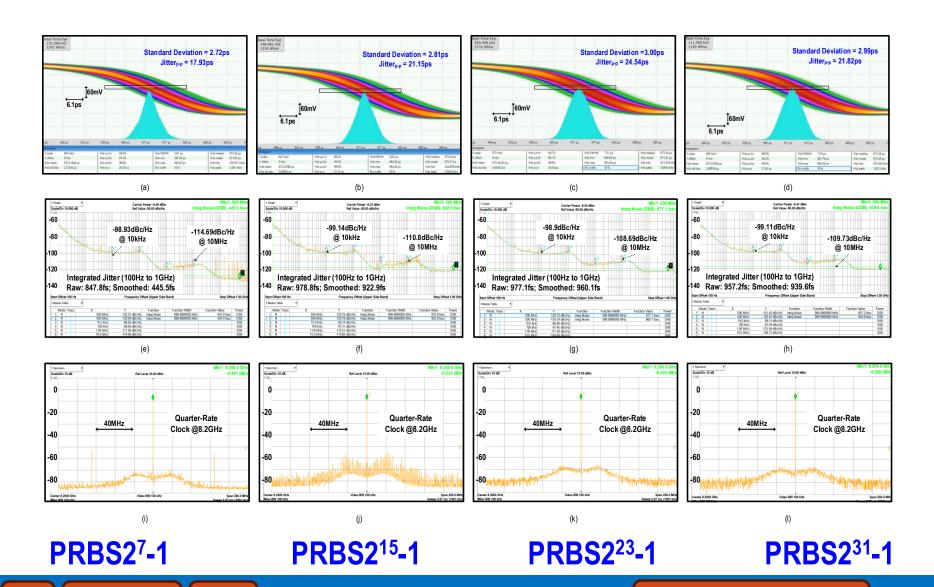

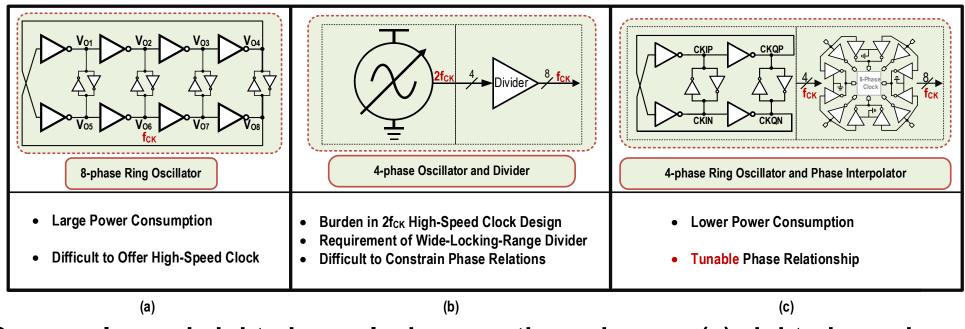

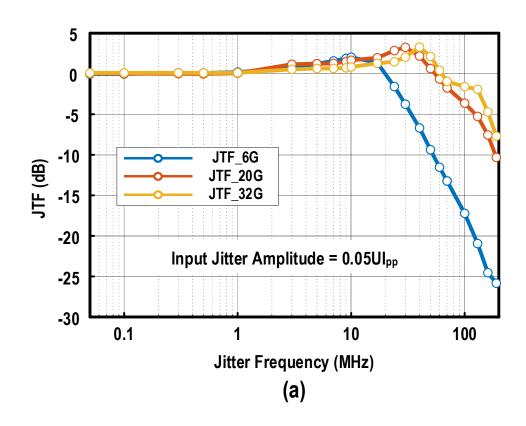

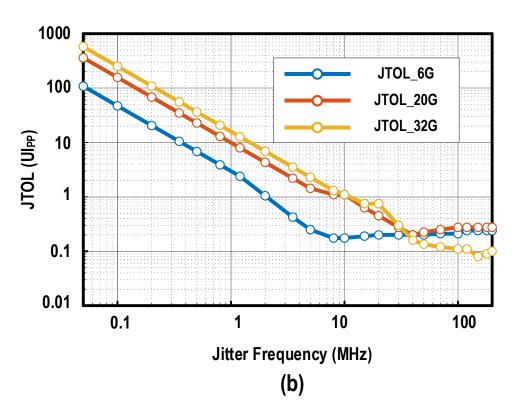

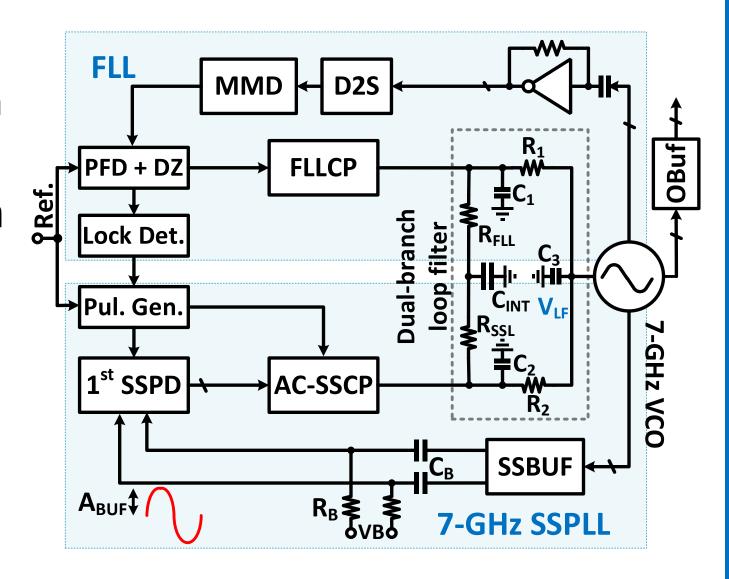

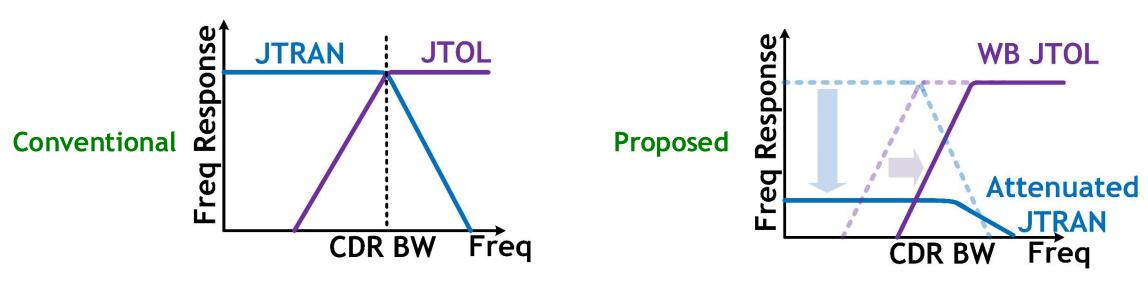

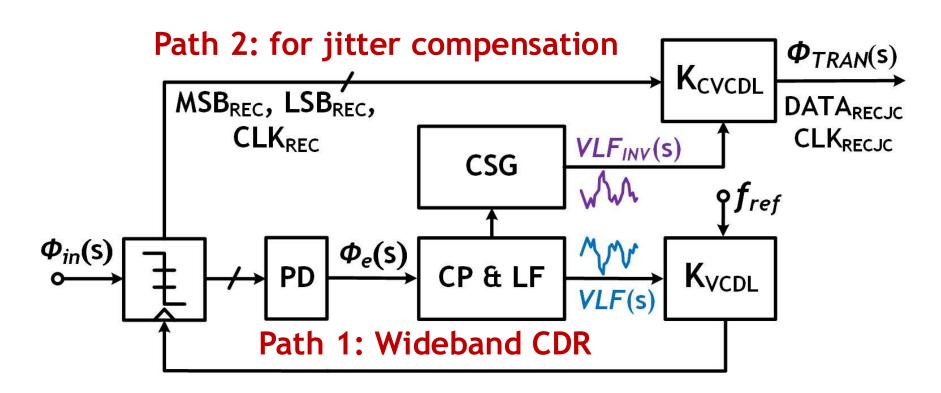

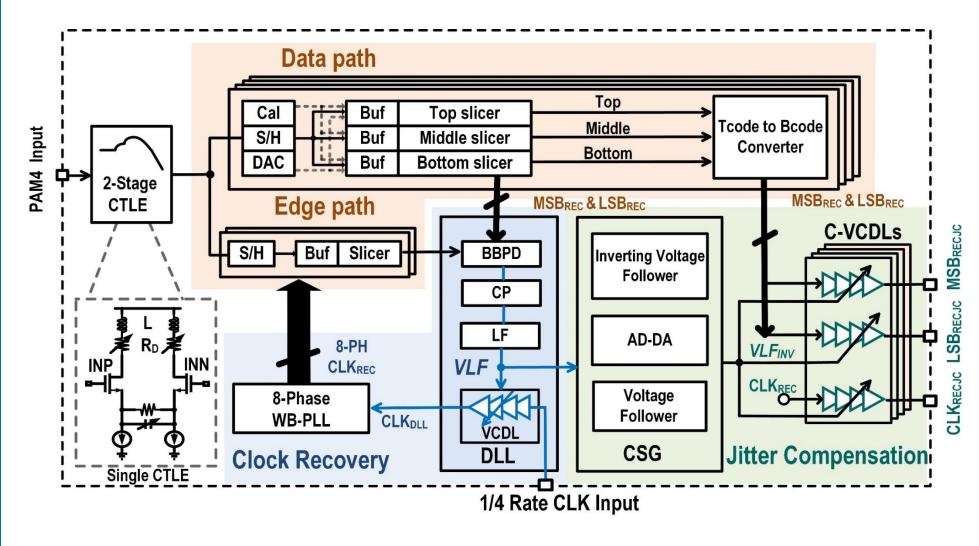

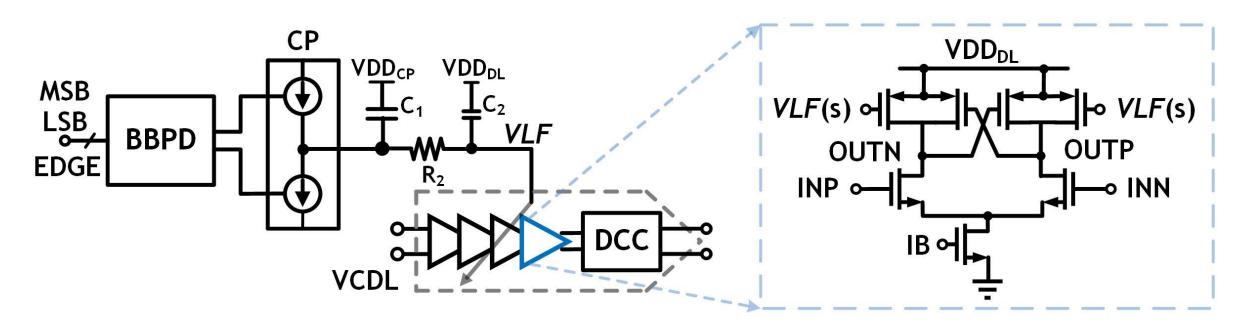

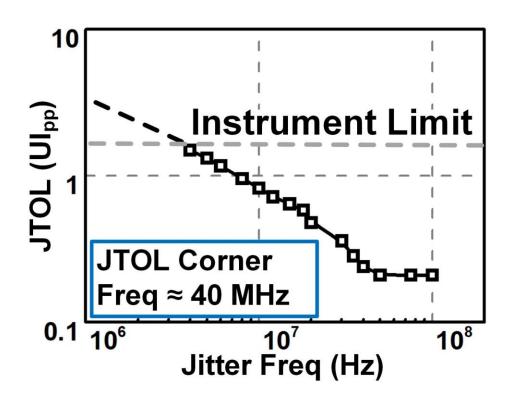

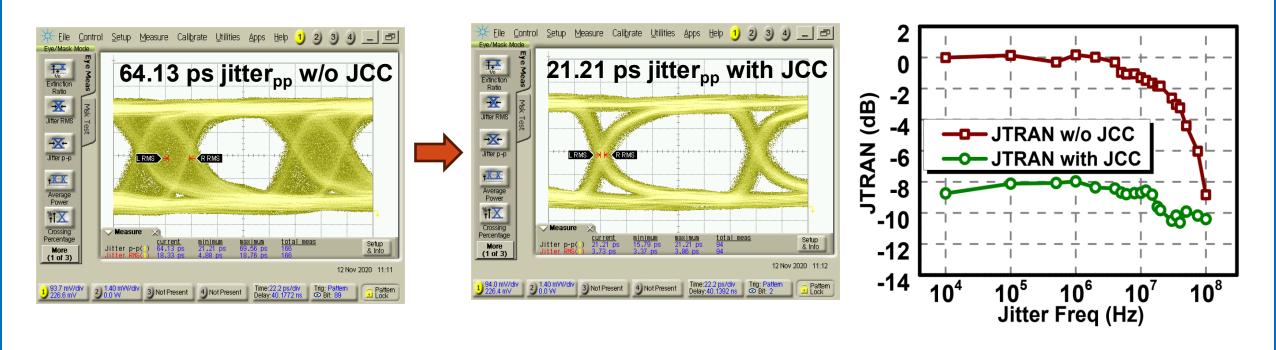

- Why Dual Path? Decoupling JTRAN and JTOL

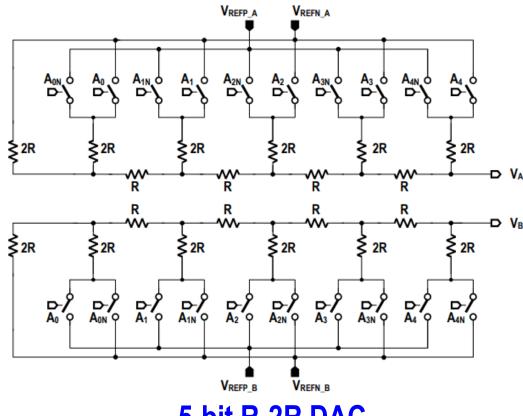

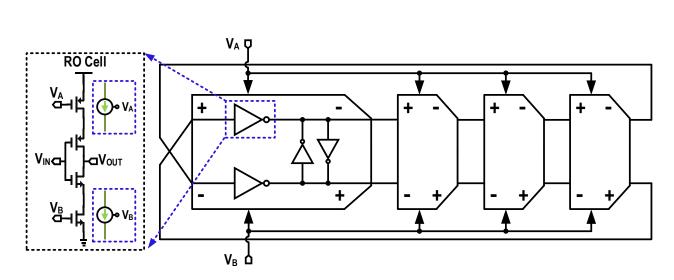

- Key Circuits

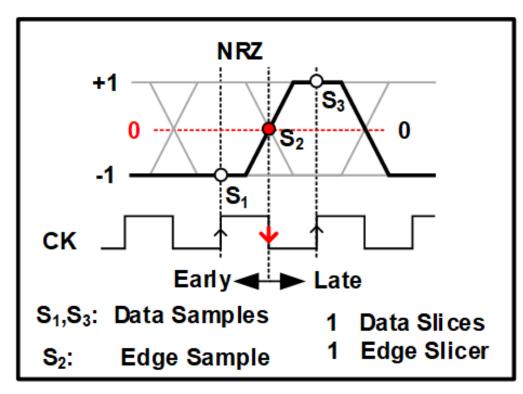

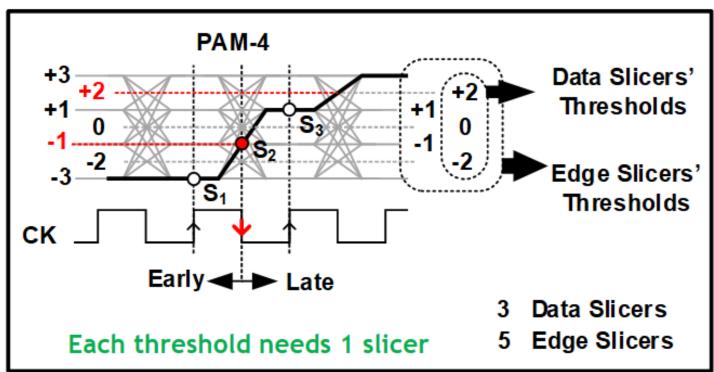

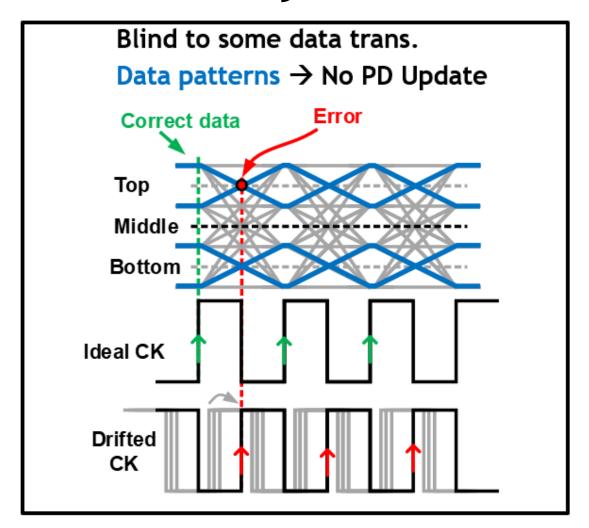

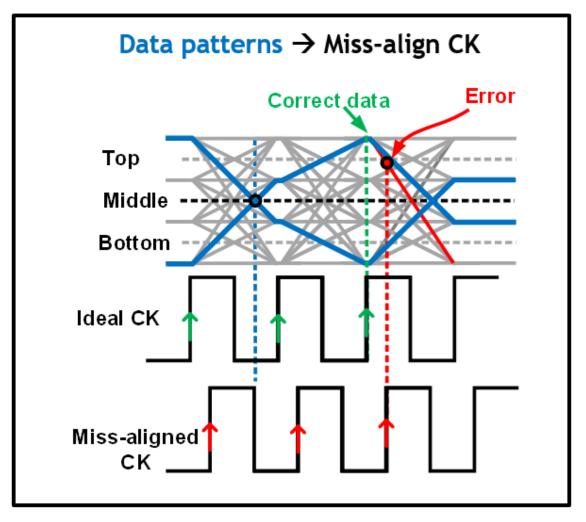

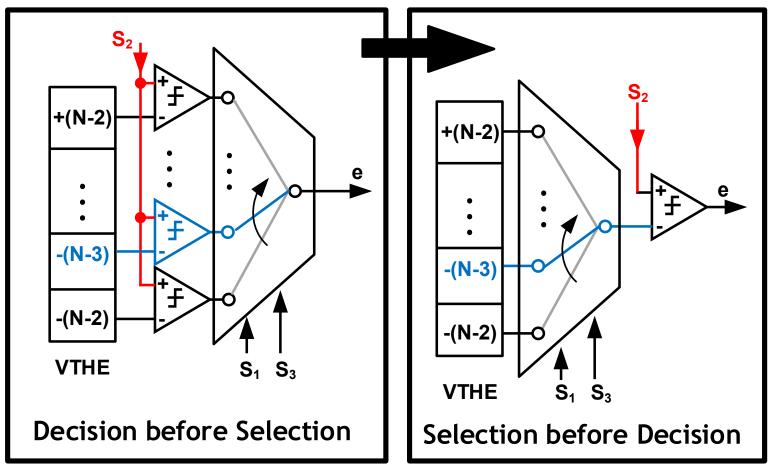

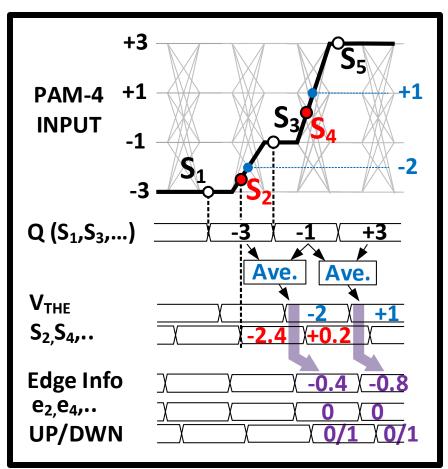

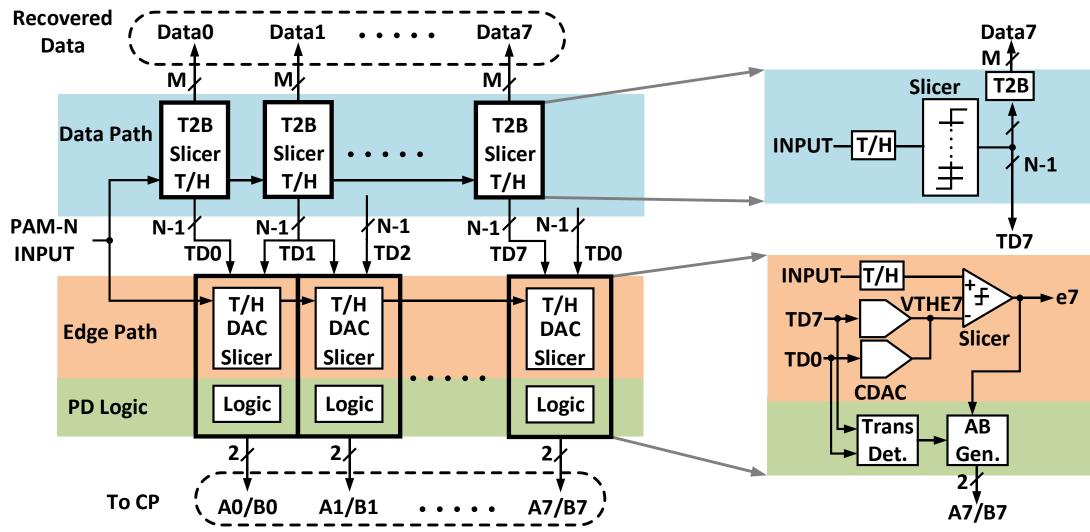

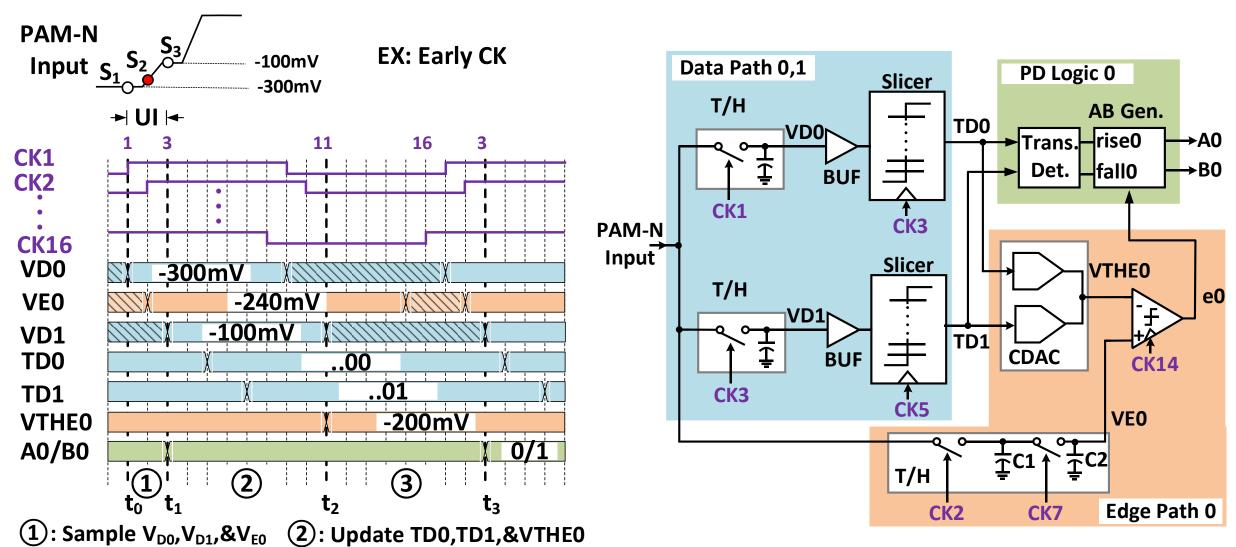

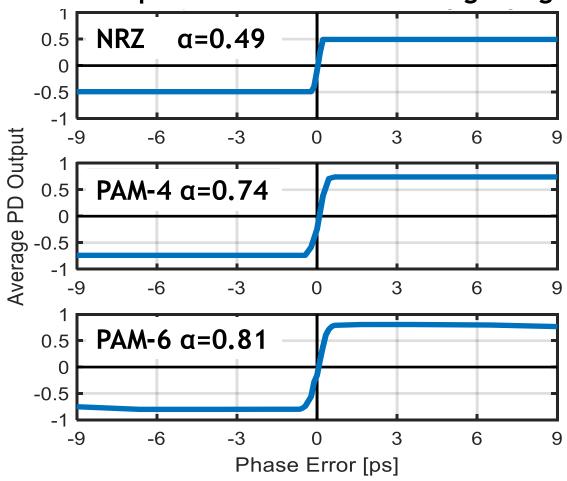

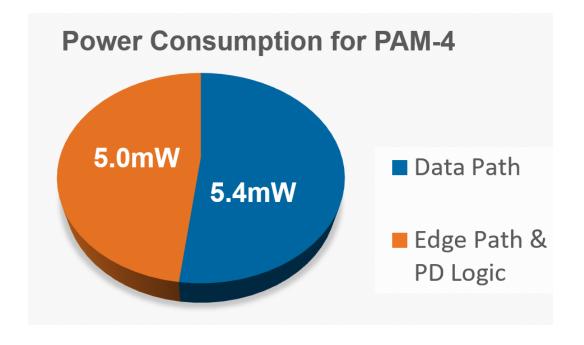

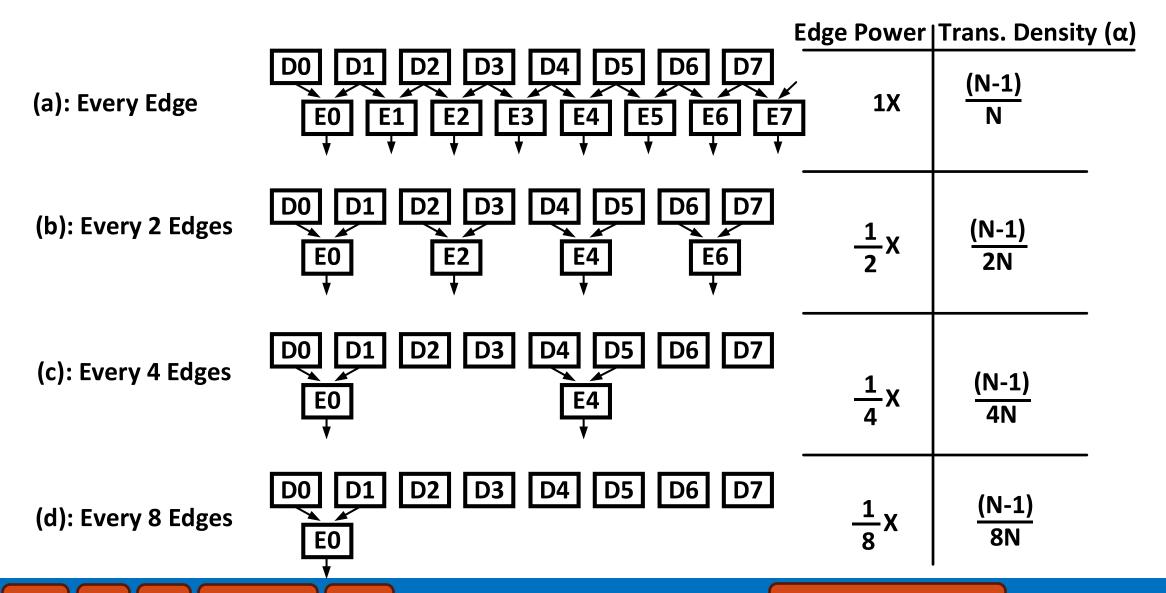

- PAM-n PD(Github: <u>Jabdekhoda (github.com)</u>)

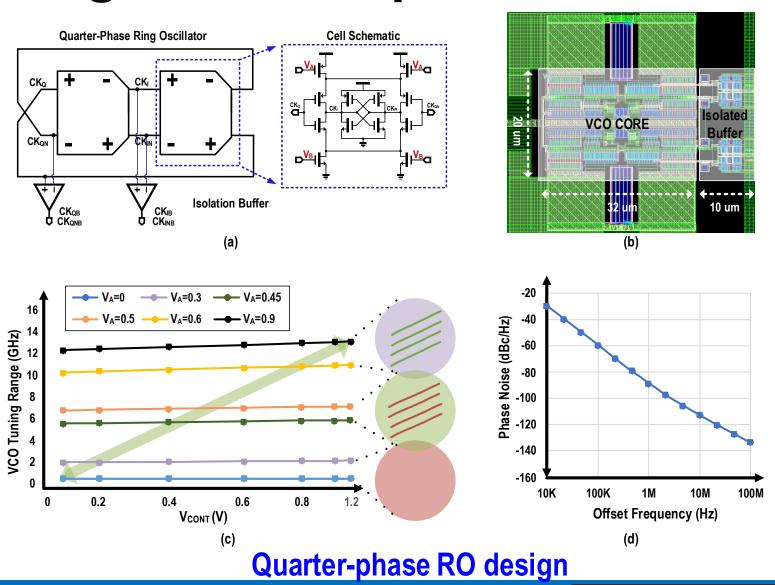

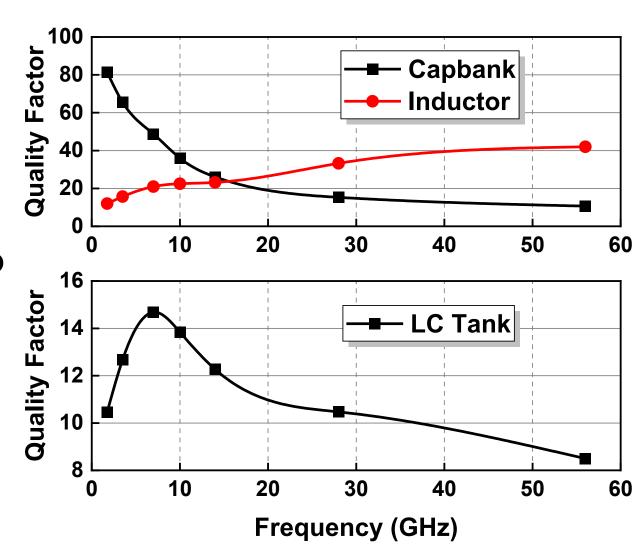

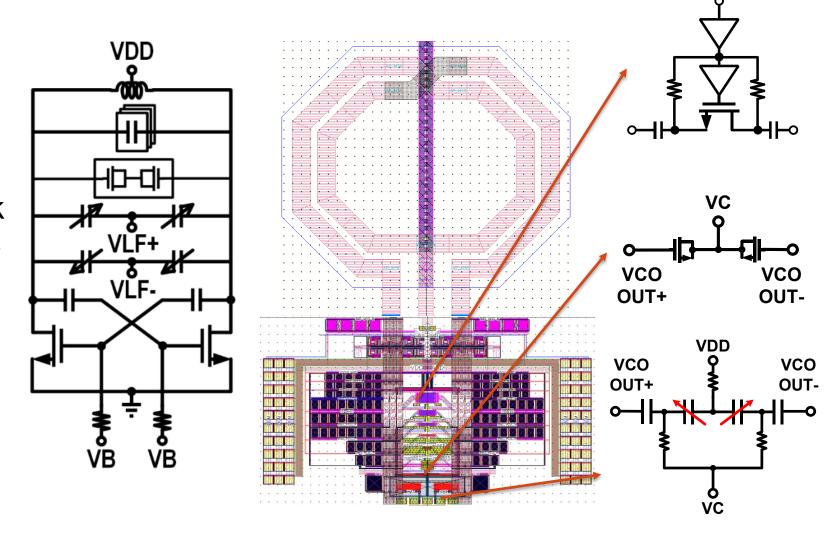

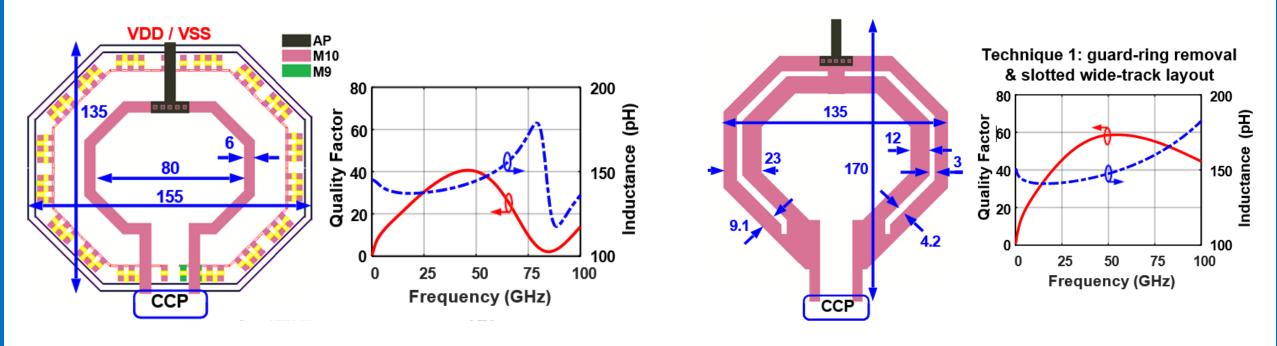

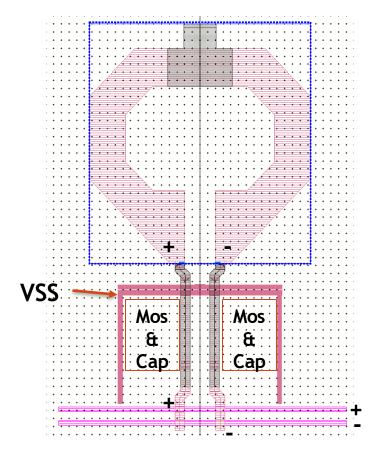

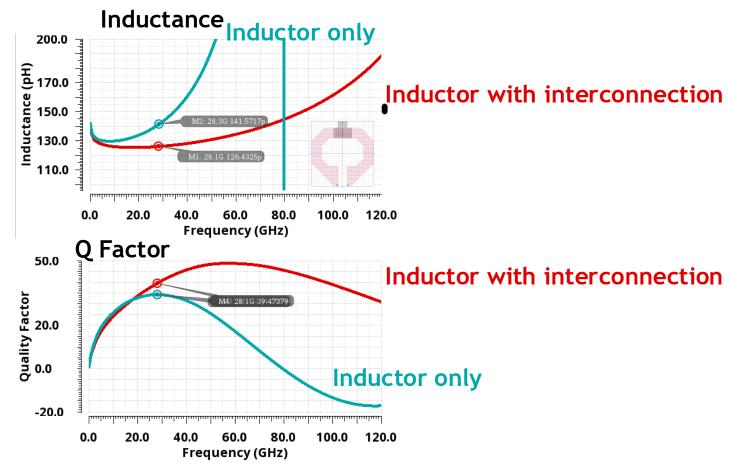

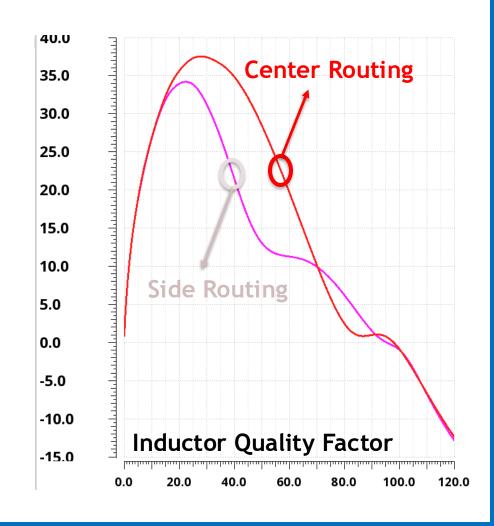

- VCO (Github: <a href="https://github.com/WANG-Li-lwangbk">https://github.com/WANG-Li-lwangbk</a>)

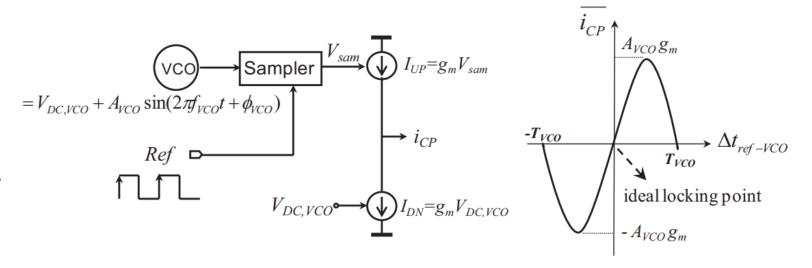

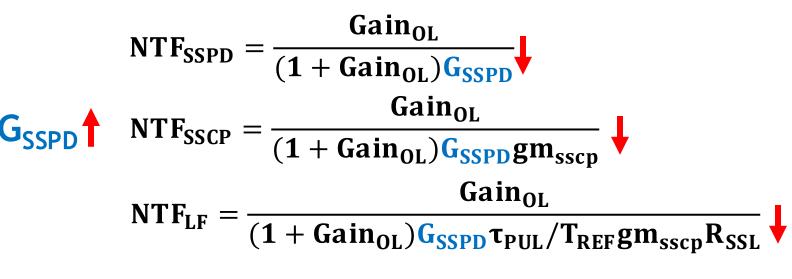

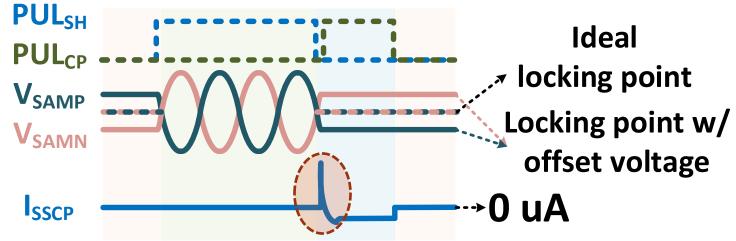

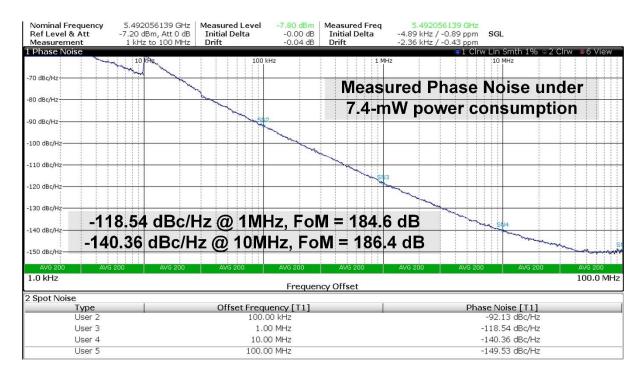

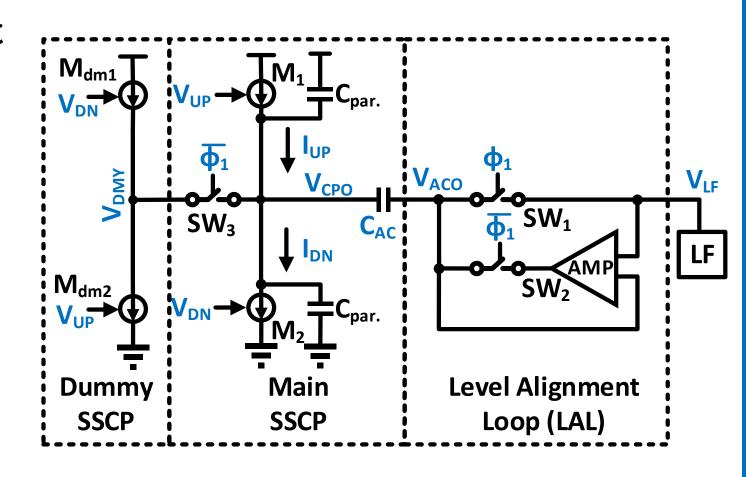

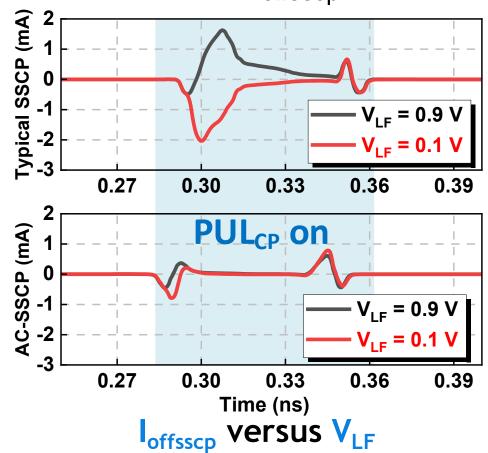

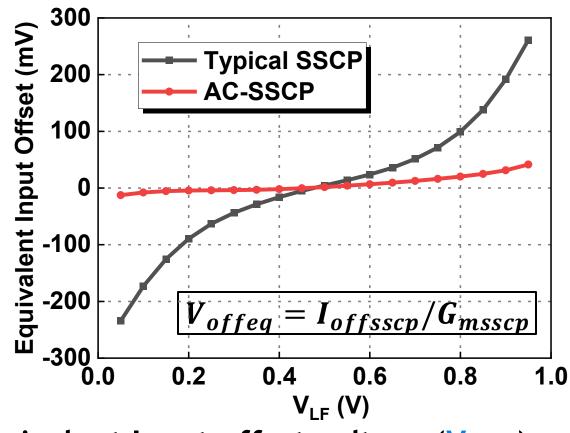

- AC-Coupled Sub-Sampling Charge Pump

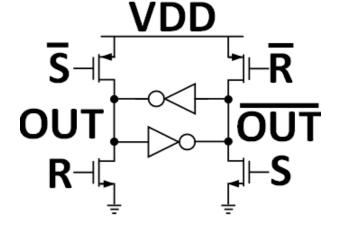

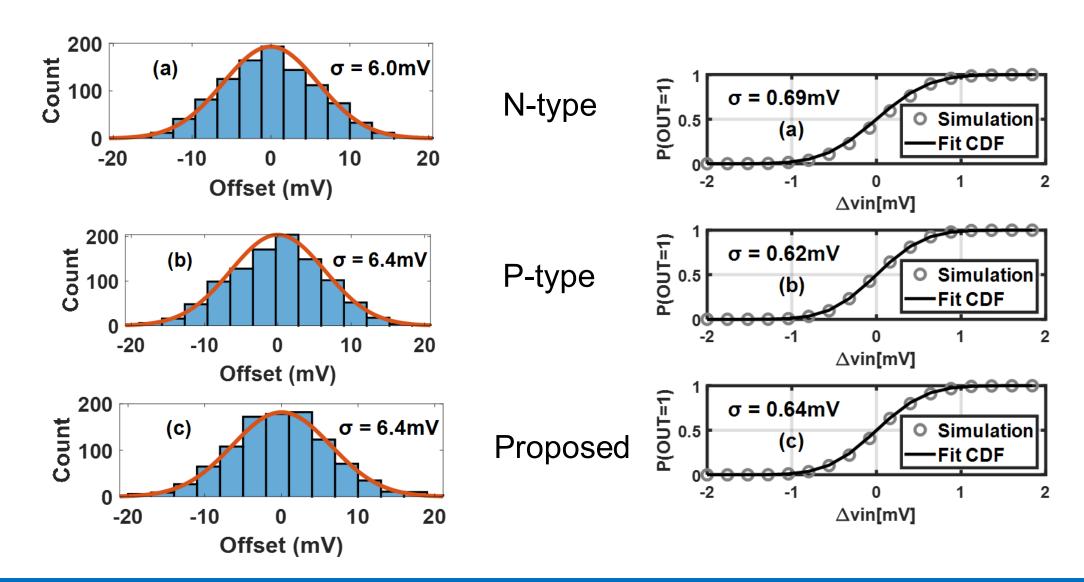

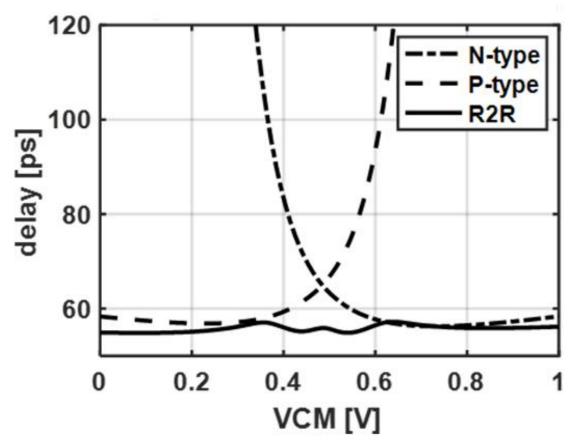

- R2R Comparator (Github: <u>Jabdekhoda (github.com</u>))

# Practical Implementation Techniques

- Motivation

- Practical Implementation Techniques

- Example 1

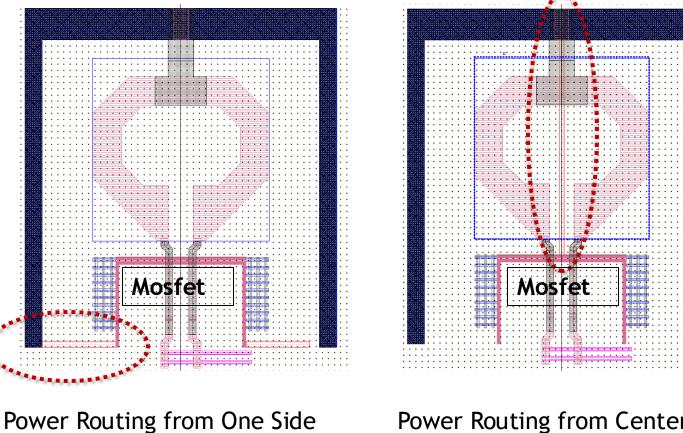

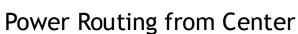

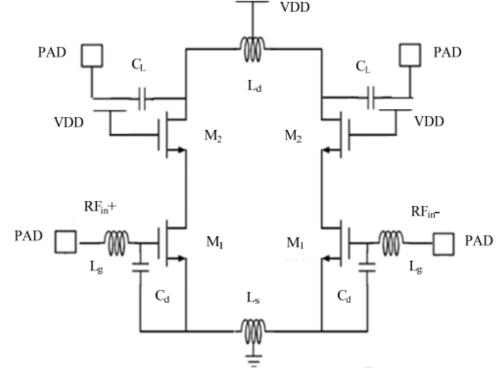

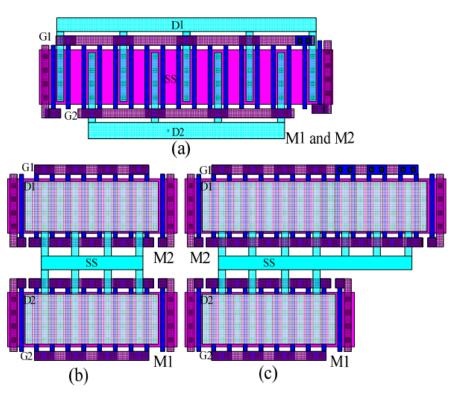

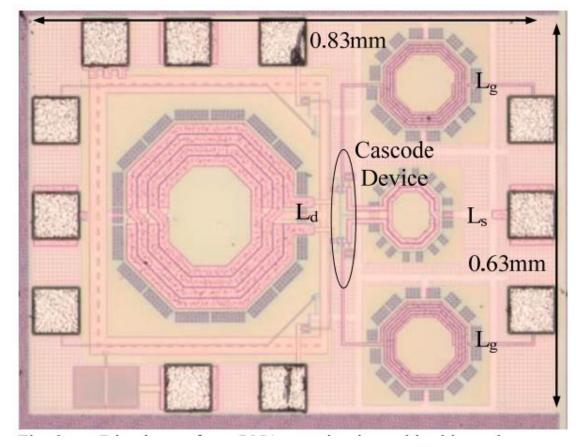

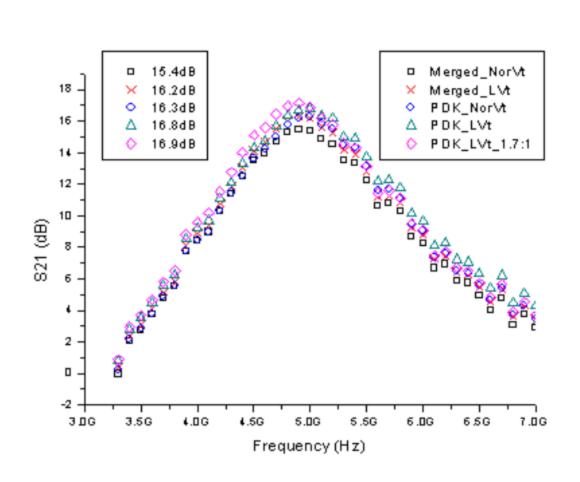

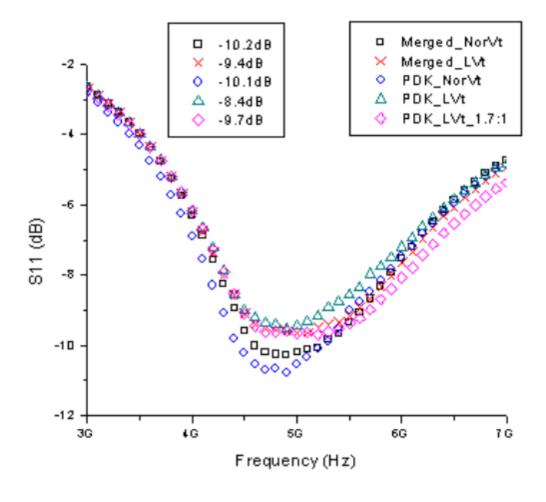

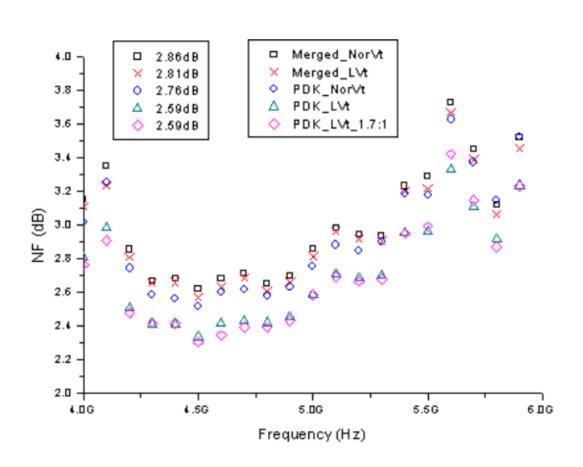

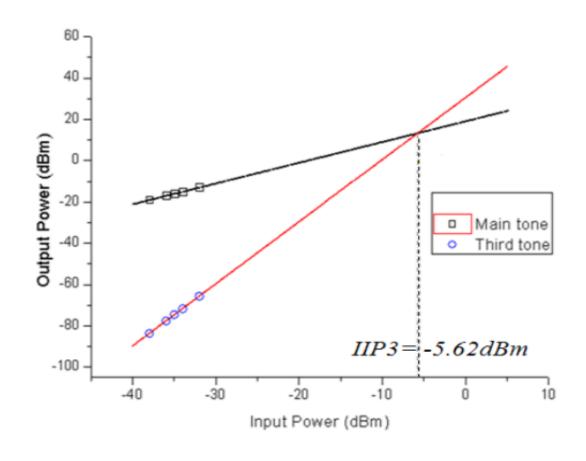

- A Performance Study of Layout and Vt Options for Low Noise Amplifier Design in 65-nm CMOS [RFIC'12]

- Example 2

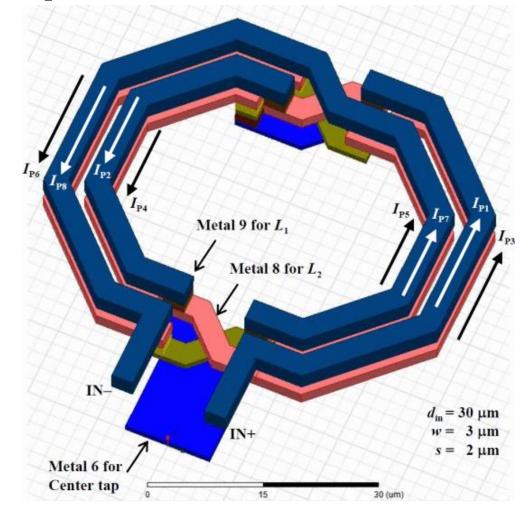

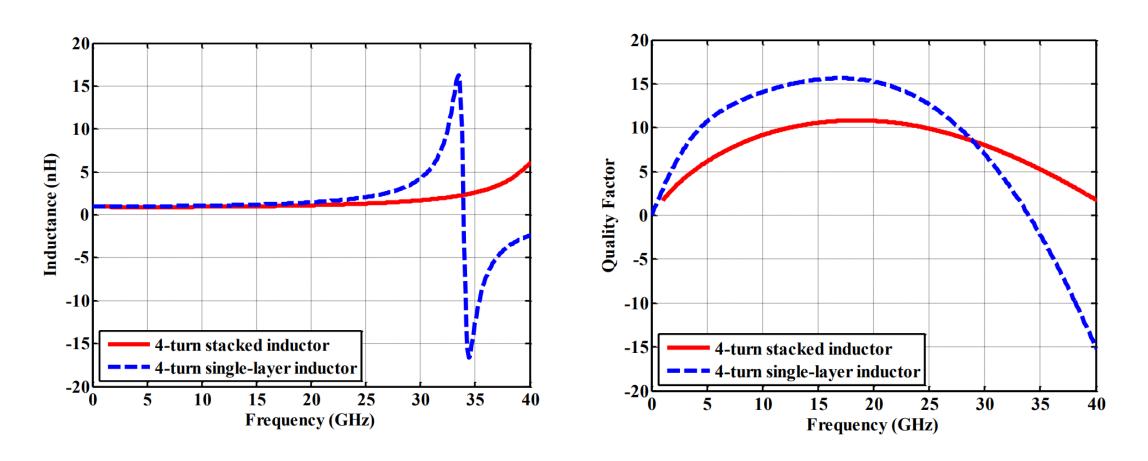

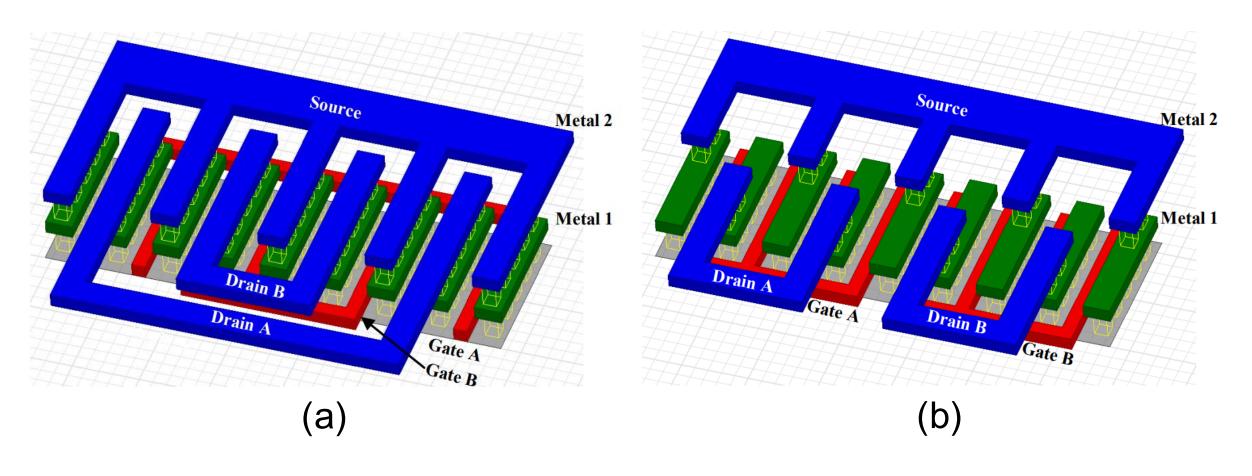

- Differential Stacked Spiral Inductor and Transistor Layout Designs for Broadband High-Speed Circuits [RFIT'14]

- Example 3

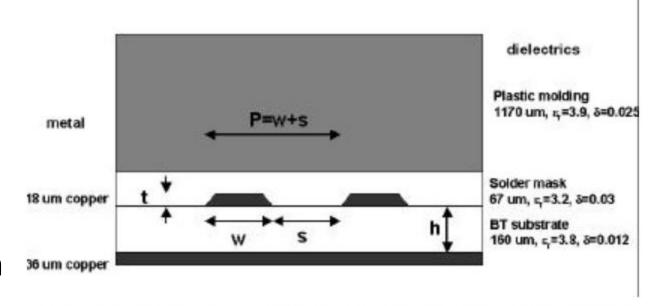

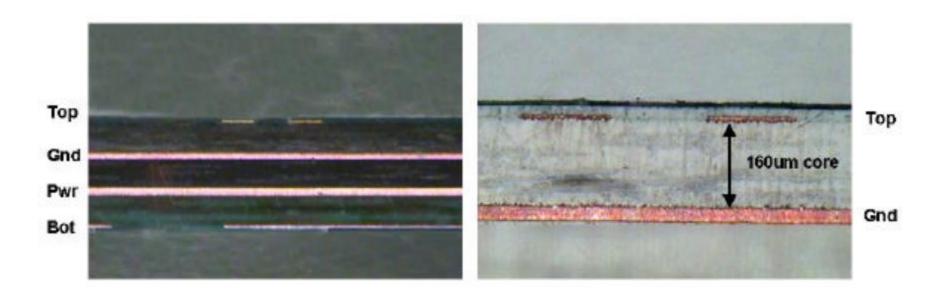

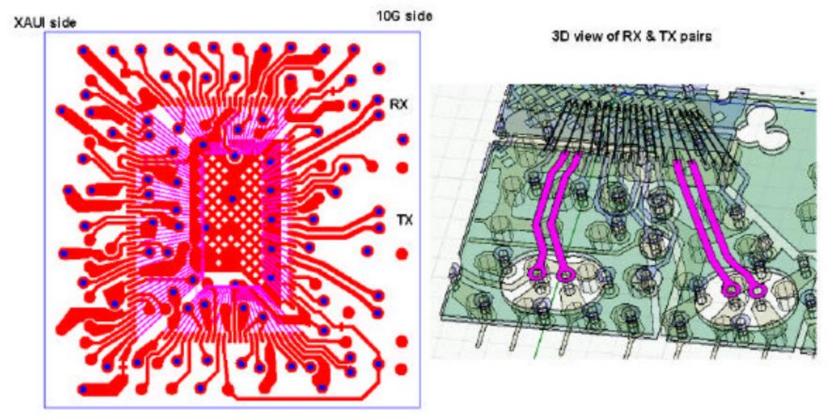

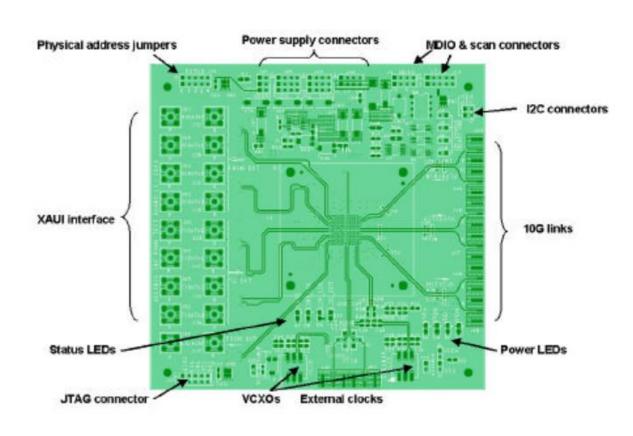

- Package Design for a 10 Gigabit Ethernet Transceiver [DesignCon'2004]

- Conclusion

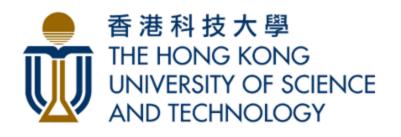

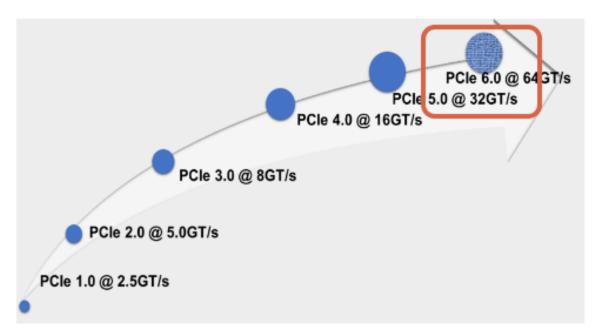

# Background of Wireline and Optical Links 有线和光通信链路的研究背景

Prof. C. Patrick Yue 俞捷教授

芯动力人才计划®第 125 期国际名家讲堂

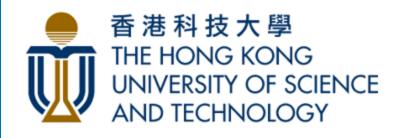

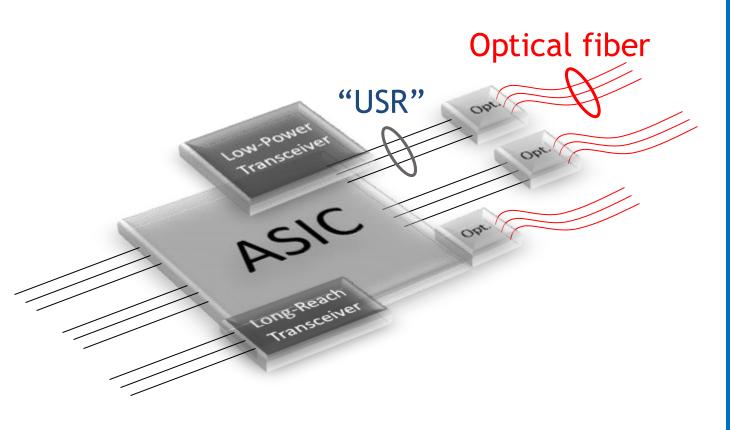

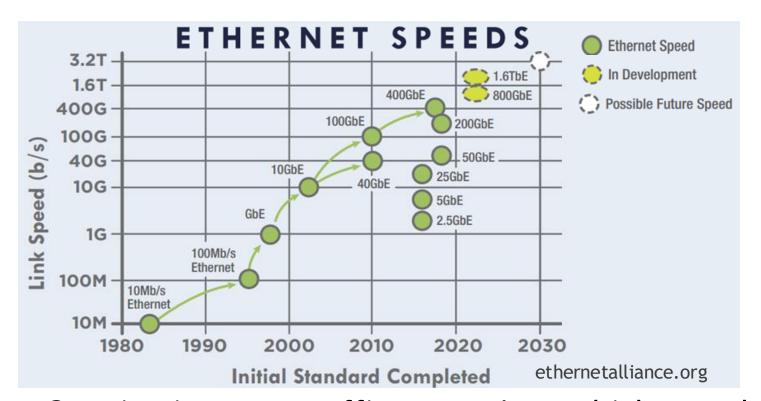

#### Wireline Link for Next Generation Ethernet

Motivation: Energy efficient high-speed data communication

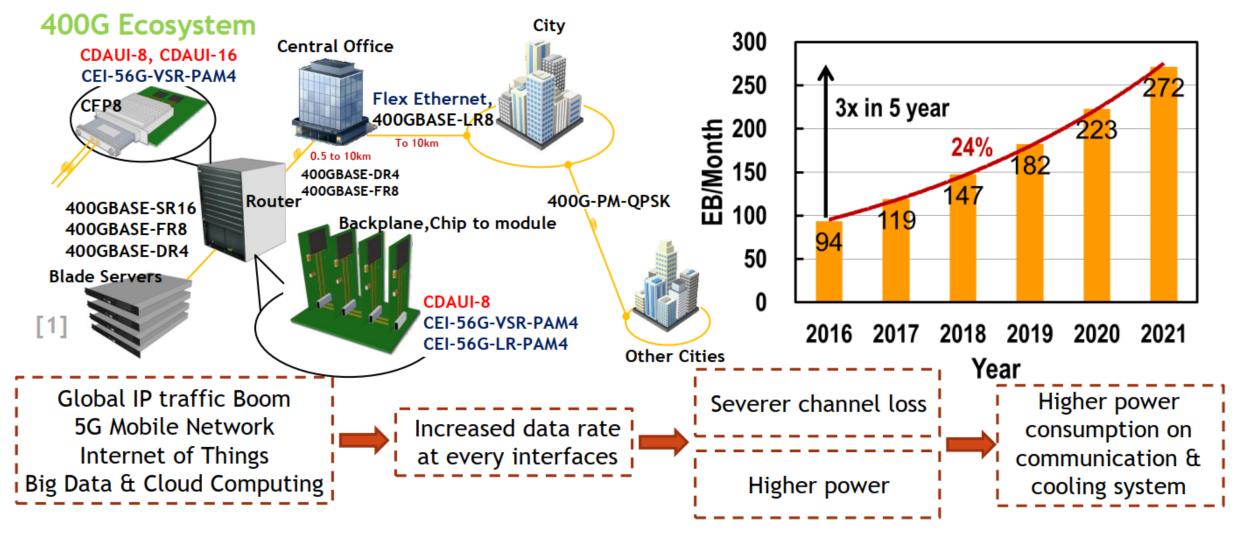

# **Optical Interconnections for 5G Network**

- Optical links for long-distance inter data center communication

- Recently, optical I/O is also evolving towards short-reach and even with package communications

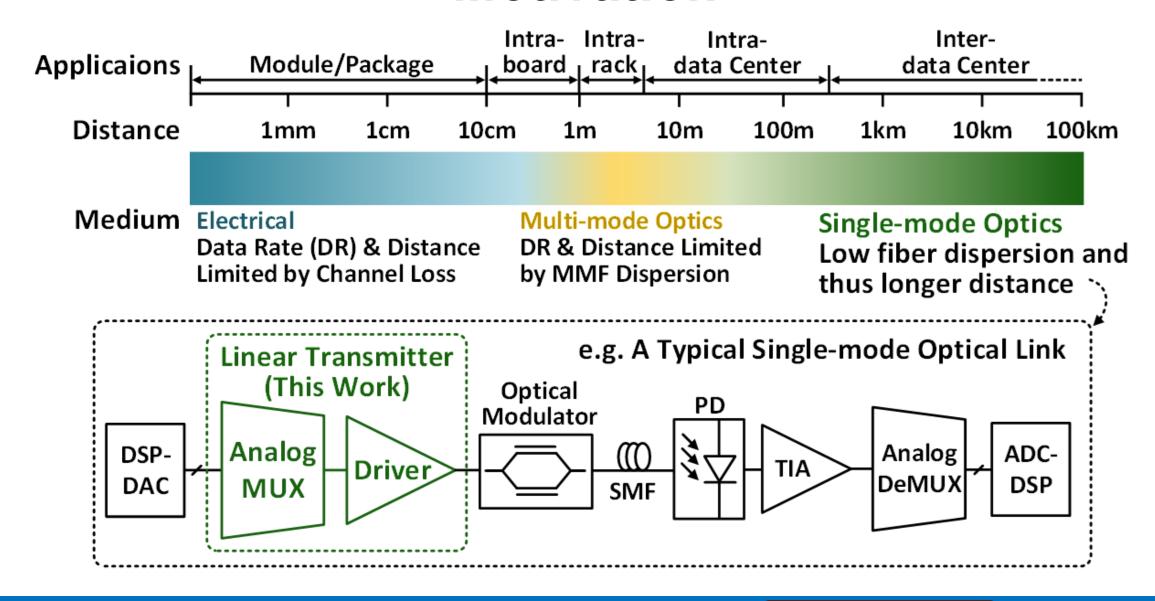

### VCSEL and Silicon-Photonic Optical Transmitter

Multi-mode optics (e.g., VCSEL)

**Electrical**

Single-mode optics (e.g., MRM)

|                                          | Data Rate | <b>Ethernet Standard</b> | Channels | Modulation Scheme      |

|------------------------------------------|-----------|--------------------------|----------|------------------------|

| VCSEL                                    | 400G      | 400GBASE-SR8             | 8        | 25Gbps NRZ             |

|                                          | 400G      | 400GBASE-SR8             | 8        | 50Gbps PAM-4           |

| Single-mode<br>optics, e.g.<br>Si-PH MRM | 400G      | 400GBASE-PSM16           | 16       | 25Gbps-λ: NRZ          |

|                                          | 400G      | 400GBASE-PSM8            | 8        | 50Gbps-λ: NRZ or PAM-4 |

# **Beyond Optical and Wireline**

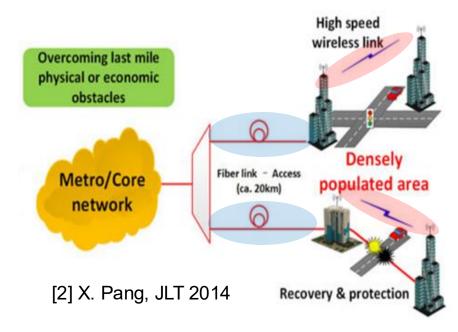

Fiber-Wireless Network

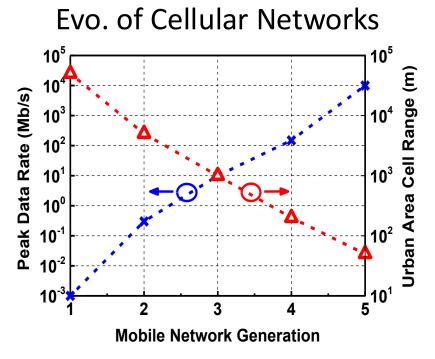

#### Fiber-Wireless Network

- 5G mobile network requires ultra-dense cellular cells

- Backhaul links deployment is challenging

- Fiber-wireless networks provide high performance and flexible backhaul link connections

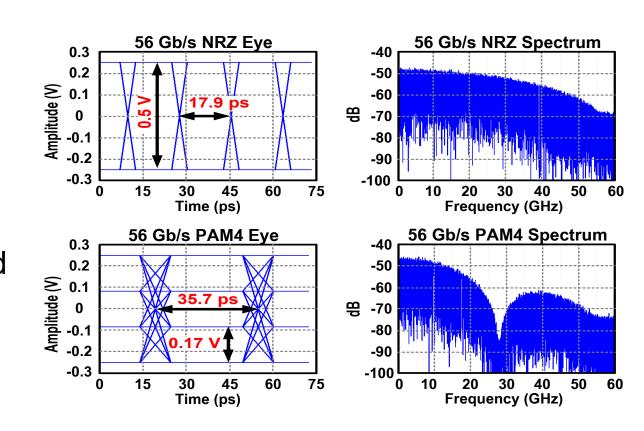

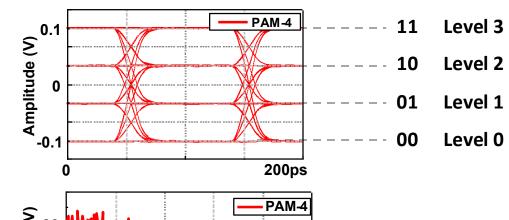

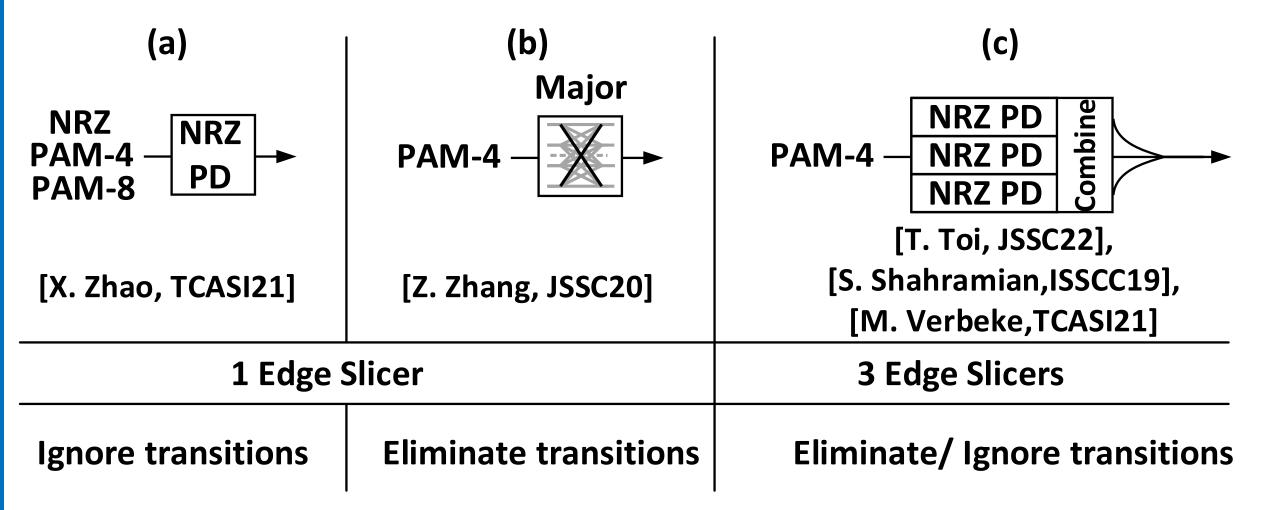

#### Wireline Rx: PAM4 vs. NRZ

- PAM4 Rx trades SNR for time/frequency efficiency

- PAM4 Rx meets new design issues

- PAM4-to-NRZ decoding for DSP

- CDR and equalizer with complicated data levels/transitions

#### **Modern Wireline Transceivers**

- Low-power across a wide range of channel losses for copper interconnect

- Transceivers for optical modules focusing on low-cost and low-power

- Relatively simple 2-PAM and 4-PAM modulation with linear and/or decision-feedback equalization

- Forward error control coding

# Paving the Way to 200Gb/s Transceivers

- Optical Transceivers that are Compact and Co-Optimized

- Modulation and Coding with Increasingly Co-Optimized **DSP** for Long-Reach **Transceivers**

- Extremely Short and Within-Package Transceivers Focusing on Low Power

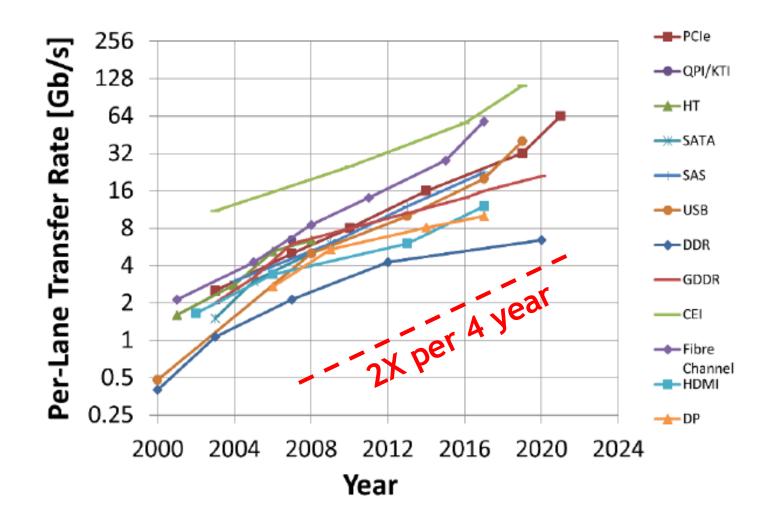

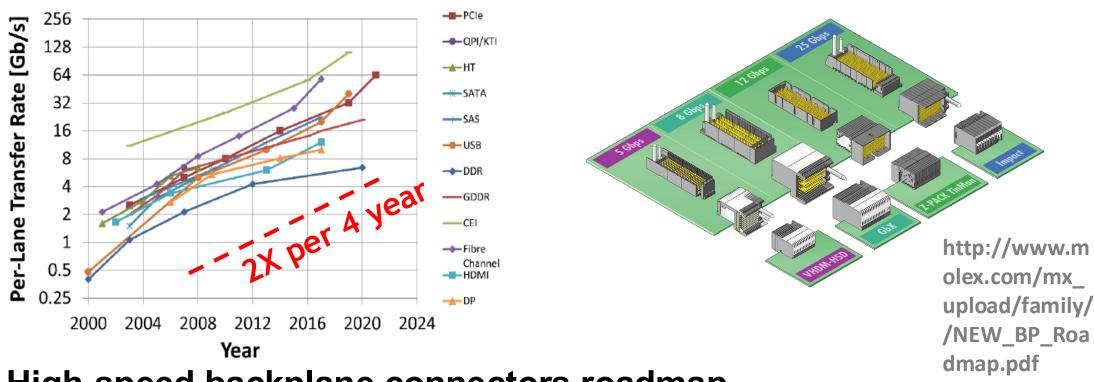

#### Trend: Per-Lane Data Rate Growth vs. Year

Data-rate per pin has approximately doubled every four years across various I/O standards ranging from DDR, to graphics, to high-speed Ethernet.

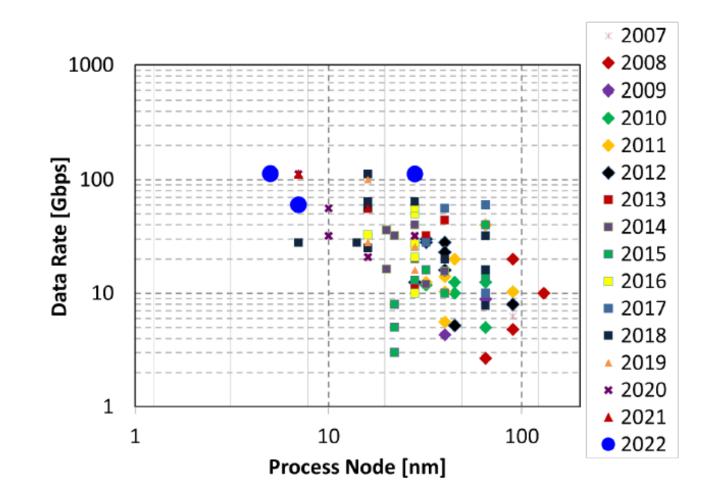

#### Trend: Data Rate vs. Process Node

PAM4 transceivers have kept pace at 56Gb/s and 112Gb/s while taking advantage of CMOS scaling down to 5 nm for more aggressive channel loss compensation

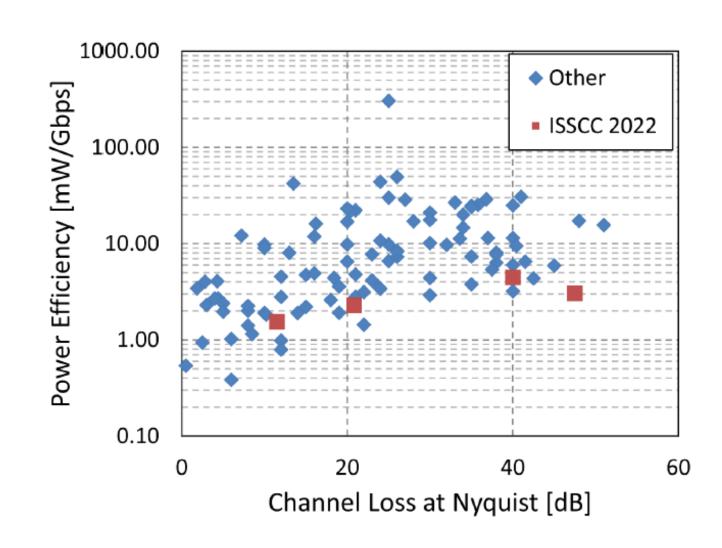

# Trends: Bit Efficiency vs. Channel Loss

- Channel loss compensation by different equalization techniques

- Power efficiency better than ~1-2 pJ/bit only for Short Reach with < 20 dB loss</li>

- Power efficiency ~5-10

pJ/bit for Long Reach with up to 50 dB loss

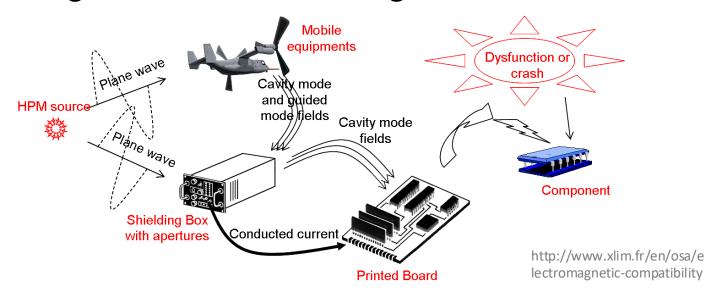

#### **EMI Issues in Advanced Data Center**

Most electronics generate electromagnetic emission

- Electromagnetic interference (EMI) causes malfunction of the victim electronics

- How to solve?

- Keep enough distance, be robust, and keep quiet

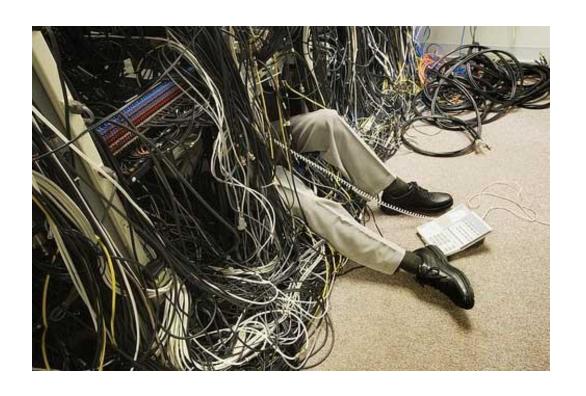

#### **EMI Issues in Advanced Data Center**

- Front-side haven, but back-side disaster

- Thousands of paralleled communication modules

- Data rate of each module > 10 Gbps

- Complicated electromagnetic environment

#### **EMI Issues in Advanced Data Center**

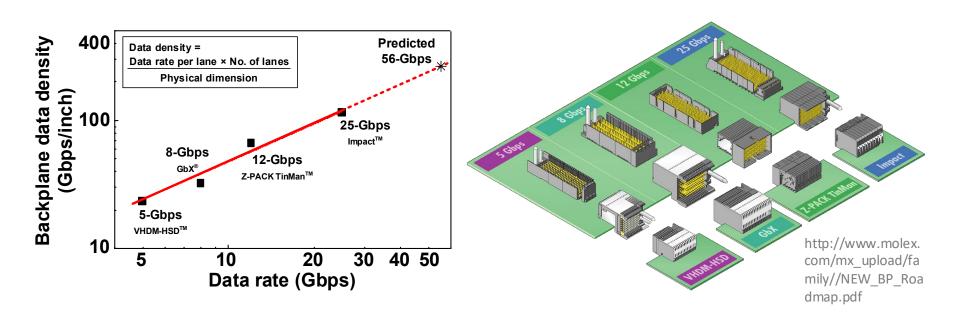

- High-speed backplane connectors roadmap

- Higher data rate↑, higher data density↑

- For each backplane link

- Smaller physical dimension, closer distance

- Be more robust and <u>quieter</u>

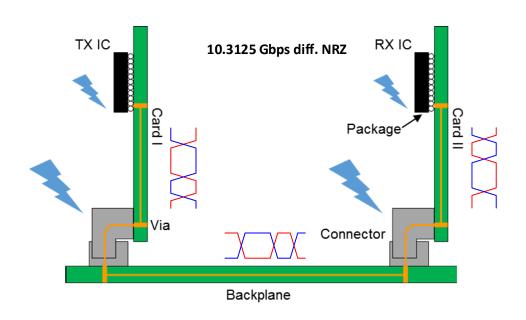

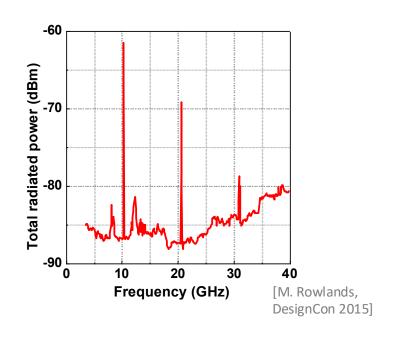

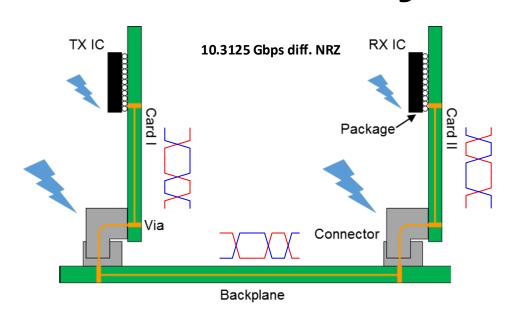

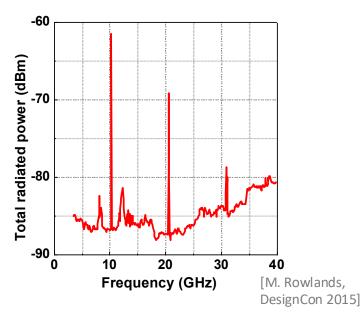

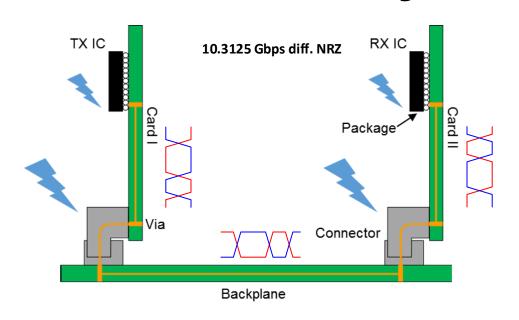

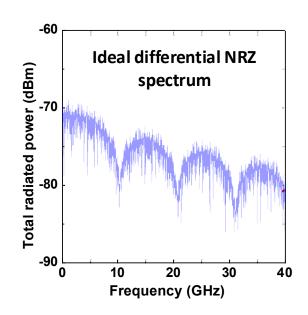

## **EMI Case Study in Backplane Link**

- EMI radiation of backplane communication module

- EMI radiations at  $2f_{Nyquist}$ ,  $4f_{Nyquist}$ , ... (e.g., 10 Gbps NRZ,  $f_{Nyquist}$  = 5 GHz)

- Ideal NRZ\* data has no frequency component @ 2f<sub>Nyquist</sub>, 4f<sub>Nyquist</sub>, 6f<sub>Nyquist</sub> ...

- NRZ = non-return-to-zero

- Distorted differential NRZ signals

# Wireline and Optical Transmitters 有线和光发射机

Prof. C. Patrick Yue 俞捷教授

芯动力人才计划®第 125 期国际名家讲堂

#### **Section Outline**

- Architecture

- VCSEL Transmitter

- MRM Transmitter

- MZM Transmitter

- Wireline Transmitter

- Key Circuits

- Multiplexer

(Now Opensource: https://github.com/HKUST-ECE-IC-Design-Center-OWL/SHARE-by-OWL-HKUST-4to1-MUX-for-28Gbaud-Optical-TX)

- Output Driver

- Pre-emphasis

- Practical Issues

- EMI Suppression Due to CM Noise to Reduce Radiation Emissions

#### **Section Outline**

- Architecture

- VCSEL Transmitter

- MRM Transmitter

- MZM Transmitter

- Wireline Transmitter

- Key Circuits

- Multiplexer

- Output Driver

- Pre-emphasis

- Practical Issues

- EMI Suppression Due to CM Noise to Reduce Radiation Emissions

# A 56-Gb/s PAM-4 VCSEL Transmitter with Piecewise Nonlinearity Compensation and Asymmetric Equalization

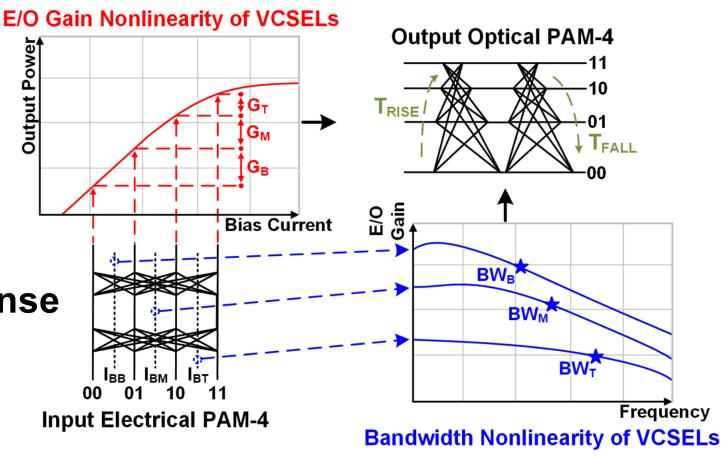

### Non-idealities of VCSEL

- Bias current ↑, E/O gain ↓

- $-G_{B} > G_{M} > G_{T}$

- Bias current ↑, E/O BW ↑

- $-BW_B < BW_M < BW_T$

- Asymmetric rise/fall response

- $-T_{RISE} < T_{FALL}$

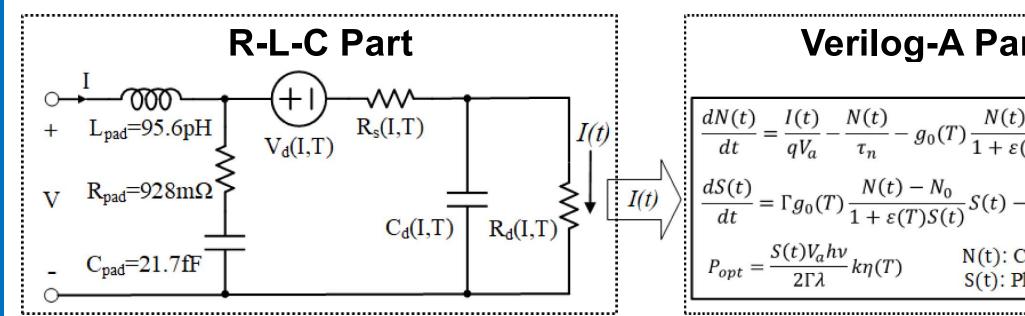

# VCSEL Modeling

Verilog-A Part

$$\frac{dN(t)}{dt} = \frac{I(t)}{qV_a} - \frac{N(t)}{\tau_n} - g_0(T) \frac{N(t) - N_0}{1 + \varepsilon(T)S(t)} S(t)$$

$$\frac{dS(t)}{dt} = \Gamma g_0(T) \frac{N(t) - N_0}{1 + \varepsilon(T)S(t)} S(t) - \frac{S(t)}{\tau_p} + \frac{\Gamma \beta N(t)}{\tau_n}$$

$$P_{opt} = \frac{S(t)V_ah\nu}{2\Gamma\lambda} k\eta(T) \qquad \text{N(t): Carrier density}$$

$$S(t): \text{Photon density}$$

- V<sub>a</sub>: volume of active region,

- $\tau_n$ : carrier lifetime,

- $g_0$ : gain slope coefficient,

- $N_0$ : transparency carrier density,

- $\tau_n$ : photon lifetime,

- $\varepsilon$ : gain compression factor,

- Γ: optical confinement factor,

- $\beta$ : spontaneous capture efficiency,

- q: electron charge.

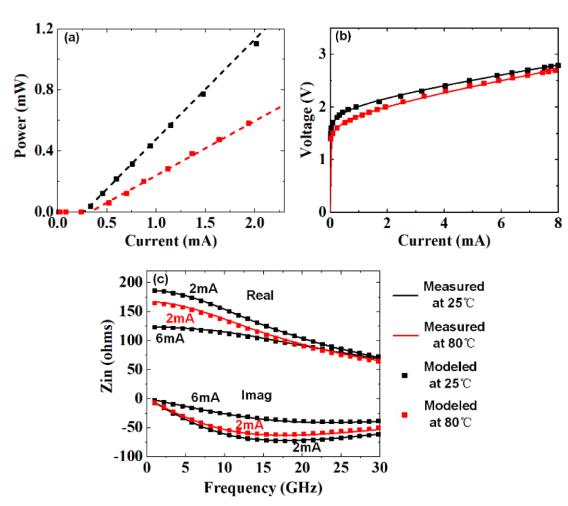

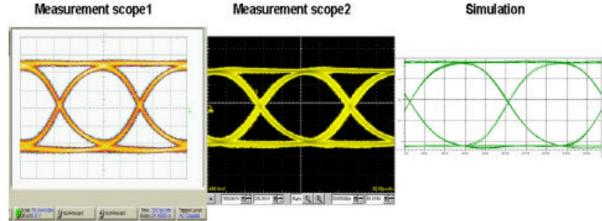

## VCSEL Modeling

#### Simulation vs. Measurement

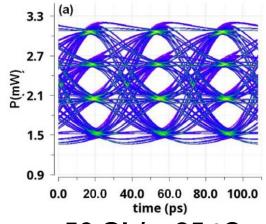

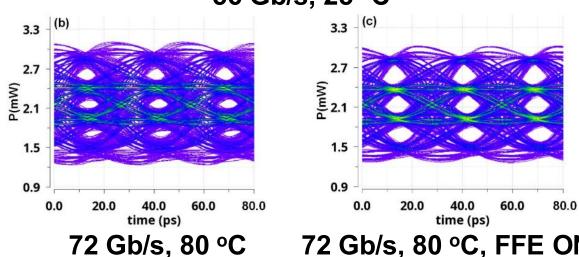

#### **Simulated Eye Diagrams**

56 Gb/s, 25 °C

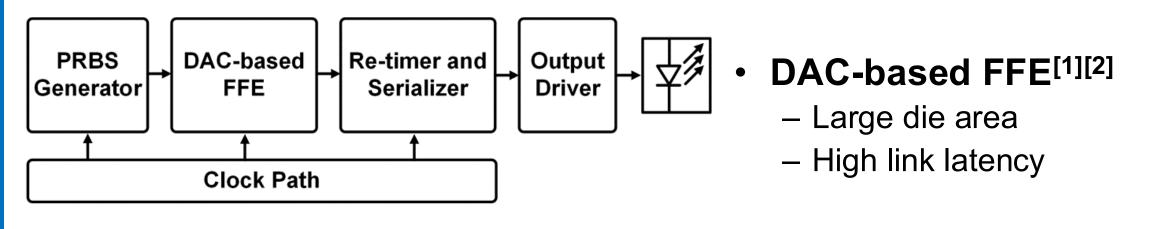

## **Prior VCSEL TX Works**

- Analog asymmetric FFE<sup>[3][4]</sup>

- Cannot fully compensate for VCSEL non-idealities

[1] A. Tyagi et al., PTL, 2018 [2] P.-J. Peng et al., JSSC, 2022 [3] J. Hwang et al., VLSI, 2019 [4] H. Do et al., ASSCC, 2021

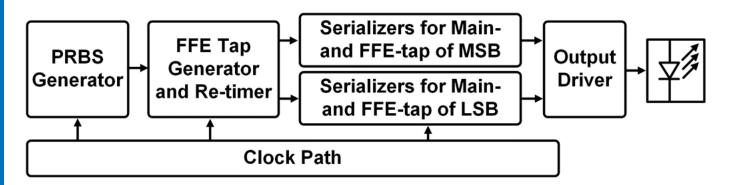

## **Proposed Compensation Methods**

- Thermometer code-based architecture for piecewise compensating E/O gain and E/O BW nonlinearities

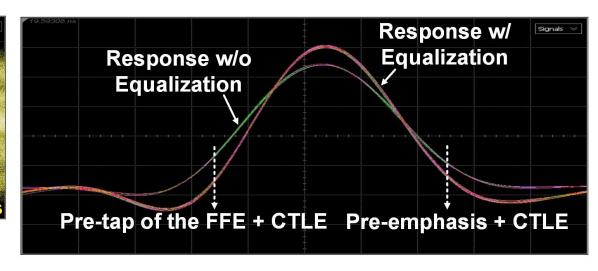

- Asymmetric pre-emphasis for relieving asymmetric optical response

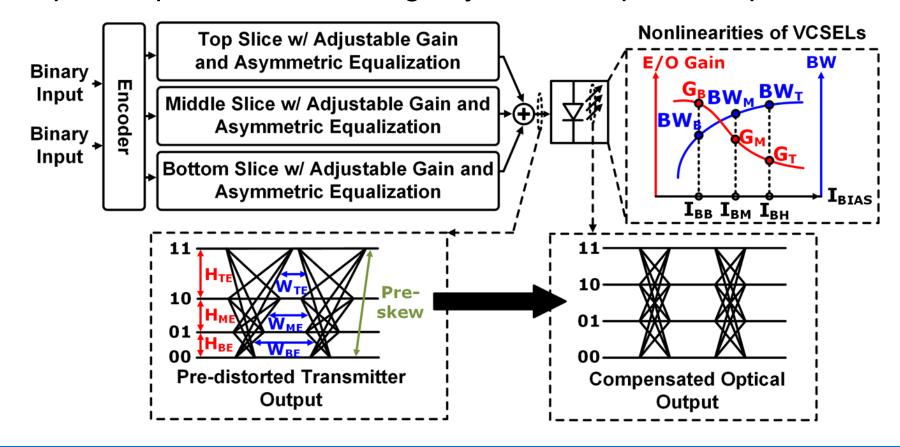

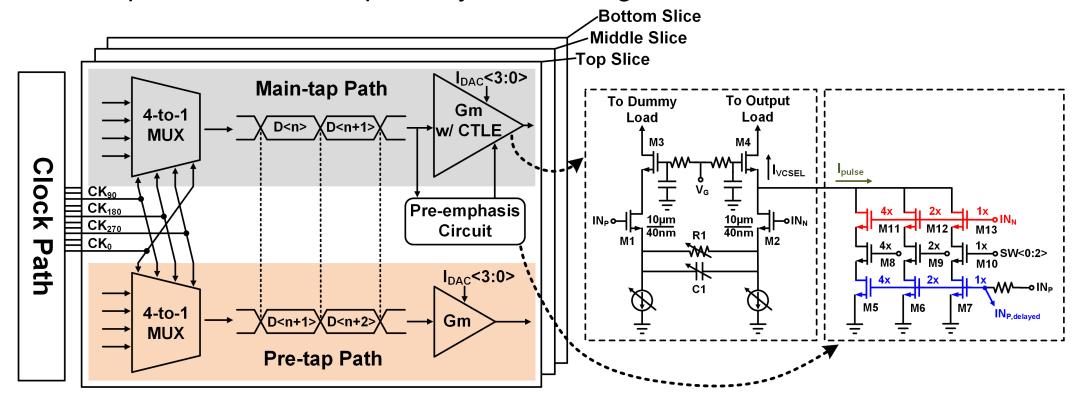

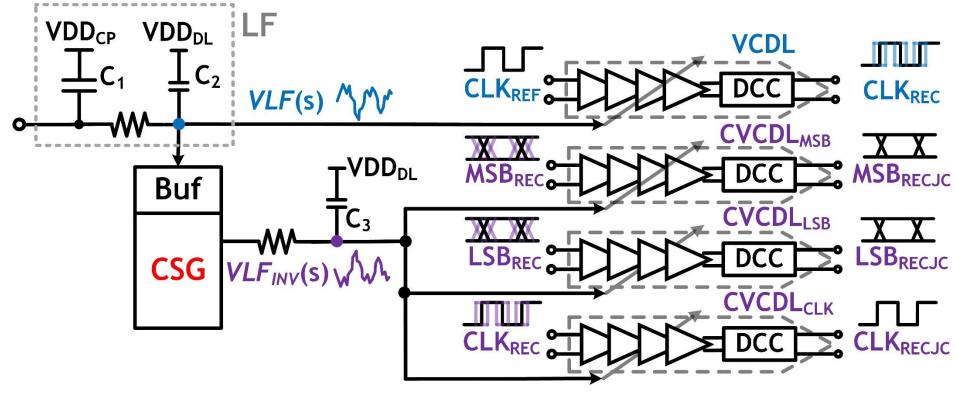

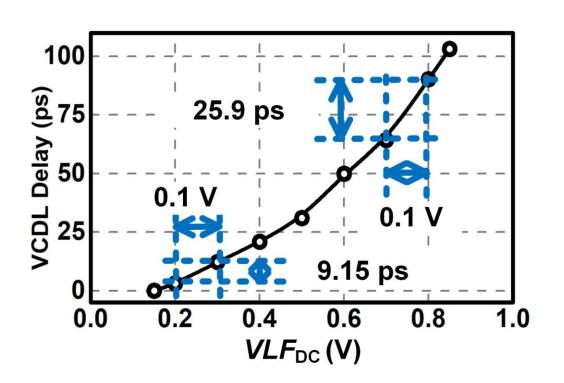

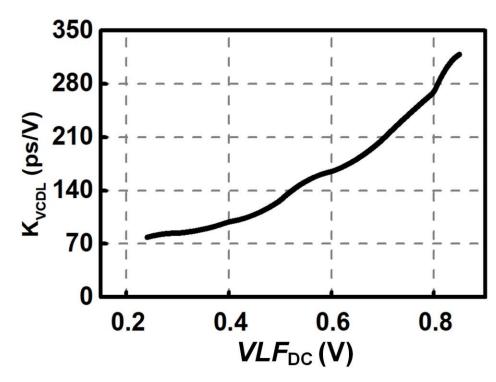

#### **VCSEL TX Architecture**

PIT

#### Data path

- 2-tap FFE

- Gm cell-merged CTLE

- Pre-emphasis circuit

#### Clock path

- Wideband PLL

- Clock tree with VCDLs

#### Optical part

Wide-bonded anodedriven VCSEL

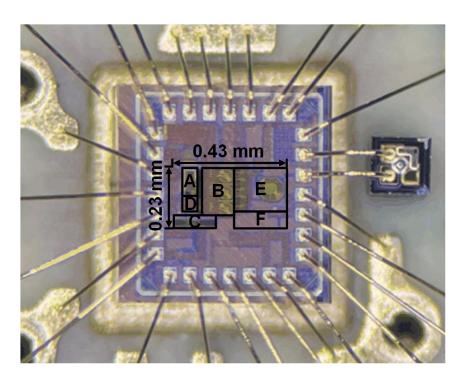

#### **Measurement Overview**

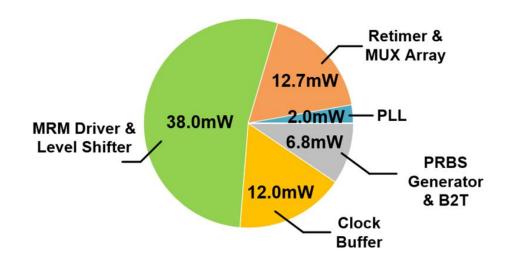

- Fabricated in 40-nm bulk CMOS

- Transmitter core occupies ~0.1 mm²

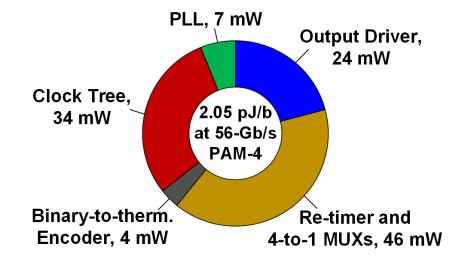

- Consumes 115 mW at 56-Gb/s PAM-4

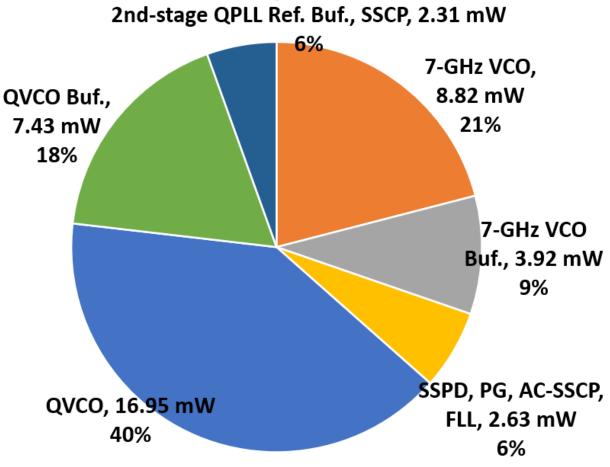

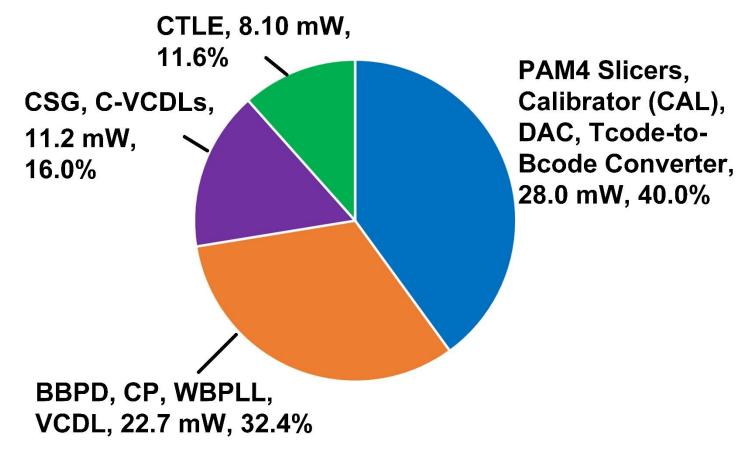

#### **Power Breakdown**

- A PRBS Generator + Binary-to-therm. Encoder

- B Re-timer + 4-to-1 Multiplexers

- C Phase-locked Loop

- D Clock Tree

- E Output Driver

- F Bias Circuit + I<sup>2</sup>C

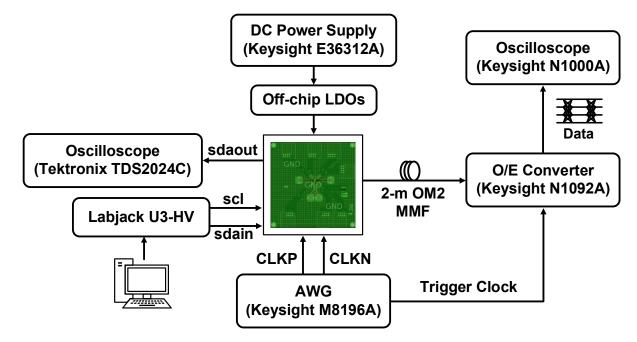

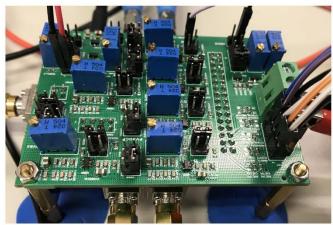

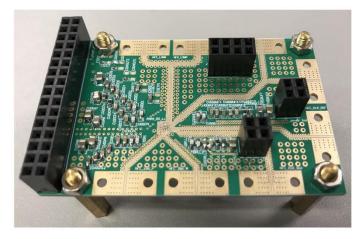

## **Measurement Setup**

- A commercial VCSEL wire-bonded with the TX for optical measurements

- The optical signal is butt-coupled to the multi-mode fiber

Scan to Watch

Measurement Video

Arbitrary Waveform Generator

O/E Converter

Oscilloscope for Clock

Oscilloscope for Data

**Measurement Setup**

**Measurement Environment**

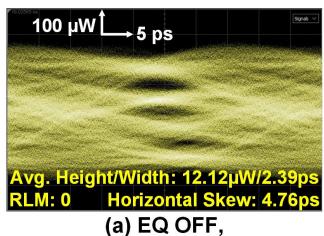

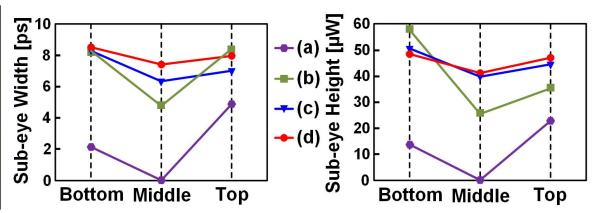

#### **Measurement Results**

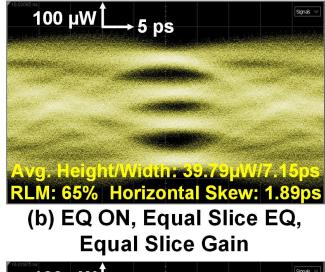

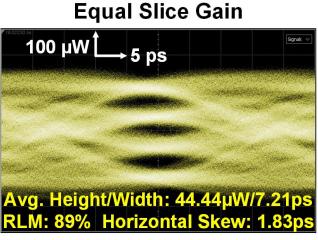

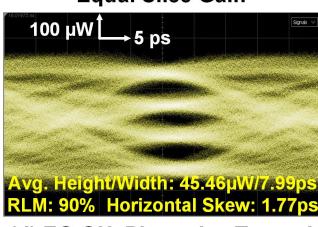

(c) EQ ON, Equal Slice EQ, Piecewise Tuned Slice Gain

(d) EQ ON, Piecewise Tunned Slice EQ and Slice Gain

## **Comparison with Prior Works**

|                               | PTL'18<br>A. Tyagi <i>et al</i> . | JSSC'22<br>PJ. Peng et al. | VLSI'19<br>J. Hwang <i>et al</i> . | ASSCC'21<br>H. Do et al.             | This work                              |

|-------------------------------|-----------------------------------|----------------------------|------------------------------------|--------------------------------------|----------------------------------------|

| CMOS Node [nm]                | 65                                | 40                         | 65                                 | 40                                   | 40                                     |

| Architecture Signaling Scheme | 1/2-rate<br>PAM-4                 | 1/4-rate<br>PAM-4          | 1/4-rate<br>PAM-4                  | 1/4-rate<br>PAM-4                    | 1/4-rate<br>PAM-4                      |

| Data Rate [Gbps]              | 50                                | 56 64                      |                                    | 64                                   | 56                                     |

| OMA [mW]                      | 2.00                              | 0.81*                      | 2.50*                              | 1.08*                                | 1.18*                                  |

| Power effi. [pJ/b]            | 5.12                              | 1.73                       | 2.69#                              | 2.09                                 | 2.05#                                  |

| Core Area [mm²]               | 0.31                              | 0.47                       | 0.28                               | 0.16                                 | 0.10                                   |

| Asymmetric<br>Equalization    | 2.5-tap DAC-<br>based FFE         | 2-tap DAC-based<br>FFE     | 3-tap LSB/MSB-<br>based Asym. FFE  | 3-tap LSB/MSB-<br>based Asym.<br>FFE | 2-tap FFE +<br>CTLE + Pre-<br>emphasis |

| Nonlinearity<br>Compensation  | Full                              | Full                       | Partial                            | Partial                              | Full                                   |

| Method Type                   | Digital                           | Digital                    | Analog                             | Analog                               | Mixed-signal                           |

<sup>\*3-</sup>dB butt coupling loss de-embedded

<sup>#</sup>Includes on-chip PLL

## Conclusion

#### A PAM-4 VCSEL transmitter in 40-nm CMOS

- The piecewise nonlinearity compensation improves optical eye height/width and RLM by 14%/12% and 38%, respectively

- The asymmetric equalization scheme reduces the horizontal optical eye skew by 63%

- The transmitter achieves a power efficiency of 2.05 pJ/b at 56-Gb/s PAM-4

- The core occupies a die area of 0.1 mm<sup>2</sup>

# A 56-Gb/s PAM-4 Transmitter Using Silicon Photonic MRM in 40nm CMOS

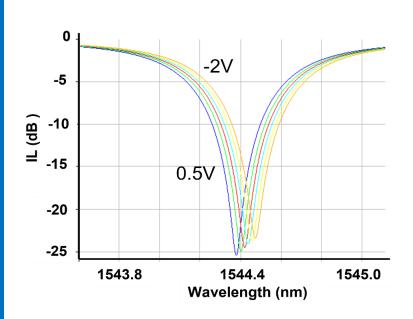

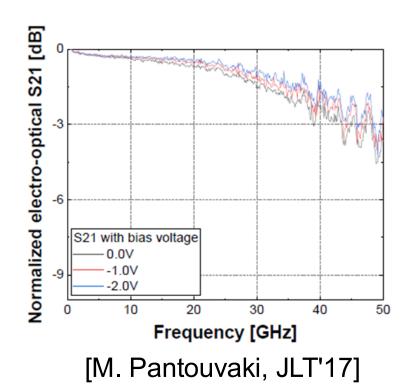

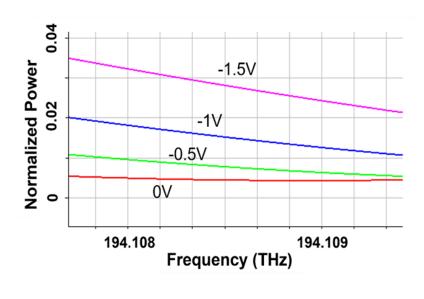

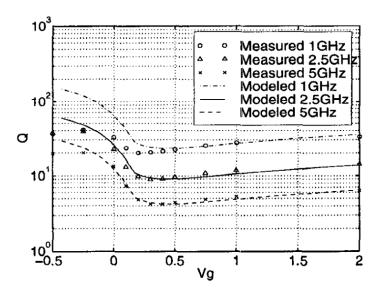

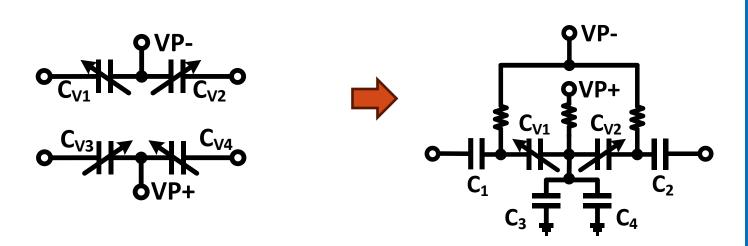

#### **MRM Characteristics**

High voltage swing for

large extinction ratio (ER)

High-swing voltage mode driver needed

Bias-dependent E-O BW

Equalization needed

- Nonlinear E-to-O conversion

- Independent level adjustment

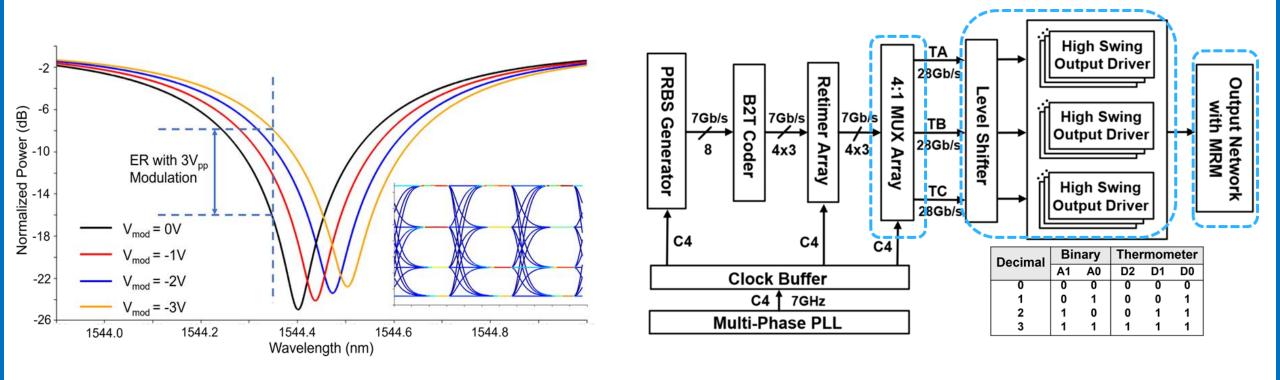

#### **Transmitter Architecture**

- For PAM-4 implementations, nonlinear E-to-O conversion results in unequal eye-heights

- Quarter-rate structure to balance the power and complexity

- Thermometer-coded topology is used for independent single-eye-height adjustment

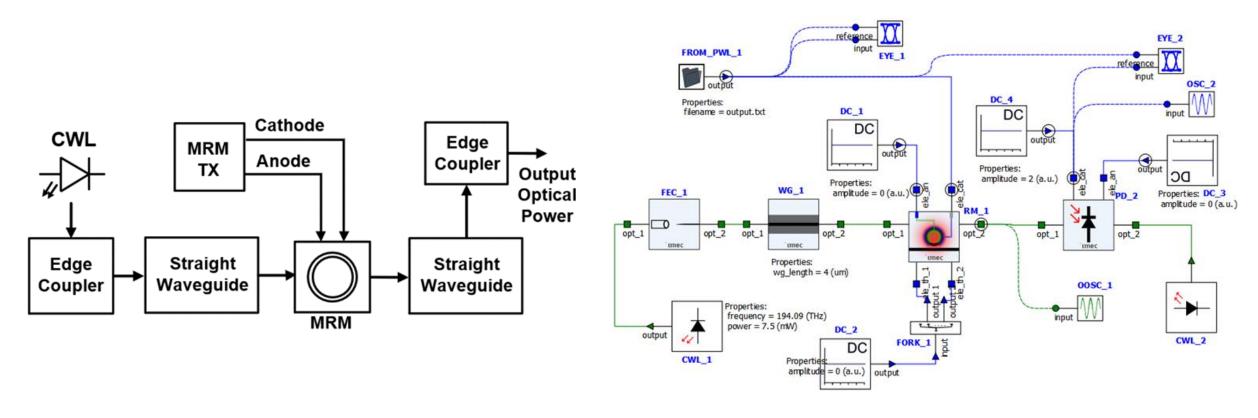

## **Optical Simulation Setup**

- Custom-designed Verilog-A model is replaced by the model provided by the foundry

- Commercial software Ansys Lumerical INTERCONNECT is used for simulation

- CW lasers, edge couplers, and straight waveguides are included in the simulation

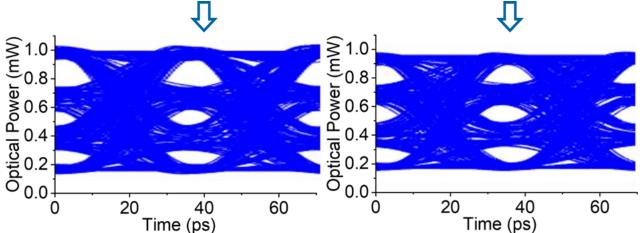

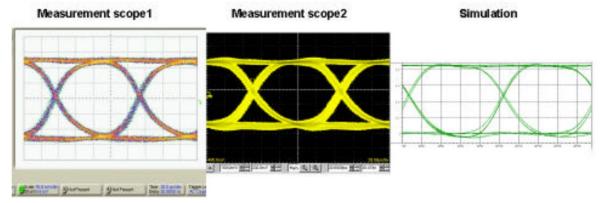

## **Simulation Results**

Before swing adjustment After swing adjustment

Simulated electrical PAM-4 eye diagram at 56 Gb/s

Simulated optical PAM-4 eye diagram at 56 Gb/s

- The electrical output can result in unequal optical eyes due to nonlinearities of MRM

- Single-eye-height adjustment combined with accurate optical simulation is necessary

- Power consumption: 71.5mW

# **Performance Summary**

|                               | PTL'18                                  | JSSC'15   | MWSCAS'19     | JSSC'20          | This Work     |

|-------------------------------|-----------------------------------------|-----------|---------------|------------------|---------------|

| Data Rate (Gb/s) 56           |                                         | 25        | 25            | 10               | 56            |

| Modulation Scheme             | Modulation Scheme NRZ NRZ               |           | PAM-4         | BPSK             | PAM-4         |

| Output Swing (V)              | 1                                       | 4.4       | 2.4           | 1.55             | 3.1           |

| Electronic IC Process         | 28nm FDSOI<br>CMOS                      | 65nm CMOS | 65nm CMOS     | 45nm SOI<br>CMOS | 40nm CMOS     |

| Optical Simulation            | N/A                                     | Verilog-A | imec ISIPP50G | N/A              | imec ISIPP50G |

| Energy Efficiency (pJ/bit)    | 0.71                                    | 4.54      | 1.6           | 2.3              | 1.28          |

| FOM <sup>a</sup> (pJ/(bit·V)) | FOM <sup>a</sup> (pJ/(bit·V)) 0.71 1.03 |           | 0.67          | 1.48             | 0.41          |

## **Conclusions**

#### A 56-Gb/s PAM-4 optical transmitter using a silicon photonic MRM

- Thermometer-coded topology used for independent single-eye-height adjustment

- Pulsed tri-state inverter-based 4:1 MUX releases the bandwidth constraint

- High-swing voltage-mode driver with swing adjustability achieves large ER

- E-O co-simulations are performed using device models from the foundry to optimize the TX design

# A 56-Gbaud 7.3-V<sub>ppd</sub> Linear Transmitter for MZM in 130-nm SiGe BiCMOS

#### **Motivation**

# **Design Challenges for Linear TX**

- Large output swing for high optical extinction ratio

- High linearity to support advanced modulation schemes for high data rate

- Equalization to compensate for high-frequency loss from E/E and E/O interfaces

- Analog serialization to relieve BW requirements for DACs

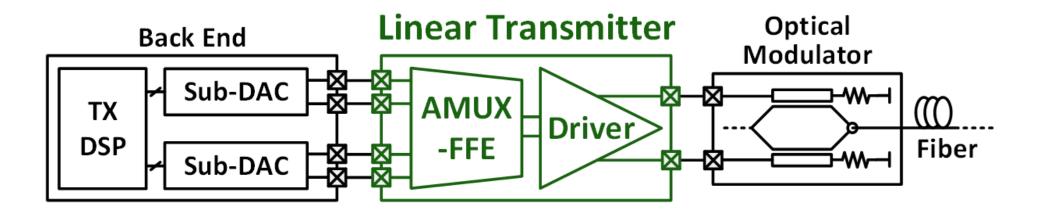

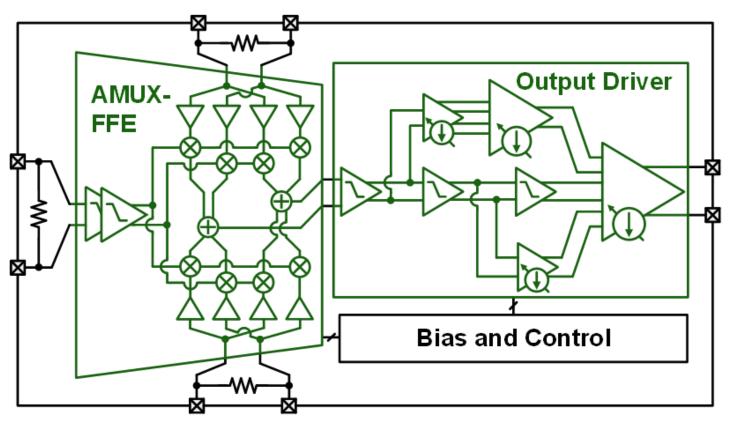

#### **Transmitter Architecture**

#### AMUX-FFE

- Serializes data streams from half rate to full rate

- Generates equalized signal with a tap generatorless re-config. FFE

#### Output Driver

Linearly amplifies signal swing using a dynamic triple-stacked topology

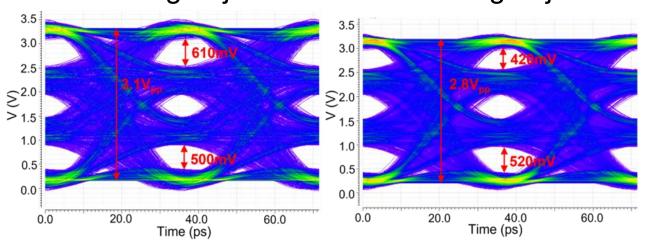

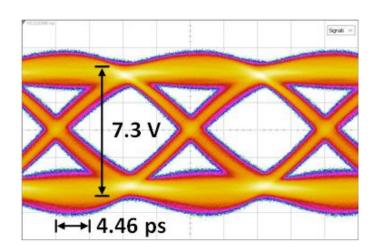

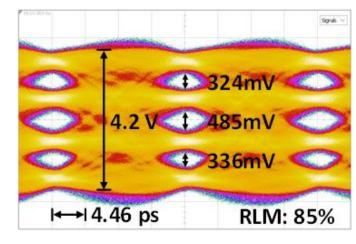

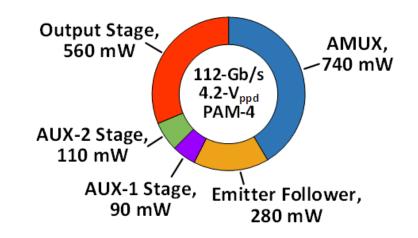

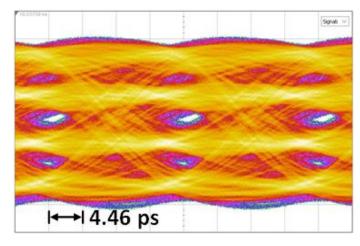

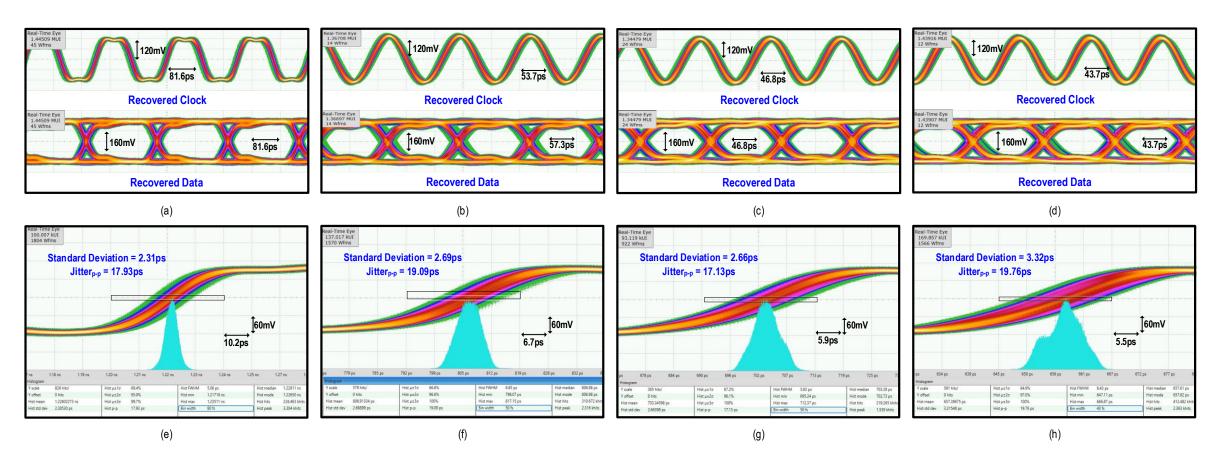

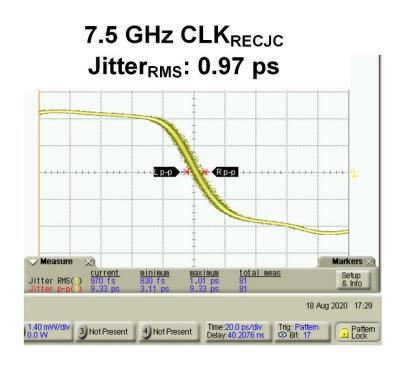

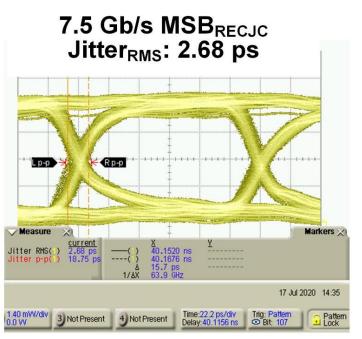

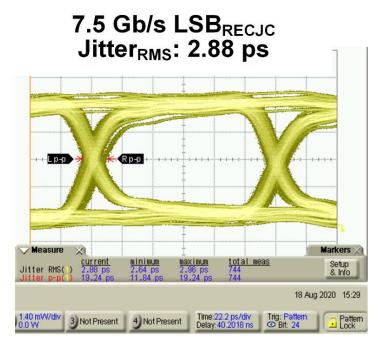

#### **Measurement Results**

- The whole transmitter supports a maximum output swing of 7.3-Vppd @ 56-Gbaud NRZ

- With FFE, 56-Gbaud 4.2-Vppd PAM-4 is also achieved, with 1.78-W power consumption

56 Gbaud with FFE Off

56 Gbaud with FFE On

56 Gbaud with FFE Off

## **Performance Summary**

|                                         |                                      | TMTT'17<br>P. Rito <i>et al.</i> | JSSC'20<br>A. H. Ahmed <i>et al.</i> | BCICTS'21<br>A. Fatemi <i>et al.</i> | BCICTS'22<br>F. Iseini <i>et al.</i> | This Work                          |

|-----------------------------------------|--------------------------------------|----------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|------------------------------------|

| Technology                              |                                      | 130-nm SiGe BiCMOS               | 130-nm SiGe BiCMOS 130-nm SiGe Bi    |                                      | 130-nm SiGe BiCMOS                   | 130-nm SiGe BiCMOS                 |

| f <sub>T</sub> / f <sub>MAX</sub>       | ([GHz]                               | 300/500                          | 250/NA 300/500                       |                                      | 380/520                              | 250/340                            |

| Output Impedan                          | ce Matching [Ω]                      | 100                              | 100                                  | 100                                  | 100                                  | 100                                |

| Equalia                                 | zation                               | NA                               | NA                                   | 1-tap FFE                            | NA                                   | Reconfig. FFE                      |

| Seriali                                 | zation                               | NA NA NA                         |                                      | NA                                   | NA                                   | 2:1 Analog                         |

| Maximum Ouput Swing [V <sub>ppd</sub> ] |                                      | 4<br>@90-Gb/s PAM-4              | 6<br>@64-Gb/s NRZ                    | 4<br>@64-Gb/s Duobinary              | 2<br>(estimated by P1dB)             | 7.3<br>@56-Gb/s NRZ                |

| Maximum Data Rate [Gb/s]                |                                      | 120<br>@3-V <sub>ppd</sub> NRZ   | 138<br>@2.4-V <sub>ppd</sub> PAM-4   | 64<br>@4-V <sub>ppd</sub> Duobinary  | 128<br>@1.2-V <sub>ppd</sub> PAM-4   | 112<br>@4.2-V <sub>ppd</sub> PAM-4 |

| Data Rate-Output Sw                     | a Rate-Output Swing Product [V·Gb/s] |                                  | 384                                  | 256                                  | 256                                  | 470                                |

| Driver THD                              |                                      | 3.8%<br>@1GHz, 3V <sub>ppd</sub> | 3.6%<br>@1GHz, 6V <sub>ppd</sub>     | 5.5%<br>@1GHz, 4V <sub>ppd</sub>     | 6%<br>@5GHz, 2V <sub>ppd</sub>       | 1.6%<br>@1GHz, 6V <sub>ppd</sub>   |

| Driver Gain [dB]                        |                                      | 12.5                             | 30 (with VGA)                        | 30 (with VGA) 24                     |                                      | 17                                 |

| Power Consumption                       | Driver                               | 550                              | 1000                                 | 1030                                 | 280                                  | 1040                               |

| [mW]                                    | AMUX                                 | NA                               | NA                                   | NA                                   | NA                                   | 740                                |

| FoM# [bit/s/Hz]                         |                                      | 0.00818                          | 0.00397                              | 0.00414                              | 0.00217                              | 0.00867*                           |

#FoM =  $\frac{\text{Maximum Data Rate}}{f_T}$  ·  $\frac{(\text{Output Swing @ Maximum Data Rate})^2}{8 \cdot \text{Output Impedance Matching} \cdot \text{Power Consumption}}$

## Conclusion

#### A linear transmitter in 130-nm SiGe BiCMOS for optical modulators

- Tap generator-less re-configurable AMUX-FFE

- Dynamic triple-stacked driver topology

- Demonstrates 7.3-Vppd maximum output swing @56-Gbaud NRZ

- Supports 56-Gbaud 4.2-Vppd PAM-4

- Achieves the best FoM among linear TX/drivers in the same node

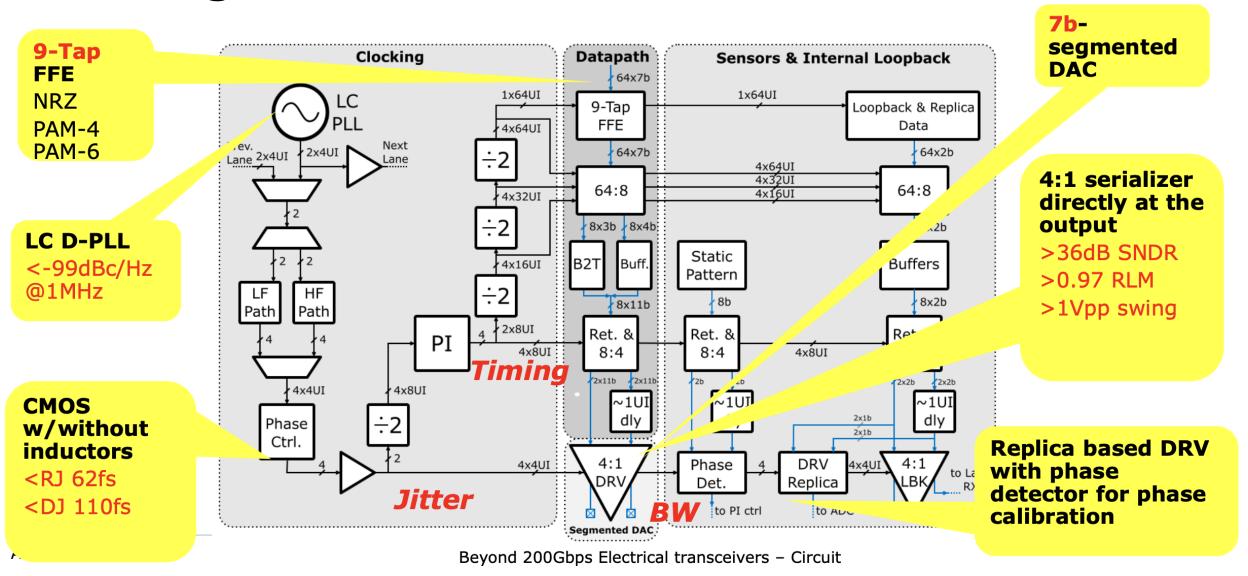

## Beyond 200Gb/s Wireline Transceiver

Source: ISSCC Forum 2024-Forum 6.3, Intel

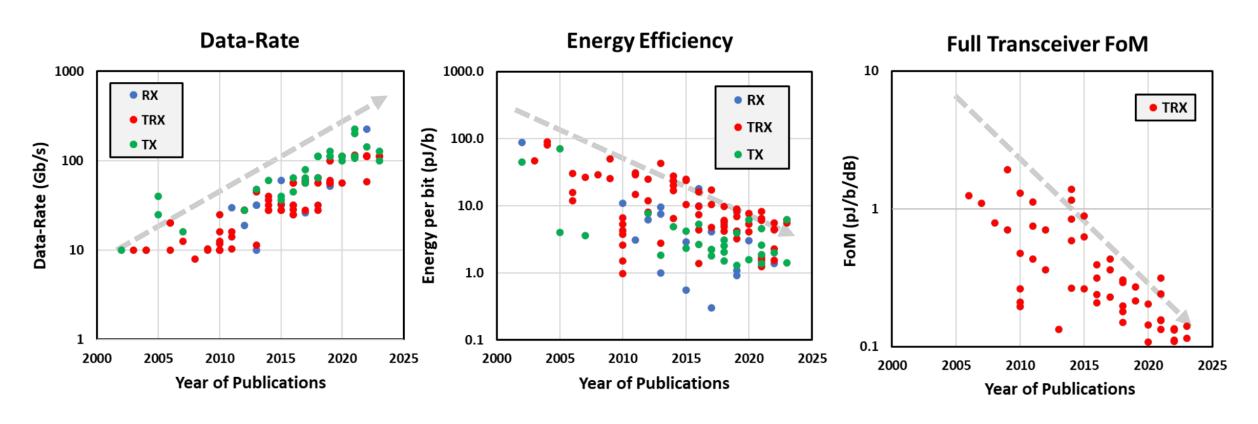

## **CMOS Electrical Links in the Past 21 Years**

■ Both speed and efficiency have scaled by >21x in the past 21 years!

From ISSCC/VLSI (2002-2022) [1-40]

PIT

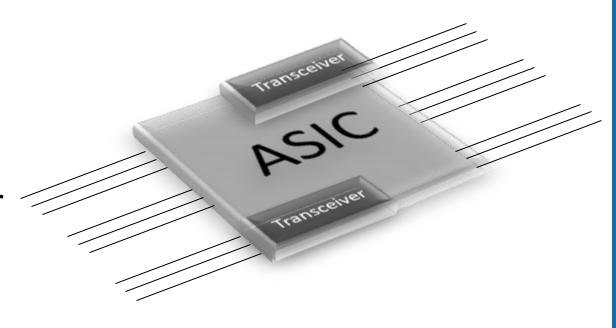

## 100+Gb/s SerDes PHY Examples

FPGAs, NW-SW SOCs, ASICs, IPs, ...

- Agilex-I™ FPGA

- 116Gb/s PAM-4 LR

- 4.2 Tb/s Max BW

- Tomahawk<sup>™</sup> 5

- 51.2 Tb/s

- 64x800GbE

- 8x106Gb/s PAM4 LR

- 28.8 Tb/s SW 800GbE

- 288x112G SerDes in 7nm

- 25.6 Tb/s SW

- 128x100G SerDes

- Alaska™

- Dual 400GbE w/ 100G PAM4 SerDes in 5nm

- **EPHY**<sup>TM</sup>

- 112G LR SerDes in 7<sub>nm</sub>

- AlphaCORE™

- 112G LR SerDes IP

112G-ELR PAM4 SerDes PHY in 5nm

**BAT**

## **Modulation for Wireline TRX**

- Modulation → PAM-4

- Best SNR SNR and power performing at tested channel

- Backward compatibility

- Electrical to optical compatibility

- Testing methodology and equipment maturity/availability

| Data Ratem Gb/s    | 224    | 224   | 224   | 224   | 224   | 224    |

|--------------------|--------|-------|-------|-------|-------|--------|

| PAMn Levels        | 4      | 5     | 6     | 7     | 8     | 16     |

| Bit per symbol     | 2.00   | 2.32  | 2.58  | 2.81  | 3.00  | 4.00   |

| Symboe Rate (GS/s) | 112.00 | 96.47 | 86.66 | 79.79 | 74.67 | 56.00  |

| UI (ps)            | 8.93   | 10.37 | 11.54 | 12.53 | 13.39 | 17.86  |

| Nyquist Freq       | 56.00  | 48.24 | 43.33 | 39.90 | 37.33 | 28.00  |

| SNR Delta          | 0.00   | -2.50 | -4.44 | -6.02 | -7.36 | -13.98 |

Source: "PAMn vs Channel and FEC investigation for 224 Gb/s", IEEE P802.3df Ethernet Task Force

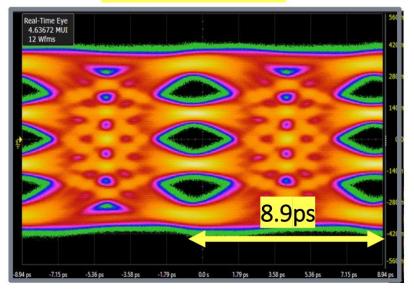

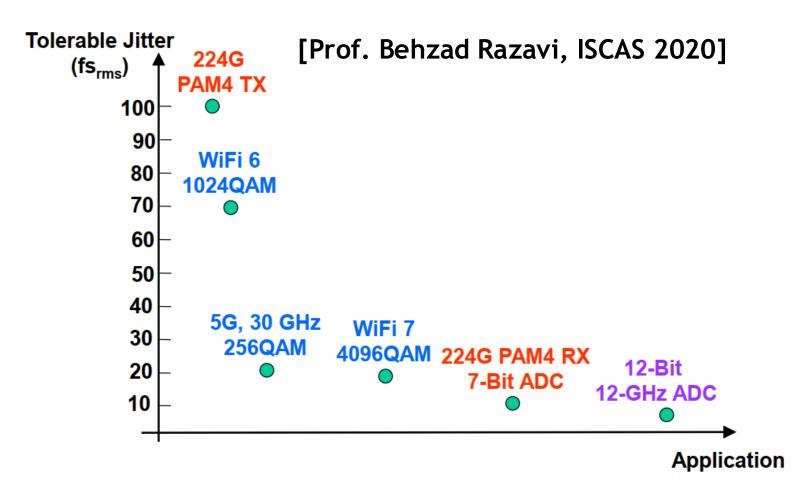

# **Key Challenges of 224-Gb/s PAM-4 Wireline TRX**

- Ultra high circuit BW > 56Ghz

- UI=8.9ps -> extra-low random jitter

< 100fs</li>

- Developing Analog to Digital converter sampling in 112GS/s (like high end scope)

- Developing Digital to Analog Converter working in 112GS/s with low noise (like high end signal generator)

- Package, channels IL and reflections

#### 224Gb/s PAM-4

J. Kim et al., ISSCC 2021

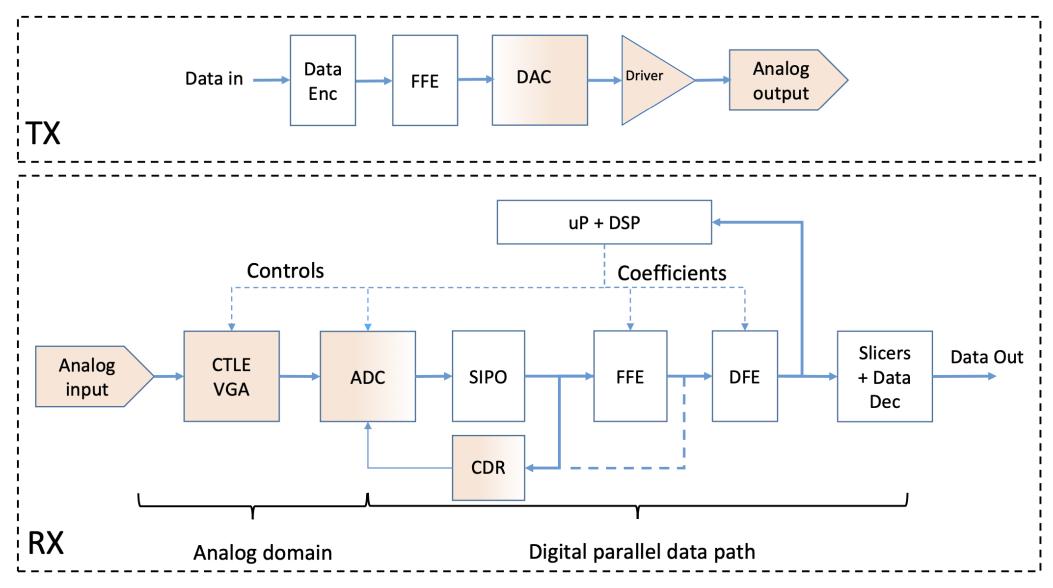

## Why DAC-ADC TRX for 224Gb/s

#### At 224Gb/s data-rate, we need to deal with

- Tough channels with higher 56GHz Nyquist

- Higher insertion loss (package, board, connector, etc.)

- Critical reflections at many UIs later than the cursor (large package and short UI)

- Sharp roll-offs or some notches

- Non-ideal smoothness (ripples in insertion loss)

- Implementation

- Analog DFE loop timing in RX can not be done with a UI=8.9ps

Need more powerful and flexible channel equalization for good BER

→ Need many-tap TX/RX FFE, continuous time EQ, DFE, sometimes advanced equalization (sliding-block DFE, MLSD, etc)

## 112/224 Gb/s DAC-ADC TRX Architecture

## E.g., A 224-Gb/s DAC-TX Architecture

#### **Section Outline**

- Architecture

- VCSEL Transmitter

- MRM Transmitter

- MZM Transmitter

- Wireline Transmitter

- Key Circuits

- Multiplexer

(Now Opensource: https://github.com/HKUST-ECE-IC-Design-Center-OWL/SHARE-by-OWL-HKUST-4to1-MUX-for-28Gbaud-Optical-TX)

- Output Driver

- Pre-emphasis

- Practical Issues

- EMI Suppression Due to CM Noise to Reduce Radiation Emissions

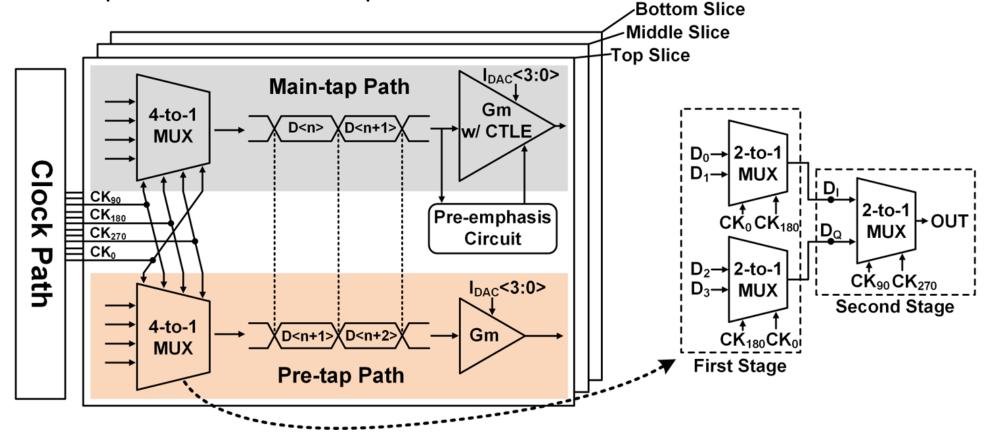

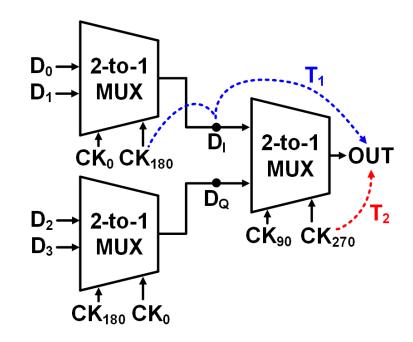

#### Functions

- 4 quarter-rate data streams → 1 full-rate data stream

- Controls tap interval of the 2-tap FFE

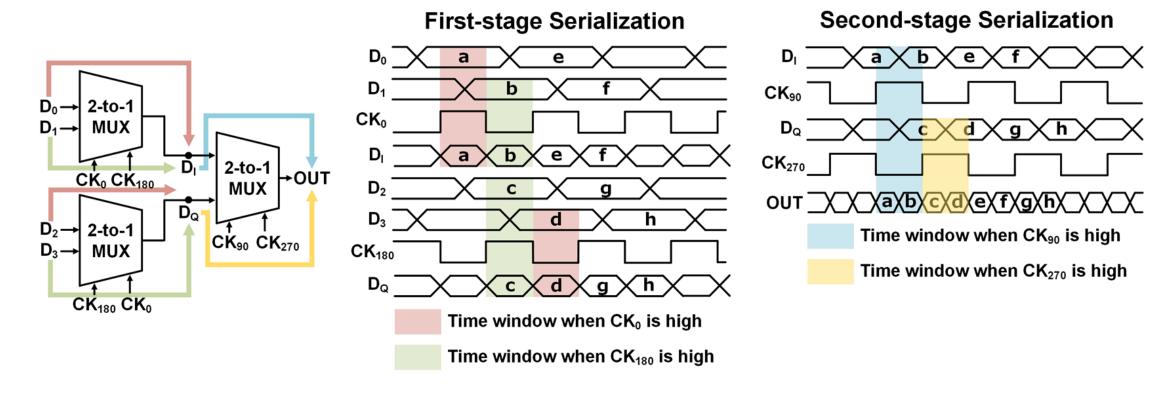

#### **Principle**

- Implemented by cascading two-stages of 2-to-1 MUXs

- 1st-stage 2-to-1 MUX serializes D<sub>0</sub>~D<sub>3</sub> to D<sub>1</sub> and D<sub>Q</sub>

- 2<sup>nd</sup>-stage 2-to-1 MUX further serializes D₁ and D₀ to OUT

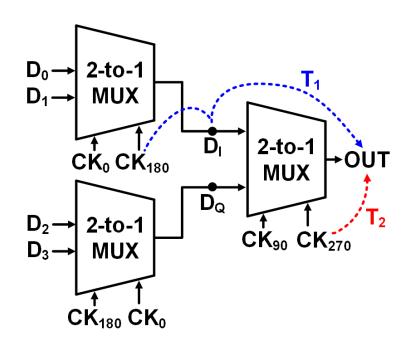

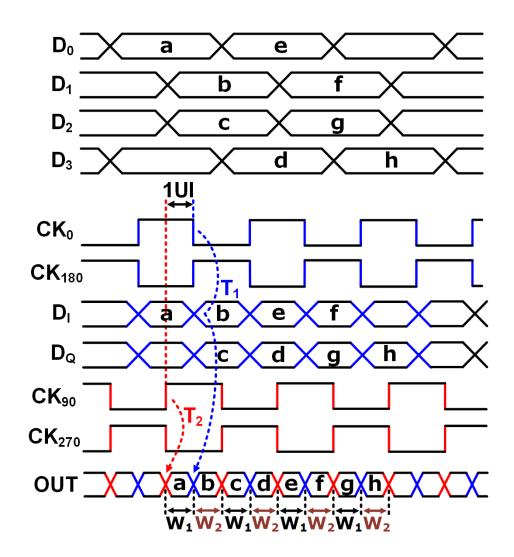

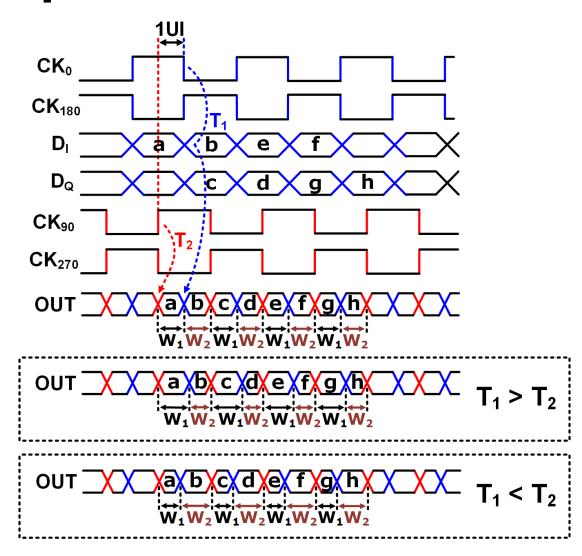

#### Output distortion issue

- T1: delay from CK<sub>0</sub> (CK<sub>180</sub>) to OUT

- T2: delay from CK<sub>90</sub> (CK<sub>270</sub>) to OUT

- T1 ≠ T2  $\rightarrow$  duty cycle distortion of the output

#### Output distortion issue

- T1: delay from CK<sub>0</sub> (CK<sub>180</sub>) to OUT

- T2: delay from CK<sub>90</sub> (CK<sub>270</sub>) to OUT

- T1 ≠ T2  $\rightarrow$  duty cycle distortion of the output

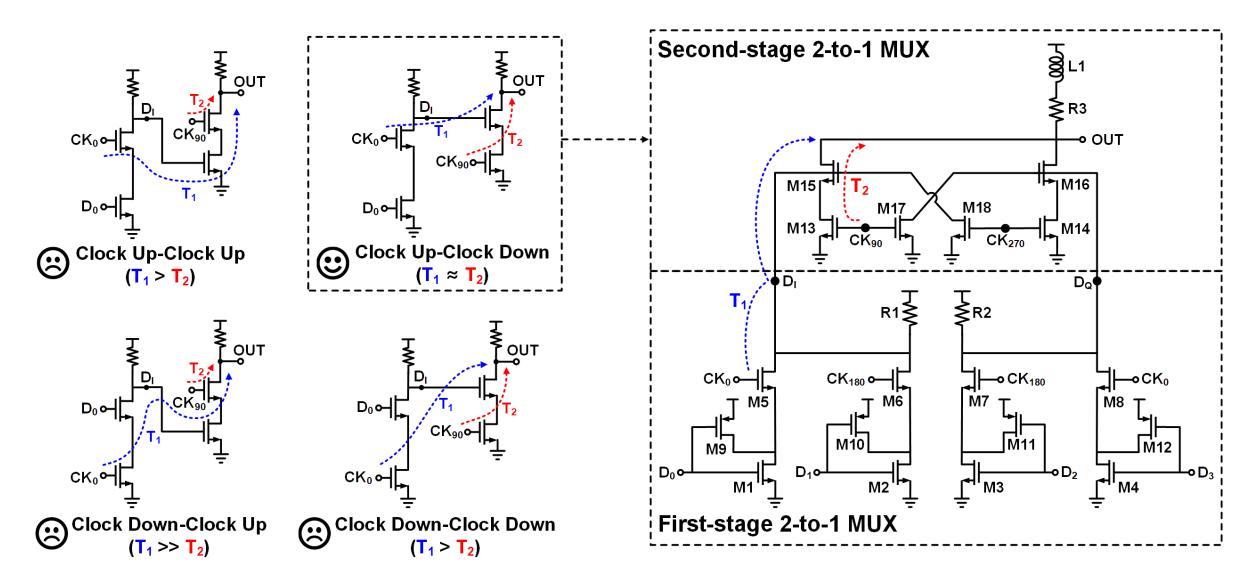

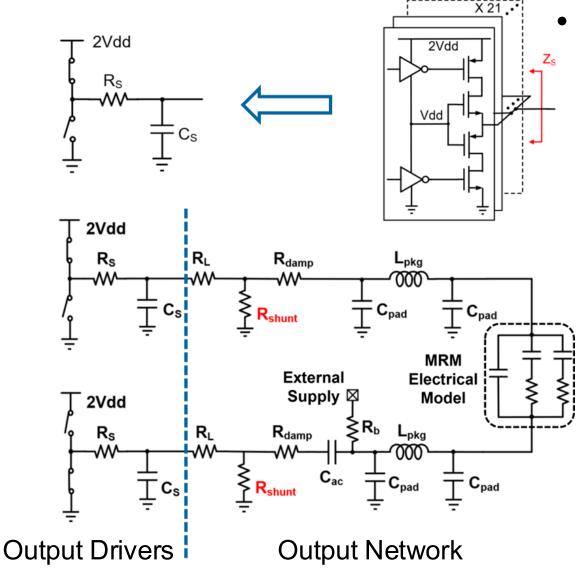

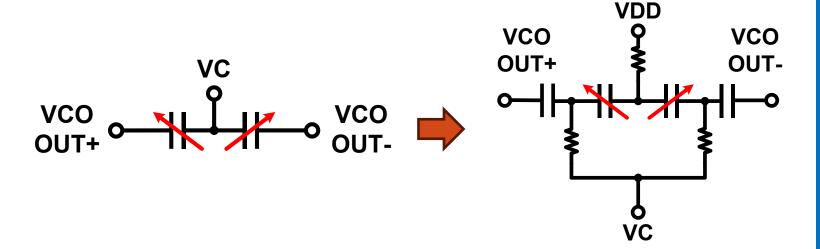

### **Output Driver for MRM and MZM**

- Multiple transistors are stacked with the middle devices biased at Vdd to achieve 2xVdd output swing

- 3-bit swing adjustability is achieved by combination of binary-weighted driver slices

- Resistors of ac-coupled level shifter are replaced by diode-connected transistors and their replicas

- By tuning Vcm\_ref, the average output voltage can be adjusted and set equally

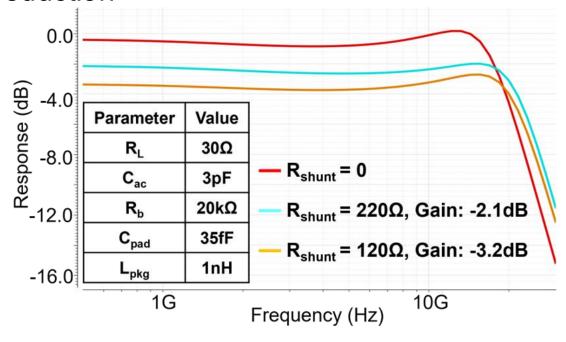

## **Output Driver for MRM and MZM**

#### Output network

- MRM driver represented by a first-order RC and optimized with the output network

- With a 220Ω-Rshunt, BW is extended from 18.6 to 22.4 GHz with a 3.2-dB dc gain reduction

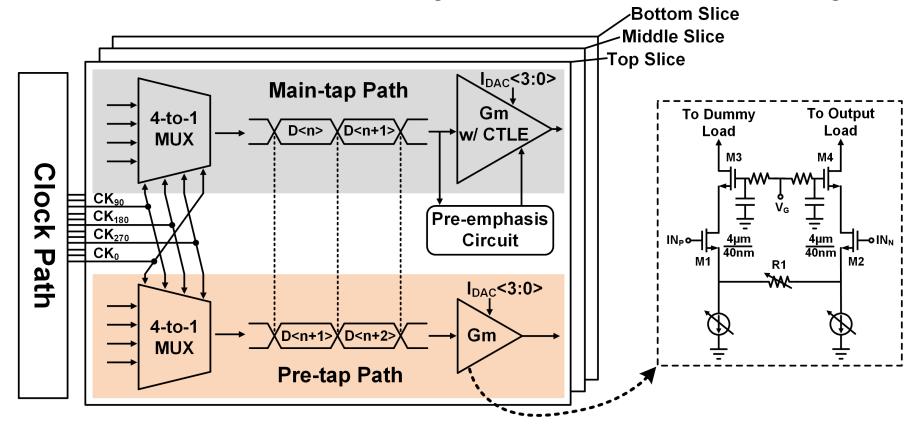

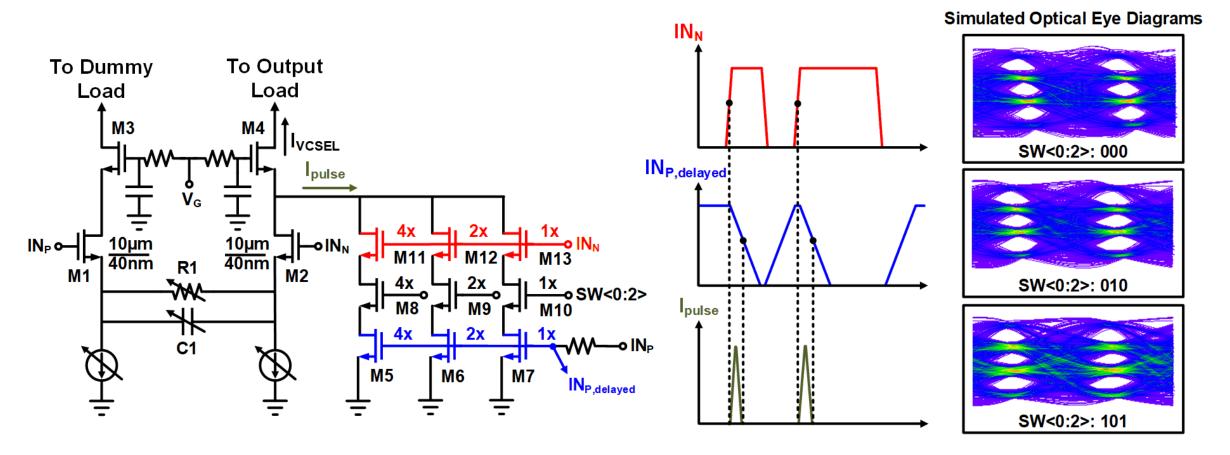

#### Output Driver for VCSEL Embedded in a 2-Tap FFE

#### Pre-tap gm cell

- Cascode structure for preventing breakdown issue

- Tunable tail current source and degenerated variable resistor for gain adjustment

### Output Driver for VCSEL Embedded in a 2-Tap FFE

#### Main-tap gm cell

- Transistors size 2.5 times larger than pre-tap gm cell

- Source-degenerated capacitor for BW extension

- Pre-emphasis circuit for optical eye skew mitigation

## **Pre-emphasis Circuit**

#### Principle

$-\text{ IN}_{N}\uparrow \rightarrow \text{I}_{VCSEL}\downarrow \rightarrow \text{IN}_{N} \text{ & IN}_{P,delayed} \text{ both high} \rightarrow \text{A sharp current pulse I}_{pulse} \text{ generated}$

#### **Section Outline**

- Architecture

- VCSEL Transmitter

- MRM Transmitter

- MZM Transmitter

- Wireline Transmitter

- Key Circuits

- Multiplexer

- Output Driver

- Pre-emphasis

- Practical Issues

- EMI Suppression Due to CM Noise to Reduce Radiation Emissions

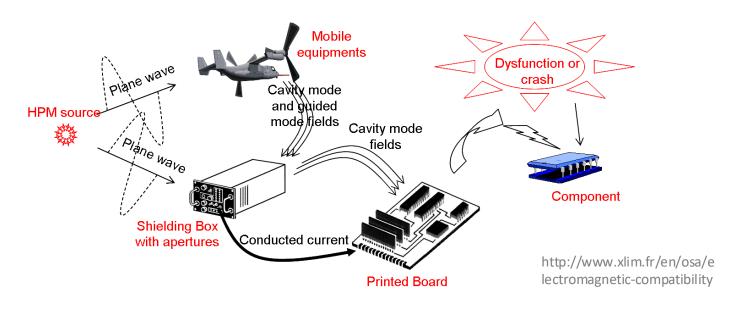

# **Analysis on EMI Related Common-Mode Noise of Serdes Transmitter**

#### What is EMI?

Most electronics generate electromagnetic emission

- Electromagnetic interference (EMI) causes malfunction of the victim electronics

- How to solve?

- Keep enough distance, be robust, and keep quiet

#### **EMI in Modern Data Center**

www.cisco.com/c/r/en/us/internet-of-everything-ioe/data-center/vision/index.html

https://avi.alkalay.net/2015/08/cloud-enabling-innovation-in-the-third-platform-era.html

- Front-side haven, but back-side disaster

- Thousands of paralleled communication modules

- Data rate of each module > 10 Gbps

- Complicated electromagnetic environment

### **Increase of Data Density**

- High-speed backplane connectors roadmap (Molex®)

- Higher data rate↑, higher data density↑

- For each backplane link

- Smaller physical dimension, closer distance

- Be more robust and <u>quieter</u>

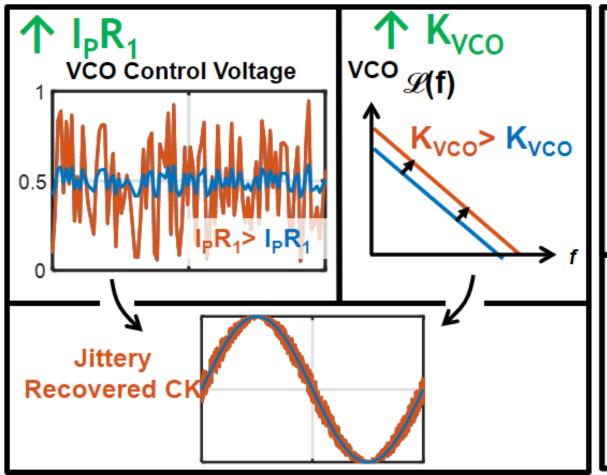

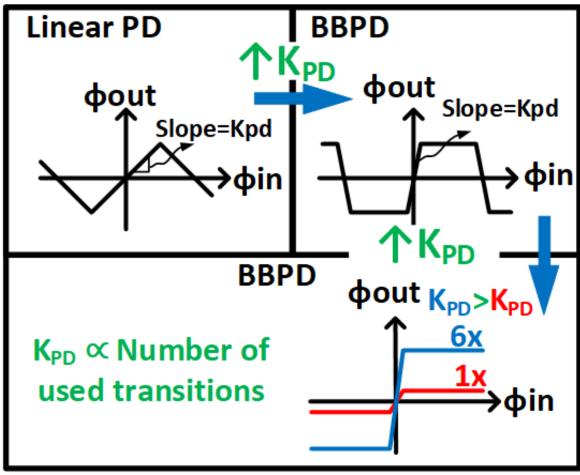

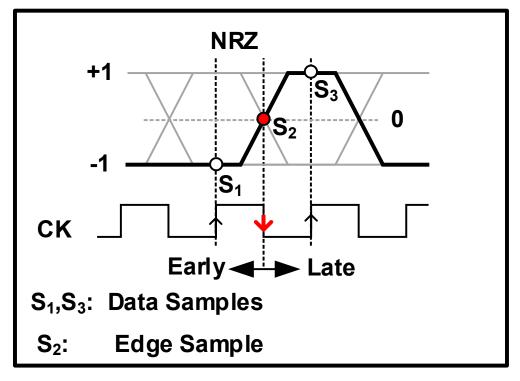

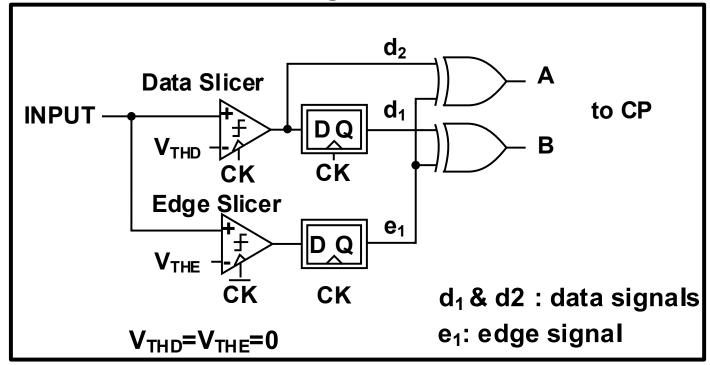

CDR/PLI

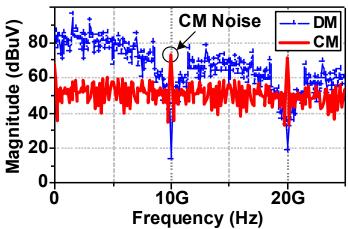

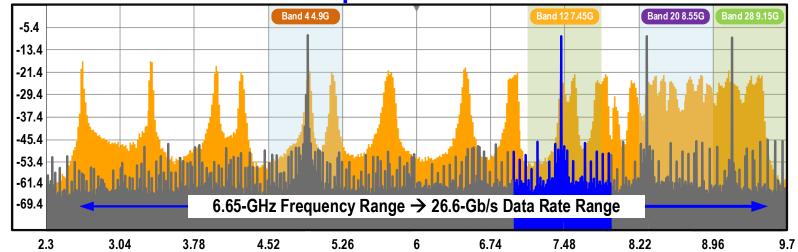

# **EMI Case Study in Backplane Link**

- EMI radiation of backplane communication module

- EMI radiations at  $2f_{Nyquist}$ ,  $4f_{Nyquist}$ , ... (e.g., 10 Gbps NRZ,  $f_{Nyquist}$  = 5 GHz)

- Ideal NRZ\* data has no frequency component @  $2f_{Nyquist}$ ,  $4f_{Nyquist}$ ,  $6f_{Nyquist}$  ...

- NRZ = non-return-to-zero

- Distorted differential NRZ signals

# **EMI Case Study in Backplane Link**

- EMI radiation of backplane communication module

- EMI radiations at  $2f_{Nyquist}$ ,  $4f_{Nyquist}$ , ... (e.g., 10 Gbps NRZ,  $f_{Nyquist}$  = 5 GHz)

- Ideal NRZ data has no frequency component @ 2f<sub>Nyquist</sub>, 4f<sub>Nyquist</sub>, 6f<sub>Nyquist</sub> ...

- Distorted differential NRZ signals

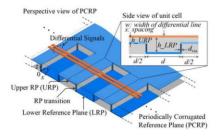

#### **Previous Works**

- CM noise dominates EMI radiation [1][6][7]

- "Passive" solutions for CM noise suppression

CM Filter/Choke, BW < 5 GHz

Common mode

Differential mode

[Murata, CM choke]

PCB structures (CM band-stop 5-10 GHz)

[Kim, TEMC 2016]

- Current solutions: "find and patch"

- How about <u>eliminating the CM noise source</u> of EMI radiation?

- Pioneer: <u>Acimovic</u>

- In DesignCon 2007, he first described the CM noise at 2f<sub>Nyquist</sub>

- No detailed analysis or verification

- Passive CM filter solution

- "Novel Band-Stop Common Mode Filter For High-Speed Digital Data Transmission"

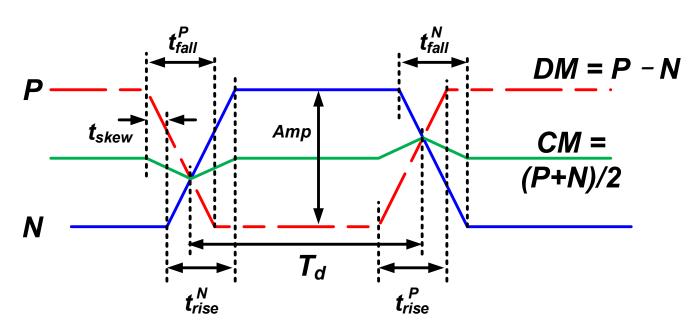

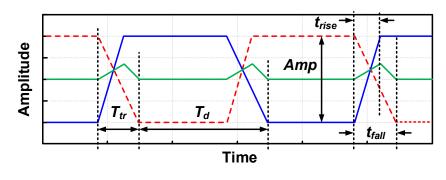

# What is the signal distortion that causes EMI radiation?

# Distorted Differential NRZ Signals

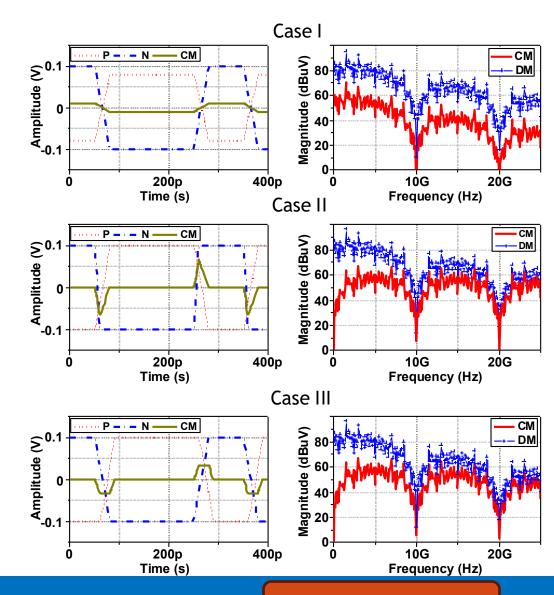

- 4 types of distortions in differential (diff.) NRZ data

- Case I: Inter-channel amplitude mismatch

- Case II: Inter-channel skew

- Case III: Inter-channel bandwidth mismatch (rise time / fall time)

- Case IV: Intra-channel edge mismatch (rise time / fall time)

# NRZ Signal Distortion: Case I/II/III

- Amplitude mismatch

- $-Amp_P=0.8\cdot Amp_N$

- Channel Skew

$$-t_{skew} = 10$$

ps

- Inter-channel bandwidth mismatch

- $-BW_P < BW_N$

- $t_{rise}^P = t_{fall}^P > t_{rise}^N = t_{fall}^N$

- Similarity

- Polarity of CM signal is data-dependent

- Broadband CM signal spectrum

- Linear distortion

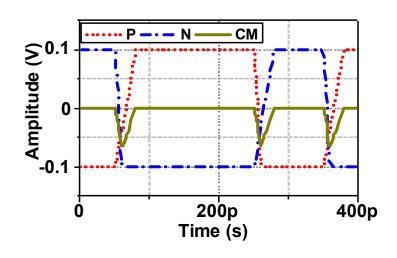

# NRZ Signal Distortion: Case IV

#### Case IV

- Intra-channel edge mismatch

- $t_{rise}^P = t_{rise}^N > t_{fall}^P = t_{fall}^N$

- Polarity of CM signal is dataindependent

- Large noise tone @ 10 GHz (2f<sub>Nyquist</sub>)

- **□** Non-linear distortion

- New noise tone @ 2fNyquist

- □ <u>'CM noise'</u> is specified to be the noise at 2f<sub>Nyquist</sub>

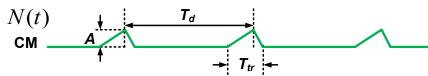

# Calculate the CM Noise @ 2f<sub>Nyquist</sub>

Fourier transform of CM signal, F(N(t))

$$-F(N(t)) = F(x(t) * c(t)) = F(x(t)) \cdot F(c(t))$$

• CM noise @ 2f<sub>Nyquist</sub>

$$-F(2f_{Nyquist}) = F(\frac{1}{T_d})$$

• A and  $T_{tr}$  is calculated as

$$-A = \frac{Amp}{2} \cdot \frac{\left|t_{rise} - t_{fall}\right|}{T_{tr}}$$

$$-T_{tr} = \max(t_{rise}, t_{fall})$$

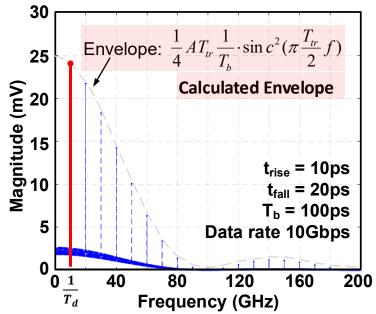

# Fourier Transform of CM Signal

CM signal

$$\|F_{N}(f)\| = \|X(f) \cdot F_{c}(f)\| = X(f) \cdot \|F_{c}(f)\| = \begin{cases} \frac{1}{4} A T_{tr} \frac{1}{T_{d}} \sin c^{2}(\frac{\pi}{2} T_{tr} f), & f = \frac{n}{T_{d}}, n \in \mathbb{Z} \\ \frac{1}{4} A T_{tr} \sqrt{\frac{1}{T_{d}}} \sin c^{2}(\frac{\pi}{2} T_{tr} f), & f \neq \frac{n}{T_{d}} \end{cases}$$

• MATLAB simulation (data rate:  $1/T_d >> 1$ ) vs. calculation results

# Calculation of CM Noise @ 2f<sub>Nyquist</sub>

•

$$F_N(2f_{Nyquist}) = \frac{1}{4} A \frac{T_{tr}}{T_d} \sin c^2 (\frac{\pi}{2} \cdot \frac{T_{tr}}{T_d}) = \frac{Amp}{8} \cdot \frac{|t_{rise} - t_{fall}|}{T_d} \cdot \sin c^2 (\frac{\pi}{2} \cdot \frac{T_{tr}}{T_d})$$

$$A = \frac{Amp}{2} \cdot \frac{\left|t_{rise} - t_{fall}\right|}{T_{tr}} \qquad 2f_{Nyquist} = \frac{1}{T_d}$$

When  $T_{tr} << T_d$

This term is about 1

- The CM noise is positively correlated with

- Data rate (10 years ago, Acimovic's work in DesignCon 2007 did not draw much attention)

- Signal swing

- Mismatch of rising and falling edges

$$F_N(2f_{Nyquist}) \propto A \cdot \frac{1}{T_d} \cdot T_{tr} \propto Amp \cdot |t_{rise} - t_{fall}| \cdot \frac{1}{T_d}$$

#### Conclusion

- CM noise dominates the EMI radiation

- Non-linear distortion generates the CM noise tone @ $2f_{Nyquist}$ ,  $4f_{Nyquist}$ ,  $6f_{Nyquist}$  ...

- The CM noise at  $2f_{Nyquist}$  is <u>largest</u>

- The CM noise increases noise floor

The CM noise is a data-dependent random process

$$F_N(2f_{Nyquist}) \propto A \cdot \frac{1}{T_d} \cdot \boxed{T_{tr}} \propto Amp \cdot |t_{rise} - t_{fall}| \cdot \frac{1}{T_d}$$

Sharp data edge (smaller  $T_{tr}$ ) reduces the EMI-related CM noise

# How is the distortion generated?

Non-linearity of high-speed I/O driver

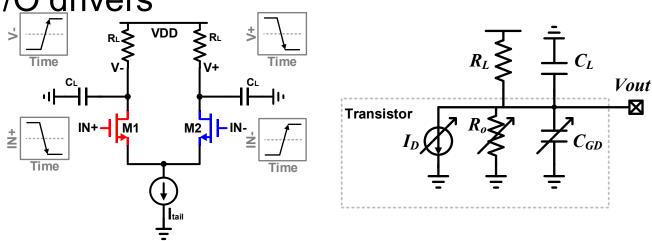

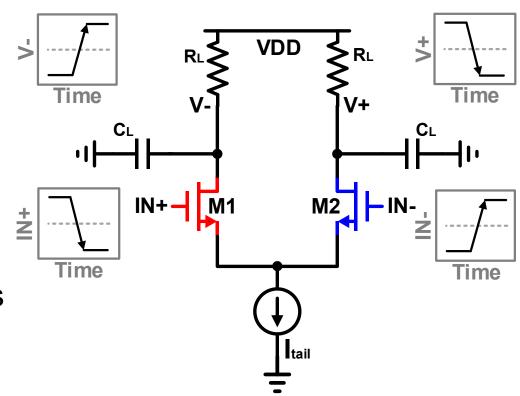

#### **CM Noise in CML Driver**

Current mode logic (CML) circuit are widely used for high-speed I/O drivers

- Equivalent circuits of M1 and M2

- Rising/falling edge calculation:  $V_{out} = V_{initial} + I_D \cdot R_{total} (1 e^{-\frac{1}{R_{total}C_{total}}t})$

- $-I_D$ ,  $R_o$  and  $C_{GD}$  varies with biasing voltage ( $V_{GS}$  and  $V_{DS}$ )

- Mismatch of rising and falling edges is a function of  $V_{GS}$  and  $V_{DS}$   $\left|t_{rise}-t_{fall}\right|=t(\Delta V_{GS},\Delta V_{DS})$

#### **CM Noise in CML Driver**

$$egin{aligned} \left| t_{rise} - t_{fall}

ight| &= t(\Delta V_{GS}, \Delta V_{DS}) \end{aligned}$$

$F_N(2f_{Nyquist}) \propto Amp \cdot \left| t_{rise} - t_{fall}

ight| \cdot rac{1}{T_d}$

- Completely reversed voltage variations

- M1:  $V_{GS}$  ↓,  $V_{DS}$  ↑

- M2:  $V_{GS}$  ↑,  $V_{DS}$  ↓

- Intrinsic mismatch of rising and falling edges

- Not able to eliminate the CM noise

- Optimize  $V_{GS}$  to minimize  $\left|t_{rise} t_{fall}\right|$ ?

- Reduce the amplitude Amp?

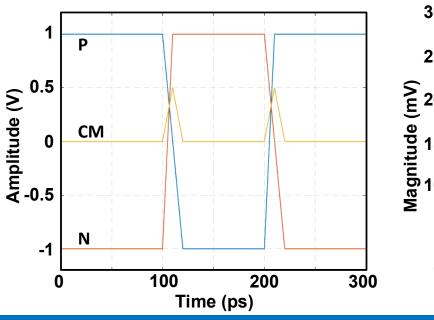

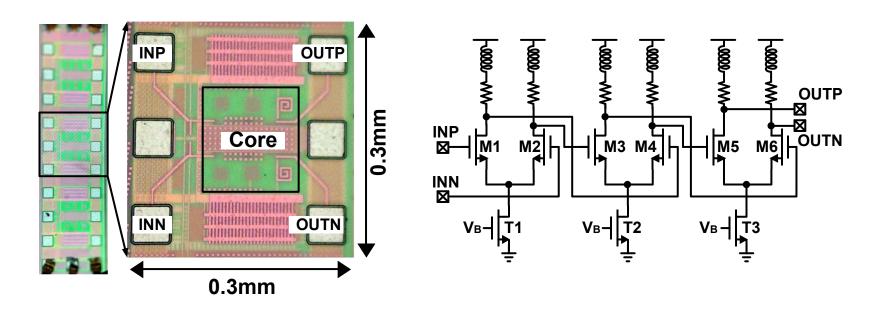

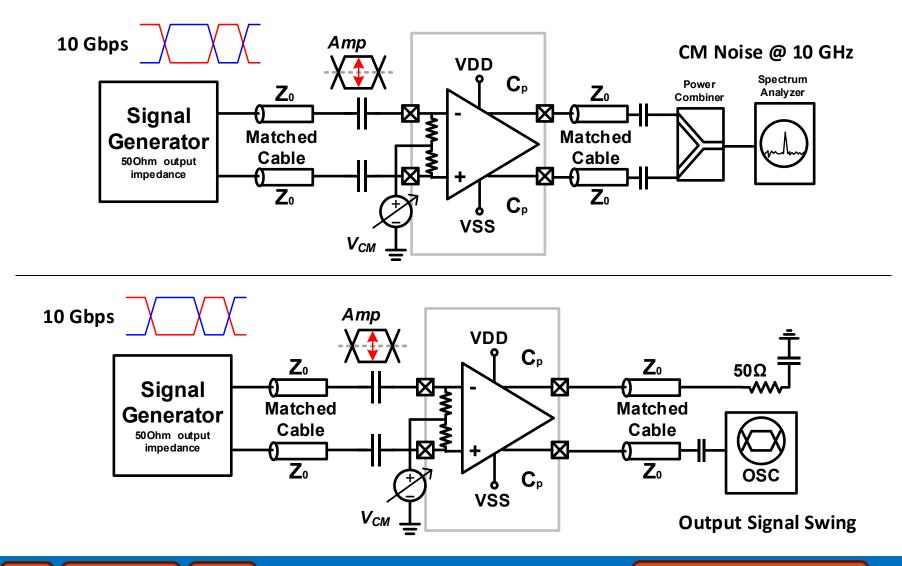

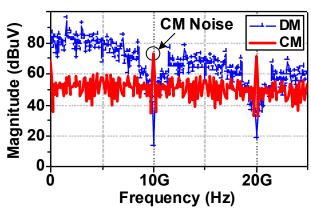

# Measurement & Verification

A test chip in a 65nm CMOS process

# **Test Chip: CML Driver Circuit**

- Test chip information

- 3-stage cascaded CML driver in a 65nm CMOS process

- Measurements

- Output CM noise & output signal

### Measurement: CM Noise & Output Signal

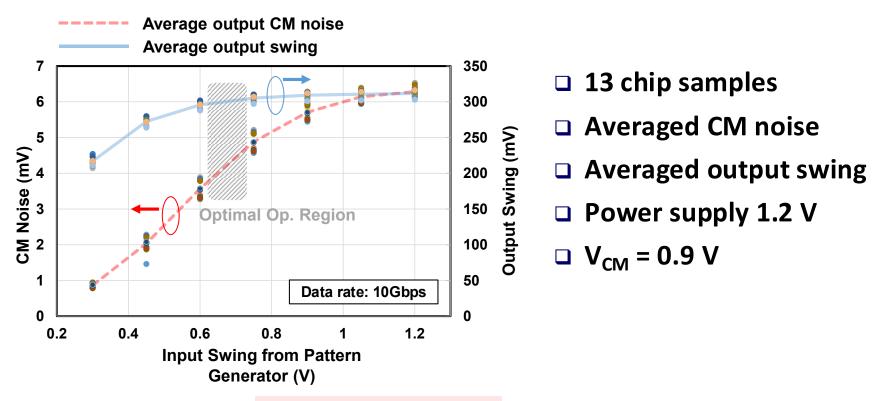

# CM Noise vs. Signal Amplitude

- Positive correlation:  $F_N(2f_{Nyquist}) \propto Amp$

- Input swing ↑, output swing saturates faster than CM noise

$$\left|t_{rise} - t_{fall}\right| = t(\Delta V_{GS}, \Delta V_{DS})$$

90% amplitude → 57% CM noise (amplitude back-off)

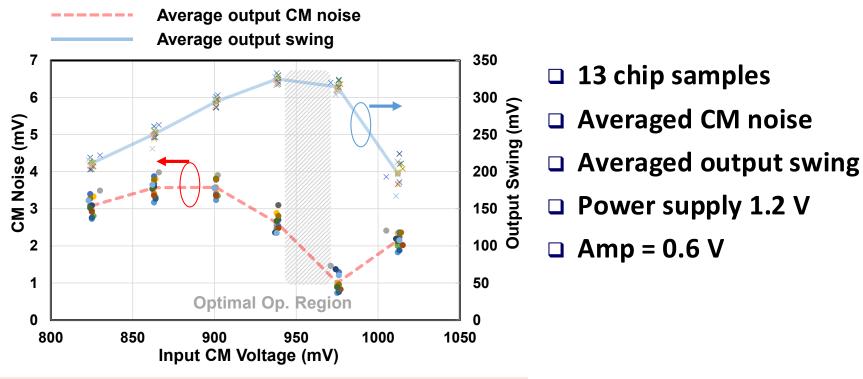

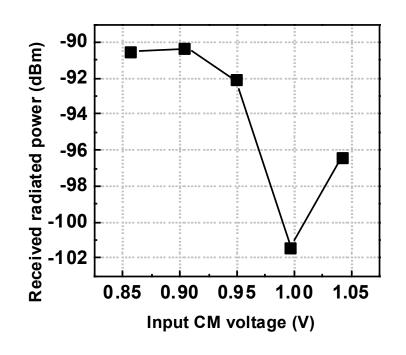

# CM Noise vs. Biasing Voltage

•

$$\left|t_{rise} - t_{fall}\right| = t(\Delta V_{GS}, \Delta V_{DS})$$

,  $F_N(2f_{Nyquist}) \propto \left|t_{rise} - t_{fall}\right|$

- Optimal Input biasing voltage ( $V_{GS}$ ) to reduce CM noise

- Balancing the rising and falling edge:  $\left|t_{rise}-t_{fall}\right|$   $\downarrow$

- Providing sufficient output swing for communication quality

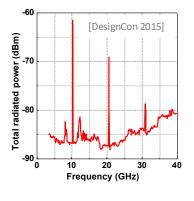

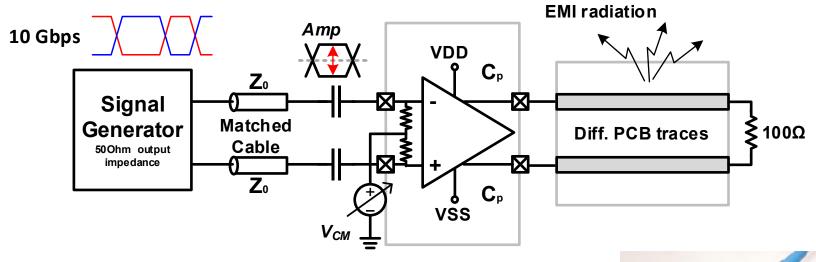

# Is the EMI radiation reduced?

**Definitely, it is.**

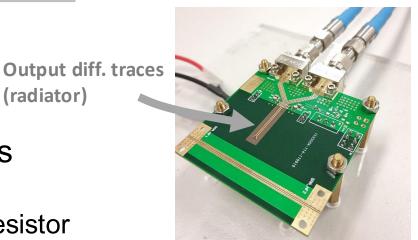

#### **EMI Radiation Measurement**

(radiator)

- EMI Measurement setup

- 10 Gbps diff. PRBS input

- Differential output PCB traces

- PCB trace  $Z_0 = 50$  Ohm

- 100 Ohm far-end termination resistor

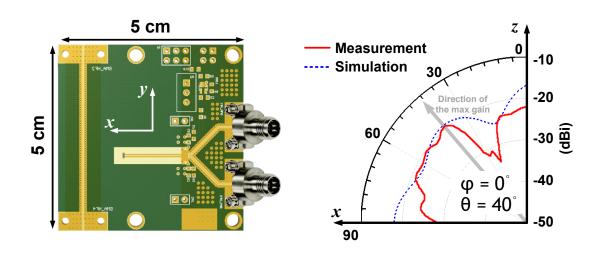

#### Where to Place the Antenna?

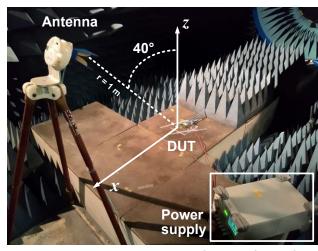

Antenna is used to collect radiated EMI emission

Testing site in an anechoic chamber

- Maximum far-field radiation

- CM radiation pattern, maximum gain:  $\varphi = 0^{\circ}$ ,  $\theta = 40^{\circ}$

- Far-field Fraunhofer distance:  $r \ge \frac{2d^2}{\lambda} = 72cm$ , so r = 1m

- d = 10.4 cm, the maximum dimension of antenna;  $\lambda$  = 3 cm, 10 GHz wavelength

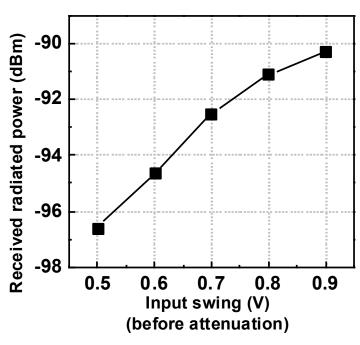

#### **EMI Radiation Measurement Result**

Signal swing vs. EMI radiation

$$EMI \propto F_N(2f_{Nyquist}) \propto Amp$$

- **□** Biasing voltage vs. EMI radiation

- Optimal biasing condition  $t_{rise} t_{fall} = t(\Delta V_{GS}, \Delta V_{DS})$

$$EMI \propto F_N(2f_{Nyquist}) \propto \left| t_{rise} - t_{fall} \right|$$

CM noise dominates EMI radiation

#### Conclusion

- CM noise is intrinsically existed in I/O buffers

- Non-linear variation during large-signal operation in transistors

- Given a certain data rate, CM noise is positively correlated to

- Signal swing

$$F_N(2f_{Nyquist}) \propto Amp$$

- Edge mismatch

$$F_N(2f_{Nyquist}) \propto |t_{rise} - t_{fall}|$$

- Suppress CM noise to reduce EMI radiation

- Limit the signal swing and do not over drive the circuit

- Optimize the biasing voltage to balance data edges

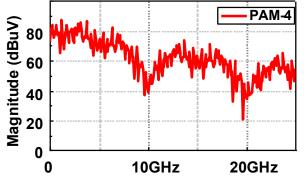

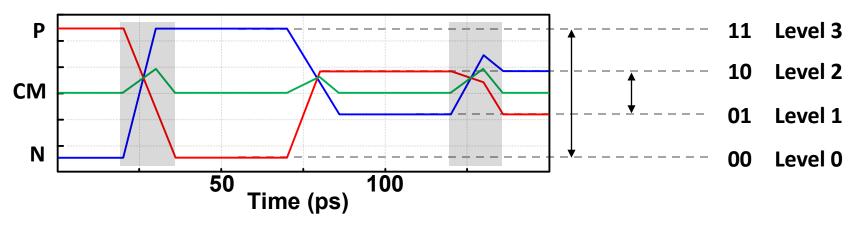

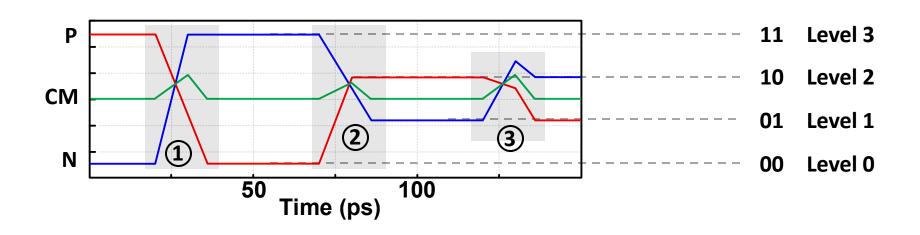

# A more complicated case: PAM-4

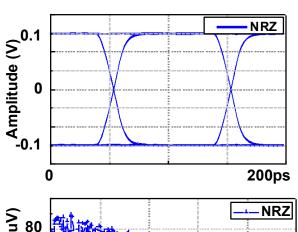

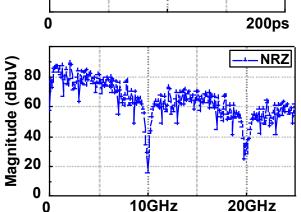

#### From NRZ to PAM-4

- □ Eye-diagram of 10 GB PAM-4

- Doubled data rate: 20 Gbps

- 4 data levels (00, 01, 10, 11)

- 16 data transitions

- Higher bandwidth efficiency

- Eye-diagram of 10 GB NRZ

- 10 Gbps

- 2 data levels (0, 1)

- 4 data transitions

- □ Eye-diagram: 10Gbps NRZ vs. 20Gbps PAM-4

- Four possible data levels per symbol, data rate is doubled

- Higher bandwidth efficiency

- Key solution for next 200/400 GbE communication

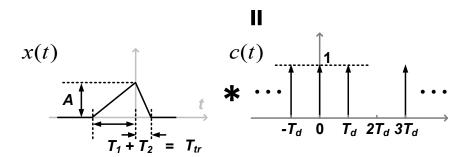

# EMI Issue in Diff. PAM-4 Signals

#### □ PAM-4

- □ Intra-Channel edge mismatch

- Similar to differential NRZ signals

PIT

•  $t_{rise}^P = t_{rise}^N = 25p > t_{fall}^P = t_{fall}^N = 10ps$

# How to describe the CM noise in PAM-4 systems?

#### From NRZ to PAM-4

Equation for NRZ

$$F_N(2f_{Nyquist}) = \frac{Amp}{8} \cdot \frac{|t_{rise} - t_{fall}|}{T_d} \cdot \sin c^2 \left(\frac{\pi}{2} \cdot \frac{T_{tr}}{T_d}\right)$$

- Upgraded equation for PAM-4

- Data period  $T_d \rightarrow$  Symbol period  $T_s$

- Mismatch of rise and fall time depends on circuit physical structure

- Amp → expected value of amplitude, E(Amp)

$$F_N(2f_{Nyquist}) = \frac{E(Amp)}{8} \cdot \frac{|t_{rise} - t_{fall}|}{T_s} \cdot \sin c^2 \left(\frac{\pi}{2} \cdot \frac{T_{tr}}{T_s}\right)$$

How to calculate E(Amp)?

# CM Noise vs. "Amplitude"

- Conclusions for NRZ

- CM noise is positively correlated to amplitude

$$F_N(2f_{Nyquist}) \propto Amp$$

- PAM-4

- CM noise is not positively correlated to amplitude

- Data transition between Level 0 and Level 3

- Data transition between Level 1 and Level 2

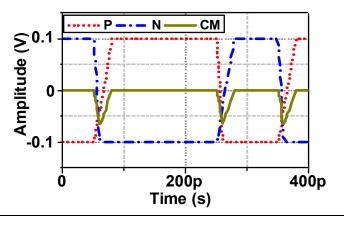

# CM Noise of PAM-4 Signals

- Data transition:  $00 \rightarrow 11$

- MSB:  $0 \rightarrow 1$

- LSB:  $0 \rightarrow 1$

- $DM: +DM_{MSB} + DM_{LSB}$

$CM: +CM_{MSB} + CM_{LSB}$

- Data transition:  $01 \rightarrow 10$

- MSB:  $0 \rightarrow 1$

- LSB:1  $\rightarrow$  0

- $\square$  DM:  $+DM_{MSB} DM_{LSB}$

$\Box$  CM: + $CM_{MSB}$  +  $CM_{LSB}$

# **CM Noise of PAM-4 Signals**

- CM noise is correlated to data transitions

- Switching distance (SD) to describe <u>how many bits</u> are <u>switched</u>

$$SD(A,B) = \sum_{k} W_{k} \cdot (A[k] \oplus B[k]), W_{k} = 2^{k-1}$$

$$N_{CM} \propto SD$$

$SD(00,11) = SD(01,10) = MSB + LSB$

CM noise is positively correlated to SD

PIT

# $E(Amp) \longrightarrow E(SD)$

**Look back to the generation of PAM-4 signals**

# E(SD) in Different PAM-4 Architectures

Binary-scaled (BS)

| MSB | LSB |                                |

|-----|-----|--------------------------------|

| 0   | 0   | $V_{\scriptscriptstyle PAM-4}$ |

| 0   | 1   | $=2V_{MSB}+V_{LSB}$            |

| 1   | 0   | -2, $MSB$                      |

| 1   | 1   |                                |

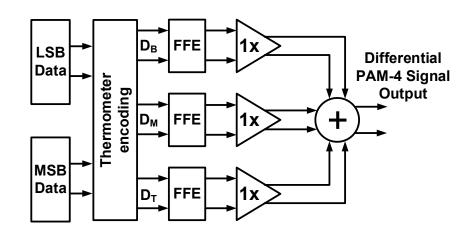

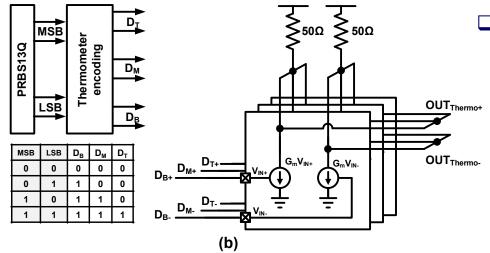

□ Thermometer-coded (TC)

| D <sub>B</sub> | D <sub>M</sub> | DT |                 |

|----------------|----------------|----|-----------------|

| 0              | 0              | 0  | $V_{\it PAM-4}$ |

| 1              | 0              | 0  | $=V_{DT}$       |

| 1              | 1              | 0  | $-$ / $_{DT}$   |

| 1              | 1              | 1  |                 |

$$V_{PAM-4} = V_{DT} + V_{DM} + V_{DB}$$

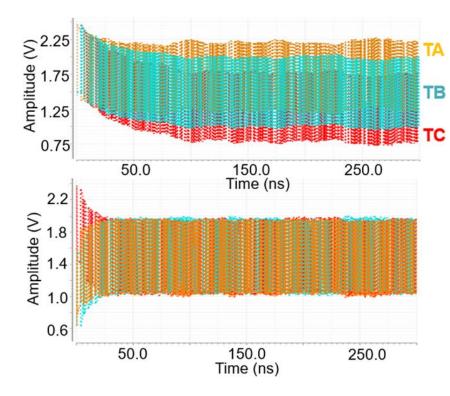

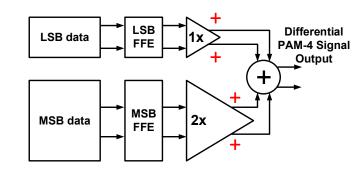

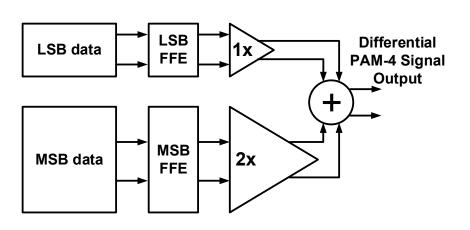

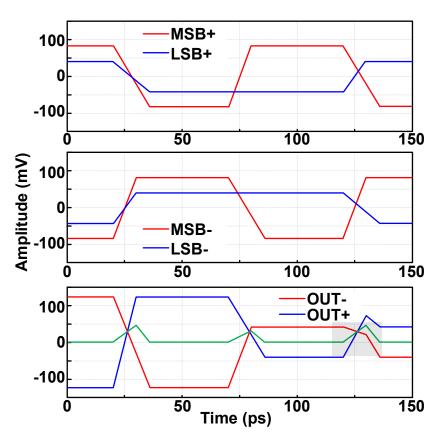

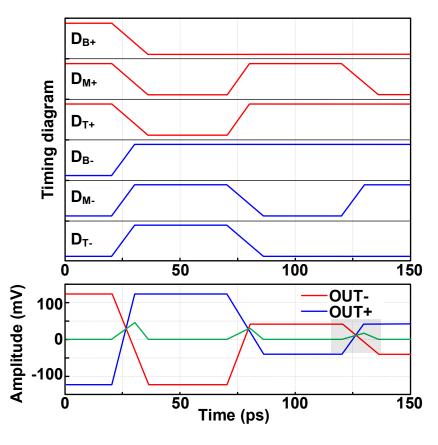

#### **Transient Waveform: BS vs. TC**

Binary-scaled (BS)

$$-V_{PAM-4} = 2V_{MSB} + V_{LSB}$$

□ Thermometer-coded (TC)

•

$$V_{PAM-4} = V_{DT} + V_{DM} + V_{DB}$$

• Smaller CM noise?

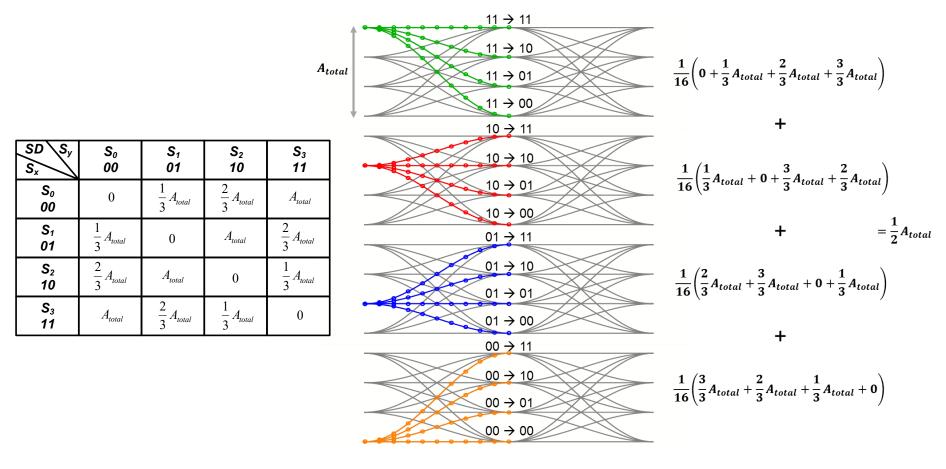

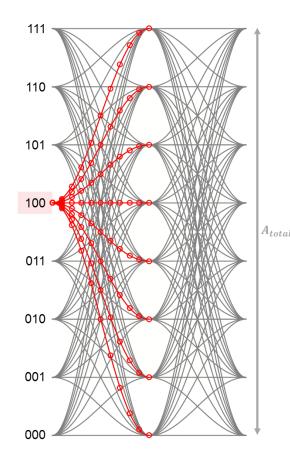

# E(SD) of Binary-Scaled PAM-4

•

$$E(SD) = \sum_{n=0}^{3} \sum_{m=0}^{3} p_{n,m} \cdot SD(S_n, S_m) = \frac{1}{16} \cdot \sum_{n=0}^{3} \sum_{m=0}^{3} SD(S_n, S_m) = \frac{1}{2} A_{total}$$

# E(SD) of Thermometer-Coded PAM-4

| $SD S_y$              | S <sub>0</sub><br>000   | S <sub>1</sub><br>001   | S <sub>2</sub><br>011  | S₃<br>111               |  |  |

|-----------------------|-------------------------|-------------------------|------------------------|-------------------------|--|--|

| S <sub>0</sub><br>000 | 0                       | $\frac{1}{3} A_{total}$ | $\frac{2}{3}A_{total}$ | $A_{total}$             |  |  |

| S₁<br>001             | $\frac{1}{3} A_{total}$ | 0                       | $\frac{1}{3}A_{total}$ | $\frac{2}{3}A_{total}$  |  |  |

| S <sub>2</sub><br>011 | $\frac{2}{3}A_{total}$  | $\frac{1}{3}A_{total}$  | 0                      | $\frac{1}{3} A_{total}$ |  |  |

| S₃<br>111             | $A_{total}$             | $\frac{2}{3}A_{total}$  | $rac{1}{3}A_{total}$  | 0                       |  |  |

•

$$E(SD) = \sum_{n=0}^{3} \sum_{m=0}^{3} p_{n,m} \cdot SD(S_n, S_m) = \frac{1}{16} \cdot \sum_{n=0}^{3} \sum_{m=0}^{3} SD(S_n, S_m) = \frac{5}{12} A_{total}$$

# E(SD) of Binary-Scaled PAM-8

|     | 111           | 110           | 101           | 100                    | 011           | 010           | 001           | 000           |

|-----|---------------|---------------|---------------|------------------------|---------------|---------------|---------------|---------------|

| 111 | 0             | $\frac{1}{7}$ | $\frac{2}{7}$ | $\frac{3}{7}$          | $\frac{4}{7}$ | 5<br>7        | $\frac{6}{7}$ | $\frac{7}{7}$ |

| 110 | $\frac{1}{7}$ | 0             | $\frac{3}{7}$ | $\frac{2}{7}$          | 5<br>7        | $\frac{4}{7}$ | $\frac{7}{7}$ | $\frac{6}{7}$ |

| 101 | $\frac{2}{7}$ | $\frac{3}{7}$ | 0             | $0 \qquad \frac{1}{7}$ |               | $\frac{7}{7}$ | $\frac{4}{7}$ | 5<br>7        |

| 100 | $\frac{3}{7}$ | $\frac{2}{7}$ | $\frac{1}{7}$ | 0                      | $\frac{7}{7}$ | $\frac{6}{7}$ | 5<br>7        | $\frac{4}{7}$ |

| 011 | $\frac{4}{7}$ | 5<br>7        | $\frac{6}{7}$ | $\frac{7}{7}$          | 0             | $\frac{1}{7}$ | $\frac{2}{7}$ | $\frac{3}{7}$ |

| 010 | 5<br>7        | $\frac{4}{7}$ | $\frac{7}{7}$ | 6<br>7                 | $\frac{1}{7}$ | 0             | $\frac{3}{7}$ | $\frac{2}{7}$ |

| 001 | 6<br>7        | $\frac{7}{7}$ | $\frac{4}{7}$ | 5<br>7                 | $\frac{2}{7}$ | $\frac{3}{7}$ | 0             | $\frac{1}{7}$ |

| 000 | $\frac{7}{7}$ | 6<br>7        | 5<br>7        | $\frac{4}{7}$          | $\frac{3}{7}$ | $\frac{2}{7}$ | $\frac{1}{7}$ | 0             |

$$SD = \sum_{n=0}^{7} \sum_{m=0}^{7} p_{n,m} \cdot SD(S_n, S_m) = \frac{1}{64} \sum_{n=0}^{7} \sum_{m=0}^{7} \frac{m}{7} A_{total} = \frac{1}{2} A_{total}$$

3-bit binary weighted

$$-V_{PAM-8} = 4V_{B2} + 2V_{B1} + V_{B0}$$

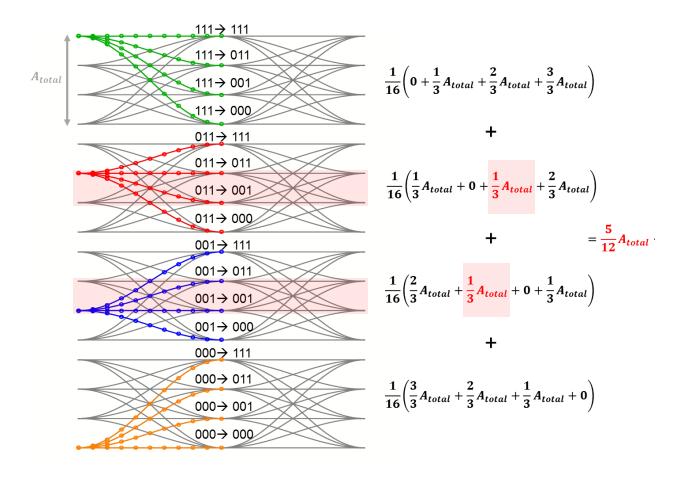

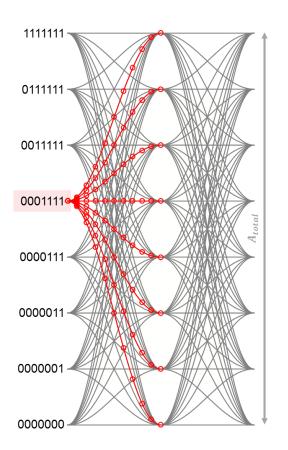

# E(SD) of Thermometer-Coded PAM-8

|         | 1111111       | 0111111       | 0011111       | 0001111       | 0000111       | 0000011        | 0000001       | 0000000       |

|---------|---------------|---------------|---------------|---------------|---------------|----------------|---------------|---------------|

| 1111111 | 0             | $\frac{1}{7}$ | $\frac{2}{7}$ | $\frac{3}{7}$ | $\frac{4}{7}$ | $\frac{5}{7}$  | $\frac{6}{7}$ | $\frac{7}{7}$ |

| 0111111 | $\frac{1}{7}$ | 0             | $\frac{1}{7}$ | $\frac{2}{7}$ | $\frac{3}{7}$ | $\frac{4}{7}$  | $\frac{5}{7}$ | $\frac{6}{7}$ |

| 0011111 | $\frac{1}{7}$ | $\frac{2}{7}$ | 0             | $\frac{1}{7}$ | $\frac{2}{7}$ | $\frac{3}{7}$  | $\frac{4}{7}$ | 5<br>7        |

| 0001111 | $\frac{1}{7}$ | $\frac{2}{7}$ | $\frac{3}{7}$ | 0             | $\frac{1}{7}$ | $\frac{2}{7}$  | $\frac{3}{7}$ | $\frac{4}{7}$ |

| 0000111 | $\frac{1}{7}$ | $\frac{2}{7}$ | $\frac{3}{7}$ | $\frac{4}{7}$ | 0             | $\frac{1}{7}$  | $\frac{2}{7}$ | $\frac{3}{7}$ |

| 0000011 | $\frac{1}{7}$ | $\frac{2}{7}$ | _   _   0     | _   _   0     | _             | _   _   ()   _ | $\frac{1}{7}$ | $\frac{2}{7}$ |

| 0000001 | $\frac{1}{7}$ | $\frac{2}{7}$ | $\frac{3}{7}$ | $\frac{4}{7}$ | $\frac{5}{7}$ | 5 6 0          |               | $\frac{1}{7}$ |

| 0000000 | $\frac{1}{7}$ | $\frac{2}{7}$ | $\frac{3}{7}$ | $\frac{4}{7}$ | $\frac{5}{7}$ |                |               | 0             |

$$SD = \sum_{n=0}^{7} \sum_{m=0}^{7} p_{n,m} \cdot SD(S_n, S_m) = \frac{1}{64} \sum_{k=0}^{7} \left( \sum_{x=0}^{k} \frac{x}{7} A_{total} + \sum_{y=k}^{7} \frac{y-k}{7} A_{total} \right) = \frac{3}{8} A_{total}$$

7 data eyes → 7-bit thermometer code

$$-V_{PAM-8} = V_{D6} + V_{D5} + V_{D4} + V_{D3} + V_{D2} + V_{D1} + V_{D0}$$

# E(SD) Calculation Summary

|                                   | PA                     | M-4                     | PA                     | M-8                    | <b>PAM-16</b>          |                          |  |

|-----------------------------------|------------------------|-------------------------|------------------------|------------------------|------------------------|--------------------------|--|

| Topology                          | $\mathbf{BS}^*$        | BS* TC# BS              |                        | TC                     | BS                     | TC                       |  |

| Baud rate (GB)                    | 10                     | 10                      | 10                     | 10                     | 10                     | 10                       |  |

| Data rate (Gbps)                  | 20                     | 20                      | 30                     | 30                     | 40                     | 40                       |  |

| Double Nyquist<br>frequency (GHz) | 10                     | 10                      | 10                     | 10                     | 10                     | $10$ $A_{total}$         |  |

| Total Signal<br>Amplitude         | $A_{total}$            | $A_{total}$             | $A_{total}$            | $A_{total}$            | $A_{total}$            |                          |  |

| Average SD                        | $\frac{1}{2}A_{total}$ | $\frac{5}{12}A_{total}$ | $\frac{1}{2}A_{total}$ | $\frac{3}{8}A_{total}$ | $\frac{1}{2}A_{total}$ | $\frac{17}{48}A_{total}$ |  |

| Normalized<br>CM Noise            |                        |                         | 1                      | 0.75                   | 1                      | 0.71                     |  |

<sup>\*</sup> BS stands for binary-scaled

- With same symbol rate (same  $T_s$ )

- BS PAM-4/8/16 have same *E(SD)* and same CM noise

- TC PAM-4/8/16 have intrinsically smaller CM noise

<sup>#</sup> TC stands for thermometer-coded

# **Upgraded CM Noise Equation**

$$N(2f_{Nyquist}) = \frac{1}{8} \frac{\beta_{S} \cdot Amp}{T_{S}} \frac{\left|t_{rise} - t_{fall}\right|}{T_{S}} \cdot \sin c^{2} \left(\frac{\pi}{2} \cdot \frac{T_{tr}}{T_{S}}\right)$$

Introducing system-architecture coefficient (SAC),

$$\beta_{S} = \frac{SD_{PAM-2^{k}}^{T}}{SD_{PAM-2^{k}}^{B}} = \frac{\frac{1}{2^{2k}} \sum_{n=0}^{2^{k}-1} (\sum_{x=0}^{n} \frac{x}{2^{k}-1} + \sum_{y=n}^{2^{k}-1} \frac{y-n}{2^{k}-1}) A_{total}}{\frac{1}{2} A_{total}}$$

Normalized CM noise to the CM noise in binary-scaled

systems

| $oldsymbol{eta}_{\scriptscriptstyle S}$ | PAM-4 | PAM-8 | PAM-16 |

|-----------------------------------------|-------|-------|--------|

| Binary-scaled                           | 1     | 1     | 1      |

| Thermometer-coded                       | 0.83  | 0.75  | 0.71   |

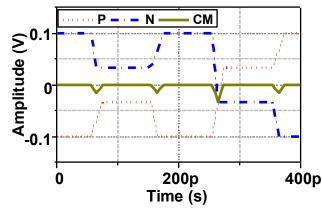

# Behavior- and transistorlevel simulation results

**PAM-4 and PAM-8 CML Drivers**

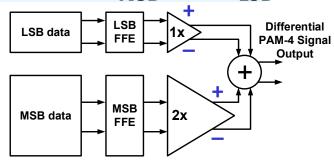

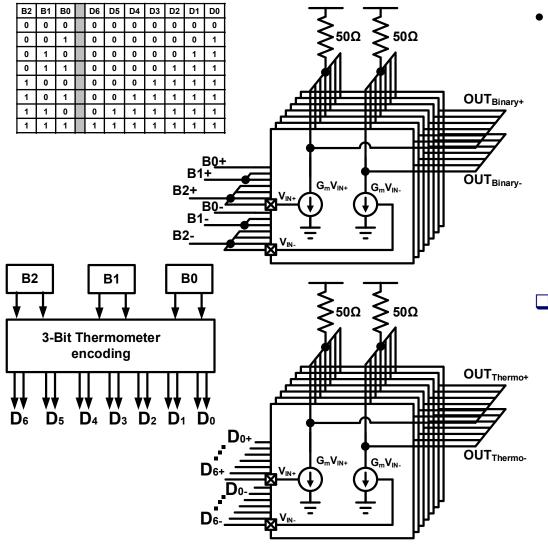

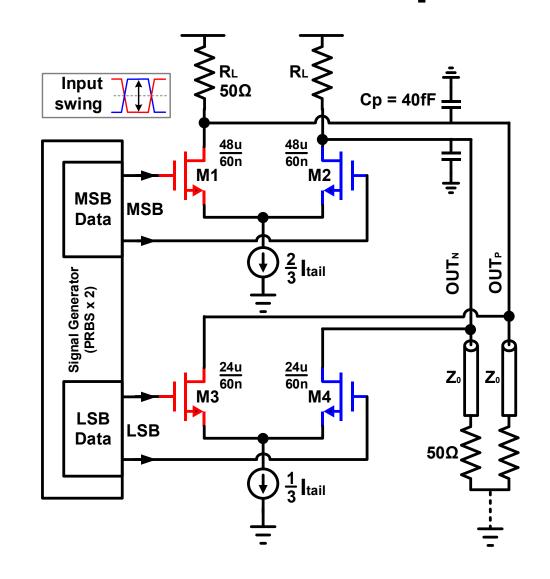

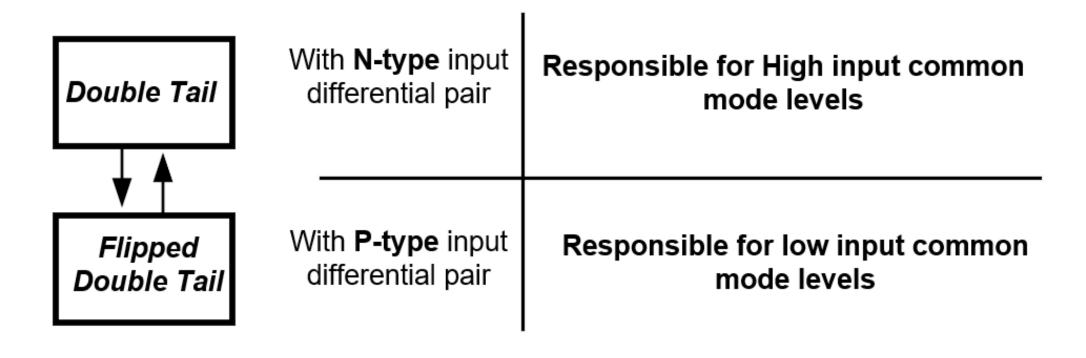

#### **PAM-4 Behavior-Level Simulations**

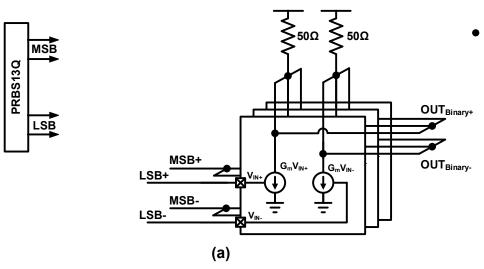

- Binary-scaled PAM-4

- 3 identical slices

- 2 for MSB, 1 for LSB

- $V_o = G_m R_o (2V_{MSB} + V_{LSB})$

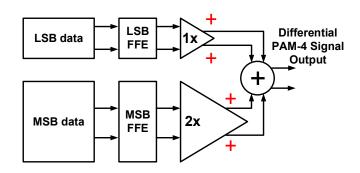

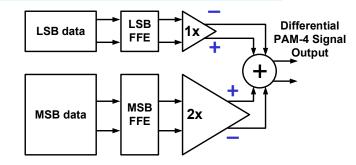

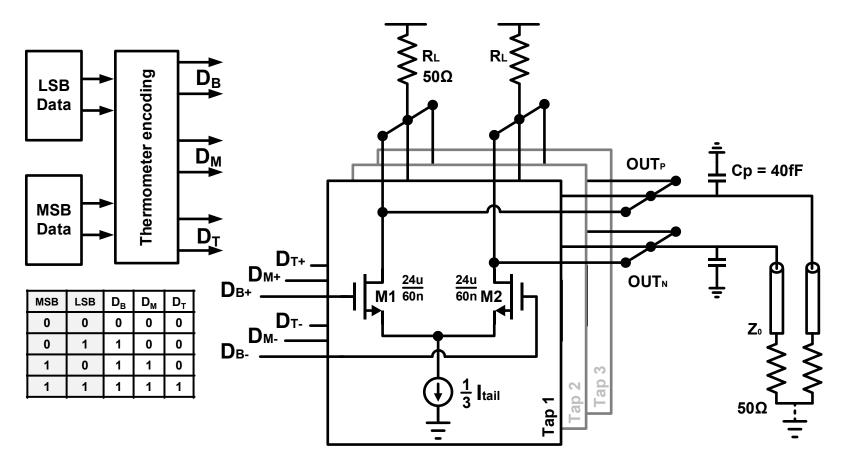

#### Thermometer-coded PAM-4

- 3 identical slices

- 1 for D<sub>T</sub>, 1 for D<sub>M</sub>, and 1 for D<sub>B</sub>

- $V_0 = G_m R_0 (V_{DT} + V_{DM} + V_{DR})$

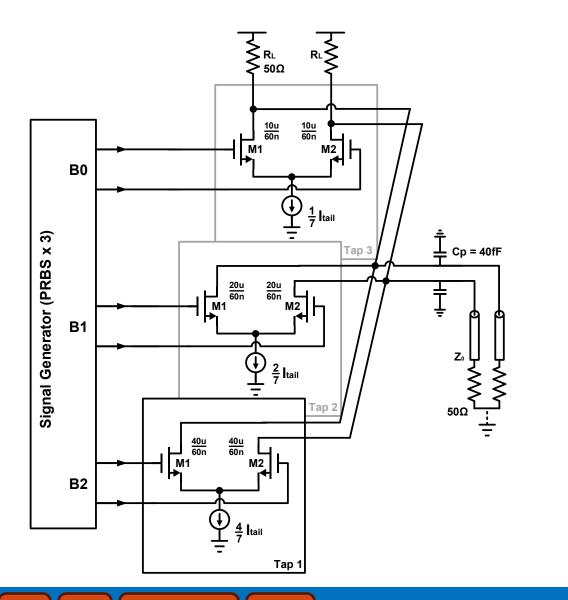

#### **PAM-8 Behavior-Level Simulations**

- Binary-scaled PAM-8

- 7 identical slices

- 4 for B2, 2 for B1, and 1 for B0

- $V_o = G_m R_o (4V_{B2} + 2V_{B1} + V_{B0})$

- Thermometer-coded PAM-8

- 7 identical slices

- Evenly distributed

- $V_o = G_m R_o (V_{D6} + V_{D5} + \cdots V_{D0})$

### **Summary of Simulation Results**

|                                    | PA              | M-4   | PA    | M-8   |  |

|------------------------------------|-----------------|-------|-------|-------|--|

| Topology                           | $\mathbf{BS}^*$ | TC#   | BS    | TC    |  |

| Baud rate (GB)                     | 10              | 10    | 10    | 10    |  |

| Data rate (Gbps)                   | 20              | 20    | 30    | 30    |  |

| Double Nyquist<br>frequency (GHz)  | 10              | 10    | 10    | 10    |  |

| Simulation time (nS)               | 800             | 800   | 800   | 800   |  |

| Total amplitude (mV)               | 252             | 252   | 252   | 252   |  |

| Rising/falling edge (ps)           | 11/10           | 11/10 | 11/10 | 11/10 |  |

| Simulated<br>CM noise @ 20GHz (mV) | 2.41            | 1.99  | 2.41  | 1.81  |  |

| Normalized CM noise                | 1               | 0.826 | 1     | 0.751 |  |

<sup>\*</sup> BS stands for binary-scaled

# TC stands for thermometer-coded

| $oldsymbol{eta}_{\scriptscriptstyle S}$ | PAM-4 | PAM-8 | PAM-16 |

|-----------------------------------------|-------|-------|--------|

| Binary-scaled                           | 1     | 1     | 1      |

| Thermometer-coded                       | 0.83  | 0.75  | 0.71   |

- Consistent with the previous calculations

- Error is caused by the <u>pseudo-randomness</u> of PRBS13Q

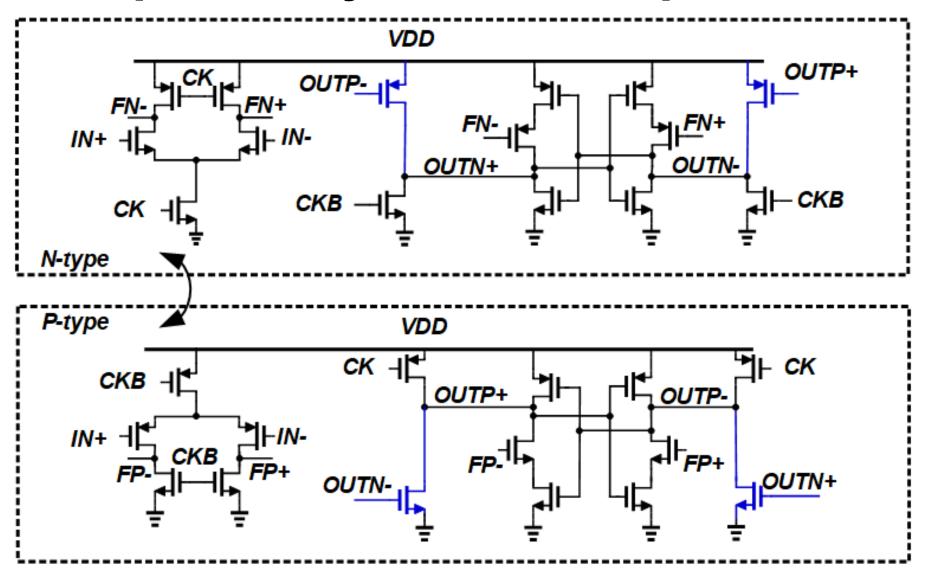

#### **BS PAM-4 Circuit Simulation Setup**

- Verilog-A signal generator

- Ideal non-distorted input MSB and LSB signals

- CML core circuit

- 65nm CMOS process

- Output transmission line

- S-parameter 2-port blocks

- Current ratio

- -MSB:LSB = 2:1

#### TC PAM-4 Circuit Simulation Setup

- Ideal input thermometer-code signals

- Current ratio, 1:1:1

# **BS & TC PAM-8 Circuit Simulation Setups**

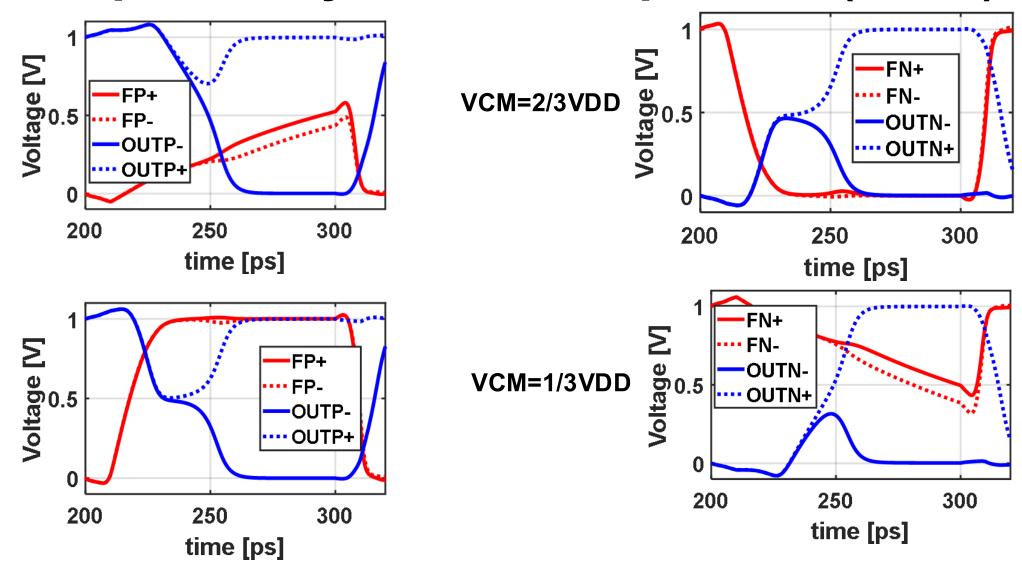

#### **Transistor-Level Simulation Results**

|                           | ı             | PAM-4 BS | ,*<br>) | PAM-4 TC# |        |             | PAM-8 BS |        |         | PAM-8 TC |       |       |       |

|---------------------------|---------------|----------|---------|-----------|--------|-------------|----------|--------|---------|----------|-------|-------|-------|

| Baud rate (GB)            |               | 10       |         |           | 10     |             |          |        | 10      |          | 10    |       |       |

| Data rate (Gbps)          | 20            |          |         |           | 20     |             |          | 30     |         |          | 30    |       |       |

| Double Nyquist frequency  | 10 GHz 10 GHz |          |         |           | 10 GHz |             |          | 10 GHz |         |          |       |       |       |

| Transistor sizing         |               | 48u+24u  |         | 24u x 3   |        | 40u+20u+10u |          |        | 10u x 7 |          |       |       |       |

| Process corner            | FF            | TT       | SS      | FF        | TT     | SS          |          | FF     | TT      | SS       | FF    | TT    | SS    |

| DC current (mA)           | 18.5          | 17.7     | 16.8    | 18.5      | 17.7   | 16.8        |          | 18.5   | 17.7    | 16.8     | 18.5  | 17.7  | 16.8  |

| Input swing (V)           | 0.2           | 0.2      | 0.2     | 0.2       | 0.2    | 0.2         |          | 0.2    | 0.2     | 0.2      | 0.2   | 0.2   | 0.2   |

| Input biasing voltage (V) | 0.85          | 0.85     | 0.85    | 0.85      | 0.85   | 0.85        |          | 0.85   | 0.85    | 0.85     | 0.85  | 0.85  | 0.85  |

| Output swing (mV)         | 214.9         | 234.7    | 253.7   | 214.8     | 234.7  | 253.6       |          | 212.1  | 231.7   | 250.7    | 212.1 | 231.7 | 250.7 |

| CM Noise<br>@ 10GHz (mV)  | 1.34          | 1.86     | 3.01    | 0.92      | 1.39   | 2.13        |          | 1.41   | 1.93    | 3.04     | 0.96  | 1.32  | 2.11  |

- Same process corner, symbol rate, driver size, power, and signal swing

- > Binary-scaled drivers have same CM noise

- > Thermometer-coded systems drivers smaller CM noise

- Consistent with prediction

#### **Conclusions**

$$N(2f_{Nyquist}) = \frac{1}{8} \beta_{S} \cdot Amp \frac{\left| t_{rise} - t_{fall} \right|}{T_{s}} \cdot \sin c^{2} \left( \frac{\pi}{2} \cdot \frac{T_{tr}}{T_{s}} \right)$$

- Reduce EMI radiation of backplane links with a certain <u>data rate</u>

- Limit amplitude and do not over drive the circuit  $Amp \downarrow$

- Optimize circuit biasing condition to balance rise and fall time  $|t_{rise}-t_{fall}|$   $\downarrow$

- Use higher-order modulations to lower symbol rate  $T_s \uparrow$

- E.g., from NRZ to PAM-4, T<sub>s</sub> is doubled

- When designing PAM-4/8 systems, use thermometer-coded topology to reduce CM noise  $\beta_s \downarrow$

# Tx Reference (OWL)

- F. Chen, C. Zhang, L. Wang, Q. Pan and C. P. Yue, "A 2.05-pJ/b 56-Gb/s PAM-4 VCSEL Transmitter with Piecewise Nonlinearity Compensation and Asymmetric Equalization in 40-nm CMOS," ESSCIRC 2023- IEEE 49th European Solid State Circuits Conference (ESSCIRC), Lisbon, Portugal, 2023, pp. 373-376.

- C. Zhang, F. Chen and C. P. Yue, "A 56-Gb/s PAM-4 Transmitter Using Silicon Photonic Microring Modulator in 40nm CMOS," 2022 IEEE 65th International Midwest Symposium on Circuits and Systems (MWSCAS), Fukuoka, Japan, 2022, pp. 1-4.

- R. Azmat, L. Wang, K. Q. Maqbool, C. Wang and C. P. Yue, "Sensing and Cancellation Circuits for Mitigating EMI-Related Common Mode Noise in High-Speed PAM-4 Transmitter," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 11, pp. 4545-4555, Nov. 2021.

- K. Q. Maqbool, D. Luo, X. Luo, H. Yu and C. P. Yue, "EMI-Related Common-Mode (CM) Noise Analysis and Prediction of High-Speed Source-Series Terminated (SST) I/O Driver in System-on-Package (SOP)," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 65, no. 4, pp. 446-450, April 2018.

- D. Luo, G. Zhu and C. P. Yue, "Electromagnetic interference related common mode noise analysis for NRZ/PAM-4 signals in wireline communication link (Invited paper)," 2017 International Conference on Electron Devices and Solid-State Circuits (EDSSC), Hsinchu, Taiwan, 2017, pp. 1-2.

- Luo, Duona, et al. "Analysis on EMI related common-mode noise of SERDES transmitter." DesignCon, 2017

#### Tx Reference

- A. Tyagi et al., "A 50 Gb/s PAM-4 VCSEL Transmitter With 2.5-Tap Nonlinear Equalization in 65-nm CMOS," IEEE Photonics Technology Letters, vol. 30, no. 13, pp. 1246-1249, July 2018.

- P. -J. Peng *et al.*, "A 56-Gb/s PAM-4 Transmitter/Receiver Chipset With Nonlinear FFE for VCSEL-Based Optical Links in 40-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 57, no. 10, pp. 3025-3035, Oct. 2022.

- J. Hwang *et al.*, "A 64Gb/s 2.29pJ/b PAM-4 VCSEL Transmitter With 3-Tap Asymmetric FFE in 65nm CMOS," in *2019 Symposium on VLSI Circuits*, Kyoto, Japan, 2019, pp. C268-C269.

- H. Do et al., "A 64 Gb/s 2.09 pJ/b PAM-4 VCSEL Transmitter with Bandwidth Extension Techniques in 40 nm CMOS," in 2021 IEEE Asian Solid-State Circuits Conference, Busan, Korea, 2021, pp. 1-3.

- H. Ramon *et al.*, "Low-power 56Gb/s NRZ microring modulator driver in 28nm FDSOI CMOS," *IEEE Photon. Technol. Lett.*, vol. 30, no. 5, pp. 467-470, Mar. 2018.

- H. Li *et al.*, "A 25 Gb/s, 4.4 V-swing, AC-coupled ring modulator-based WDM transmitter with wavelength stabilization in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 50, no. 12, pp. 3145-3159, Dec. 2015.

- R. Wang *et al.*, "A CMOS photonic optical PAM4 transmitter linearized using three-segment ring modulator," in *Proc. 62nd Midwest Symp. Circuits and Systems* (MWSCAS), 2019, pp. 1114-1117.

- N. Mehta et al., "A laser-forwarded coherent transceiver in 45-nm SOI CMOS using monolithic microring resonators," IEEE J. Solid-State Circuits, vol. 55, no. 4, pp. 1096-1107, Apr. 2020.

- P. Rito et al., "A DC-90-GHz 4-Vpp Modulator Driver in a 0.13-μm SiGe:C BiCMOS Process," *IEEE Transactions on Microwave Theory and Techniques*, vol. 65, no. 12, pp. 5192-5202, Dec. 2017.

- A. H. Ahmed *et al.*, "A Dual-Polarization Silicon-Photonic Coherent Transmitter Supporting 552 Gb/s/wavelength," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 9, pp. 2597-2608, Sept. 2020.

- A. Fatemi et al., "A Multi-mode Linear Optical Modulator Driver Circuit in 130 nm SiGe BiCMOS Technology," in 2021 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), Monterey, CA, USA, 2021, pp. 1-4.

- F. Iseini et al., "Lumped Ultra-Broadband Linear Driver in 130 nm SiGe SG13G3

Technology," in 2022 IEEE BiCMOS and Compound Semiconductor Integrated

Circuits and Technology Symposium (BCICTS), Phoenix, AZ, USA, 2022, pp. 136139.

- T. Wu et al., "Overview of Signal Integrity and EMC Design Technologies on PCB: Fundamentals and Latest Progress," IEEE Trans. Electromagn. Compat., vol. 55, no. 4, pp. 624–638, Aug. 2013.

- Michael Rowlands et al., "EMI Analysis of High-Speed I/O Connector in an Active System", in DesignCon, CA, USA, Feb 2015.

- Michael W. Fogg, "Understanding the Effects of Channel Generated Skew on Chassis EMI", in *DesignCon*, CA, USA, Feb 2015.

- P. Acimovic, "Novel Band-Stop Common Mode Filter For High-Speed Digital Data Transmission," in *DesignCon*, 2007.

- P. Acimovic, "Loaded Parallel Stub Common Mode Filter," in DesignCon, 2008.

- D. M. Hockanson *et al.*, "Investigation of fundamental EMI source mechanisms driving common-mode radiation from printed circuit boards with attached cables," *IEEE Trans. Electromagn. Compat.*, vol. 38, no. 4, pp. 557–566, 1996.

- M. Kim, "Periodically Corrugated Reference Planes for Common-Mode Noise Suppression in High-Speed Differential Signals," *IEEE Trans. Electromagn.* Compat., vol. 58, no. 2, pp. 619–622, Apr. 2016.

- J. K. Kim *et al.*, "High-speed current-mode logic amplifier using positive feedback and feed-forward source-follower techniques for high-speed CMOS I/O buffer," *IEEE J. Solid-State Circuits*, vol. 40, no. 3, pp. 796–802, Mar. 2005.

- PAM-4: A Key Solution For Next-Generation Short-Haul Optical Fiber Links, https://www.neophotonics.com/pam-4-key-solution-next-generation-short-haul-optical-fiber-links/.

- J. Lee et al., "Design of 56 Gb/s NRZ and PAM4 SerDes transceivers in CMOS technologies," IEEE J. Solid-State Circuits, vol. 50, no. 9. pp. 2061–2073, Sep-2015.

# Wireline and Optical Receiver 有线和光接收机

Prof. C. Patrick Yue 俞捷教授

芯动力人才计划®第 125 期国际名家讲堂

#### **Outline**

- Motivation

- Electrical vs Optical Link

- RX Architecture

- Wireline vs Optical Receiver

- ADC-Based Receiver

- Circuit Implementations

- PD Interface

- Multi-peaking TIA

- Modified Cherry-Hooper Amplifier

- FFE and DFE Implementation

- Practical Issue

- On-Chip LDO for Improved Sensitivity

- Conclusion

#### **Outline**

- Motivation

- Electrical vs Optical Link

- RX Architecture

- Wireline vs Optical Receiver

- ADC-Based Receiver

- Circuit Implementations

- PD Interface

- Multi-peaking TIA

- Modified Cherry-Hooper Amplifier

- FFE and DFE Implementation

- Practical Issue

- On-Chip LDO for Improved Sensitivity

- Conclusion

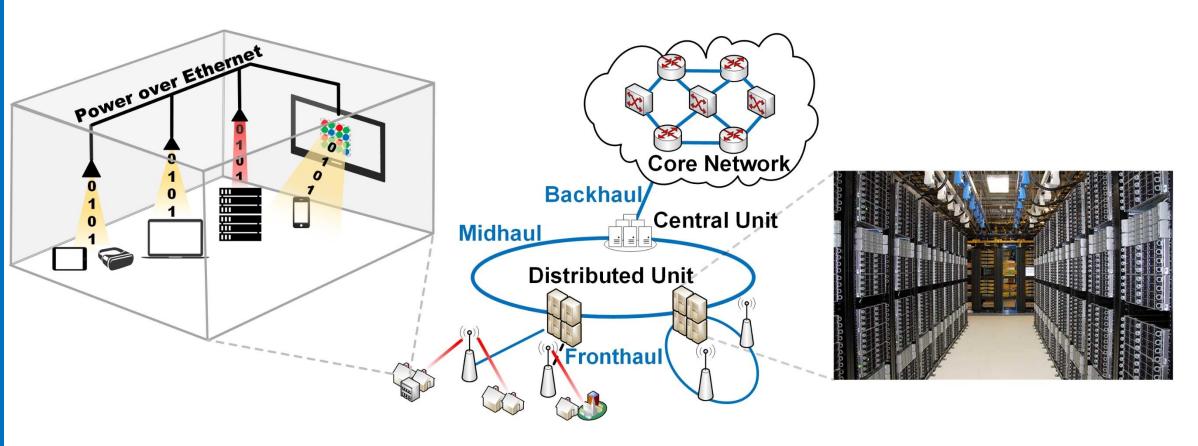

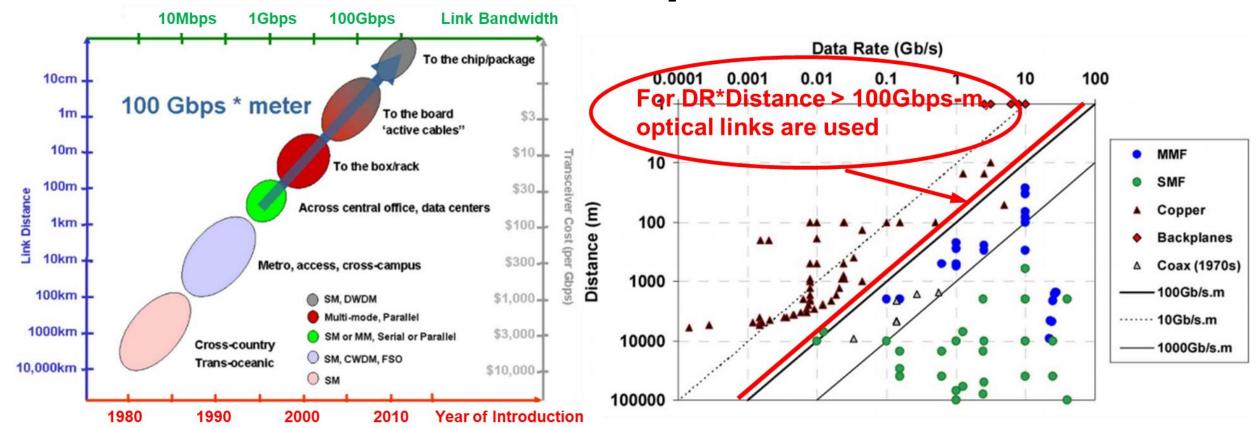

# **Electrical vs Optical Links**

Penetration of optical links into communications.

• SMF: Single-Mode Fiber

• MMF: Multi-Mode Fiber

Electrical links are bonded by the 100Gb/s-m bandwidth-distance product

# **Electrical vs Optical Links**

The potential exists to lower the energy of optical links to below a pJ/bit to the service link lengths ~1 m

#### **Outline**

- Motivation

- Electrical vs Optical Link

- RX Architecture

- Wireline vs Optical Receiver

- ADC-Based Receiver

- Circuit Implementations

- PD Interface

- Multi-peaking TIA

- Modified Cherry-Hooper Amplifier

- FFE and DFE Implementation

- Practical Issue

- On-Chip LDO for Improved Sensitivity

- Conclusion

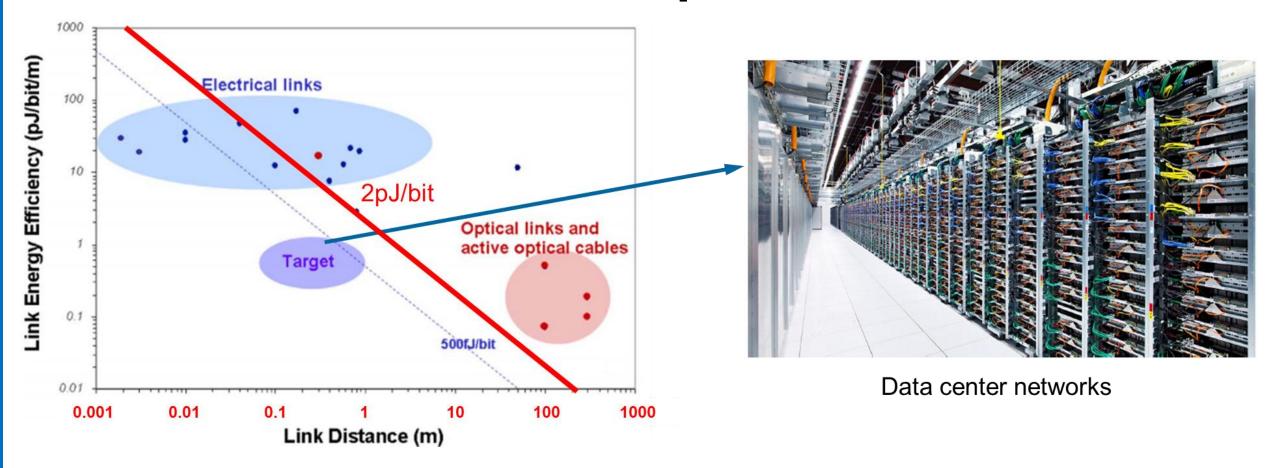

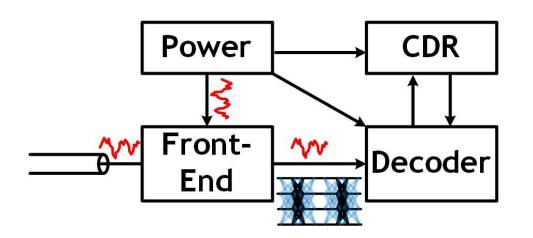

# **Intensity Modulation and Direct Detection Link**

Typical system architecture of an intensity modulation and direct detection (IMDD) optical link

| Distance/Optical Fiber    | Modulation                 |  |  |  |

|---------------------------|----------------------------|--|--|--|

| 100m MMF (400 GBASE-SR16) | 25Gbaud NRZ, 16ch parallel |  |  |  |

| 500m SMF (400 GBASE-PSM4) | 1λ 50Gbaud PAM4            |  |  |  |

| 2km SMF (400 GBASE-FR8)   | WDM 8λ WDM 25Gbaud PAM4    |  |  |  |

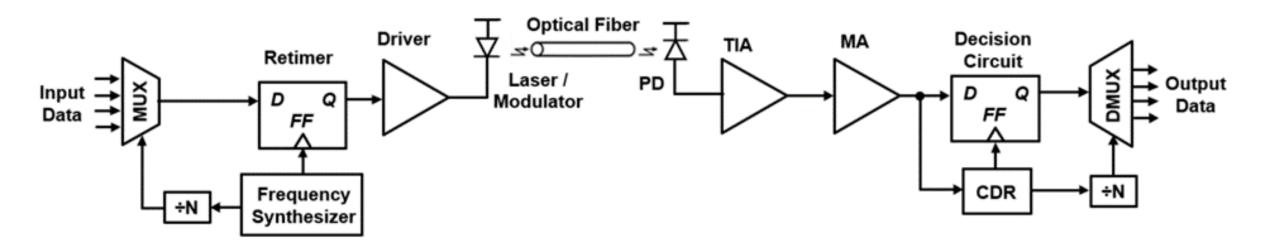

# Comparison Between Wireline and Optical RX

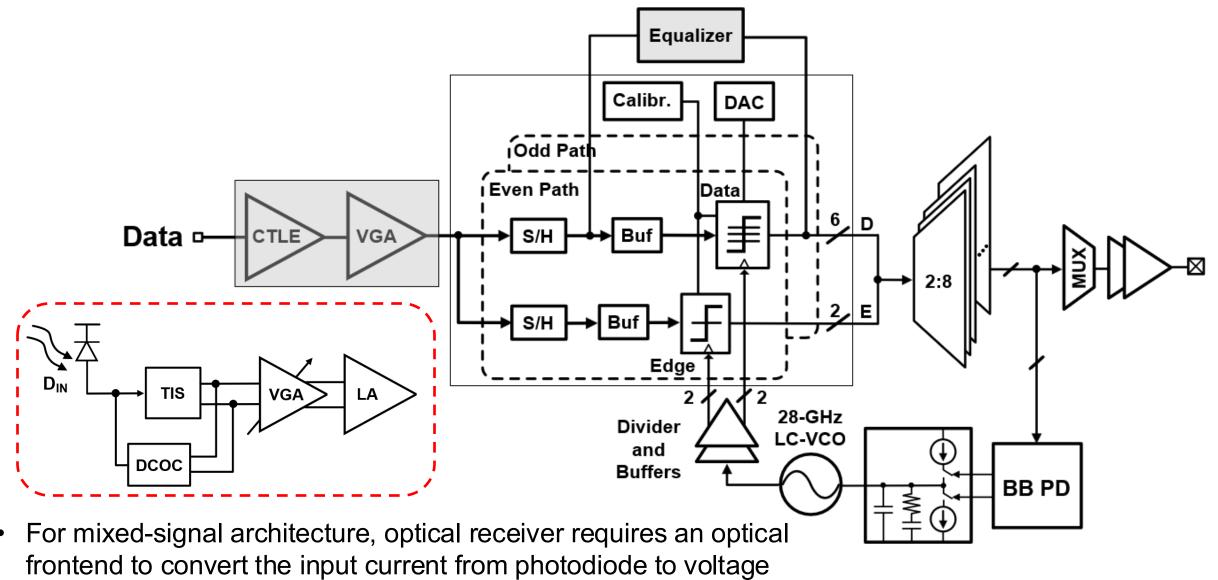

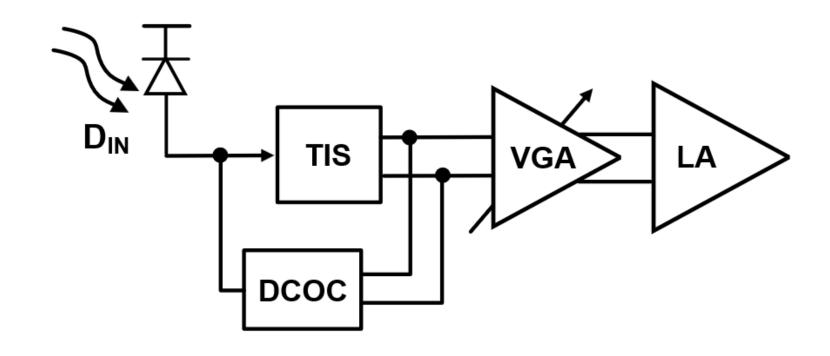

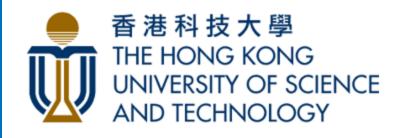

# **Optical Frontend Architecture**

• Optical frontend consists of a transimpedance amplifier (TIS), a variable amplifier (VGA), a limiting amplifier (LA), and a dc-offset cancellation (DCOC) block

# **Optical Frontend Architecture**

Feedforward equalization and decision feedback equalization can be implemented to compensate for the ISI of TIA

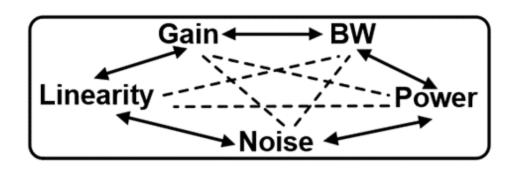

# **Optical Receiver Design Tradeoffs**

- Highly integrated optical communication system modules using silicon-based CMOS transceiver ICs with integrated AFE are highly desirable

- As the first stage of RX, the performance of TIA dictates the minimum input sensitivity and the maximum data rate of the entire RX

- TIA design tradeoff: by increasing the TIA gain, the noise can be reduced, and the sensitivity is improved, but the BW and data rate suffer

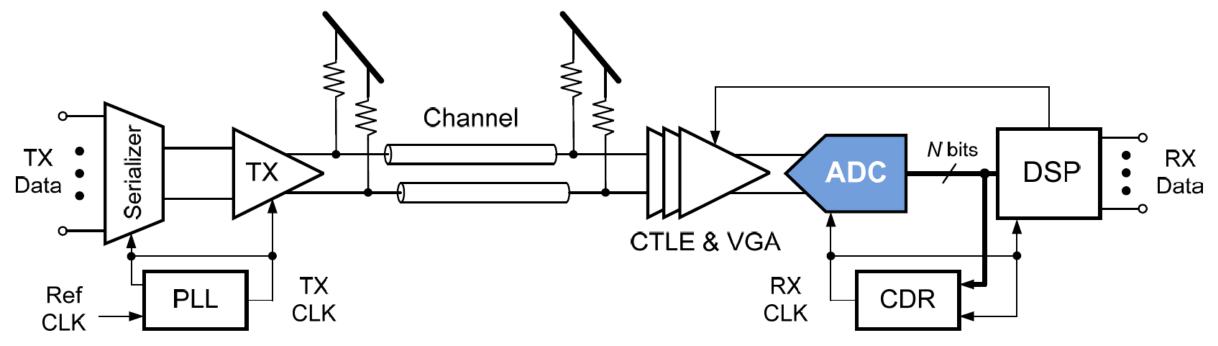

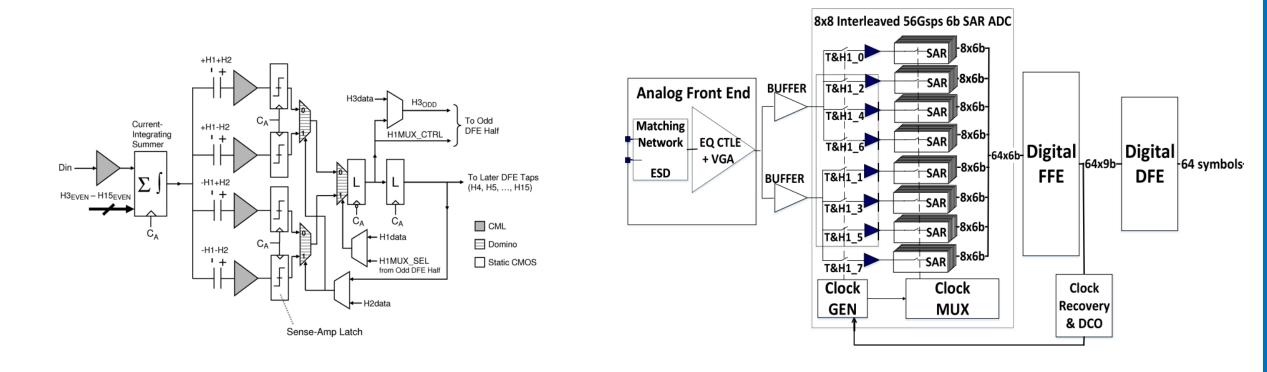

#### **ADC-Based Receiver Front Ends**

- ADC-based receivers perform ISI cancellation in digital domain, allowing for flexible advanced equalization and symbol detection

- Well-suited for more spectrally-efficient modulation schemes (PAM4)

- Benefit from improved area and power with CMOS scaling

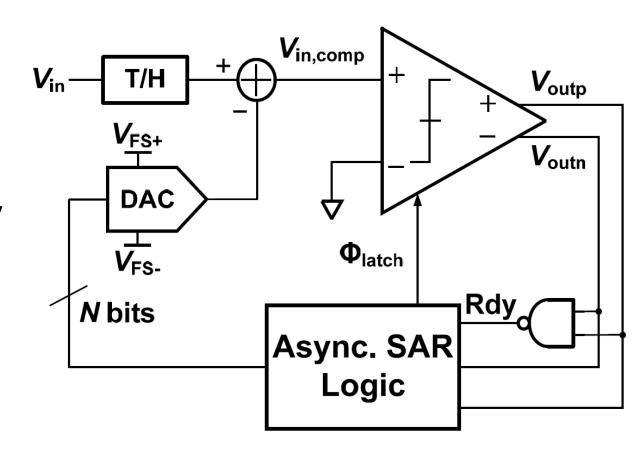

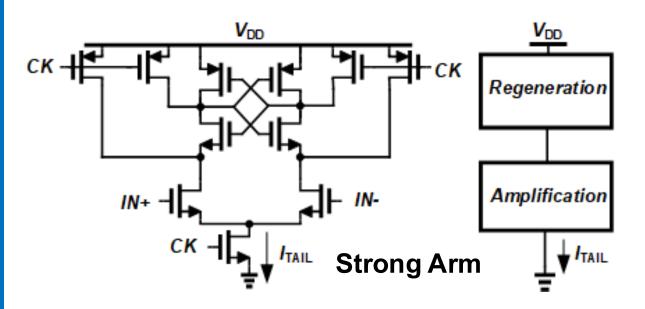

#### SAR ADC

- Performs a binary search conversion over multiple clock cycles

- Simplest implementations only require one comparator per unit ADC

- Slower unit ADC relative to flash/binary search

- Excellent choice for 6-8b resolution to support both PAM-2 and PAM-4

- The dominant architecture for PAM-4 ADC-based receivers

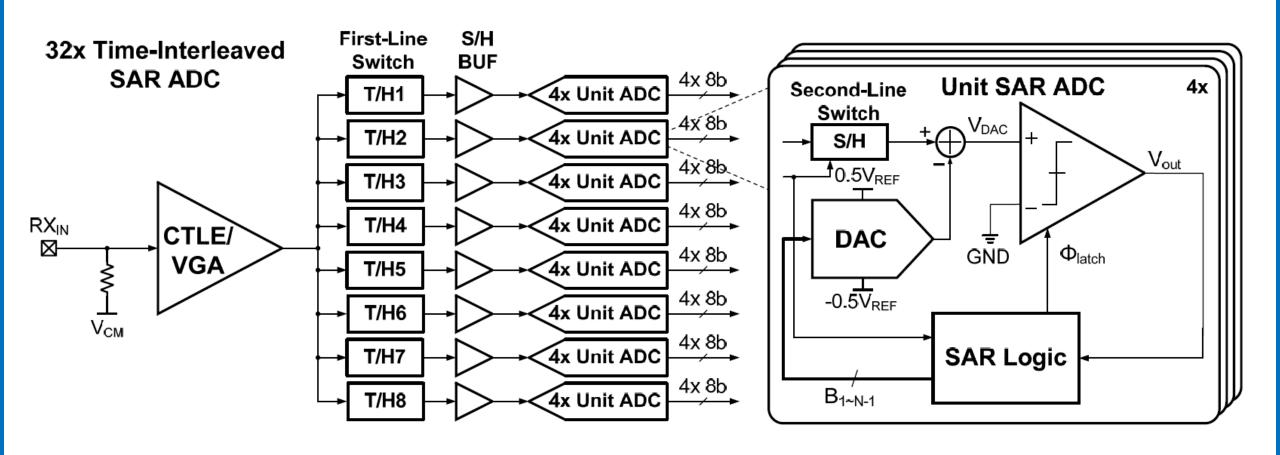

#### **Time-Interleaved ADCs**

Wireline ADCs are time-interleaved to achieve high sample rates

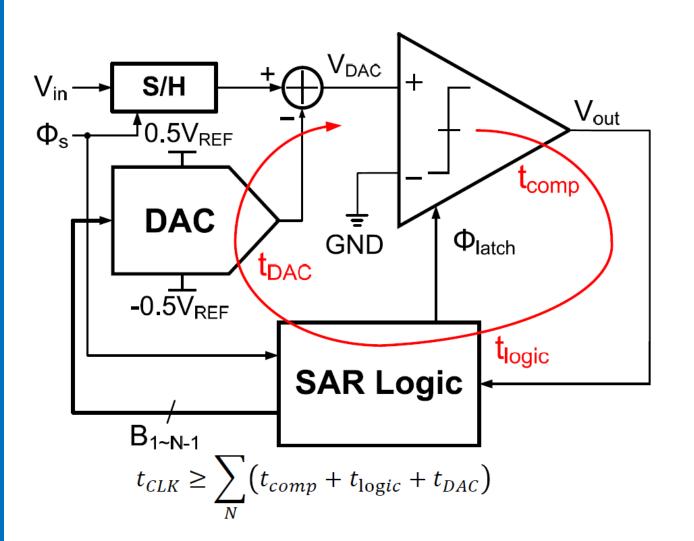

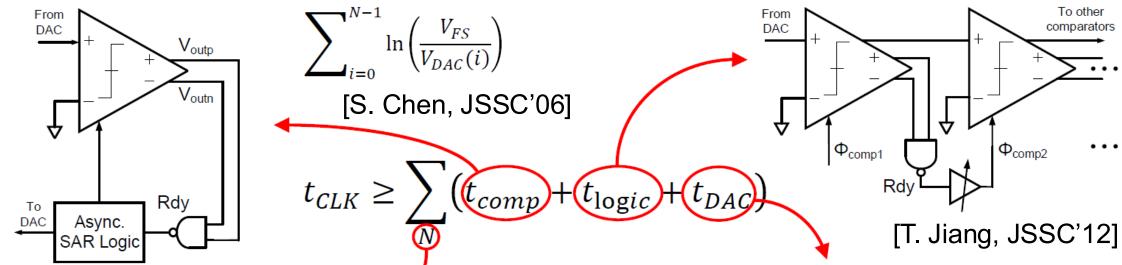

# **Unit SAR ADC: Critical Timing Path**

- SAR ADC consists of S/H, DAC, comparator and SAR logic

- The conversion speed of SAR ADCs depends on the delay from comparator, logic and DAC in the critical timing path

- Various techniques to reduce the delay for faster SAR ADC speed

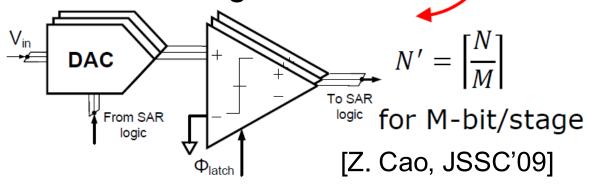

# **Unit SAR ADC: Advanced Techniques**

Asynchronous SAR operation

Loop-unrolled SAR

Multi-bit/stage conversion

Redundant SAR algorithm (trade-off N)

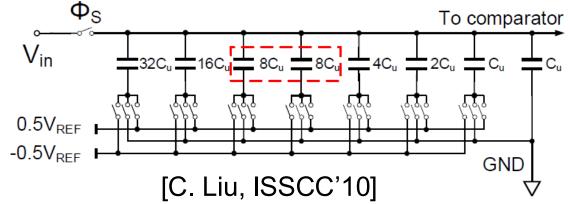

#### **DAC**

- DAC generates residue signals by subtracting binary weighted reference from input

- Capacitive DAC is the most popular DAC structure due to low power consumption

# **DAC** Implementation

Minimum unit cap size limited by matching requirement and KT/C noise (noise usually dominated by front-end and comparator)

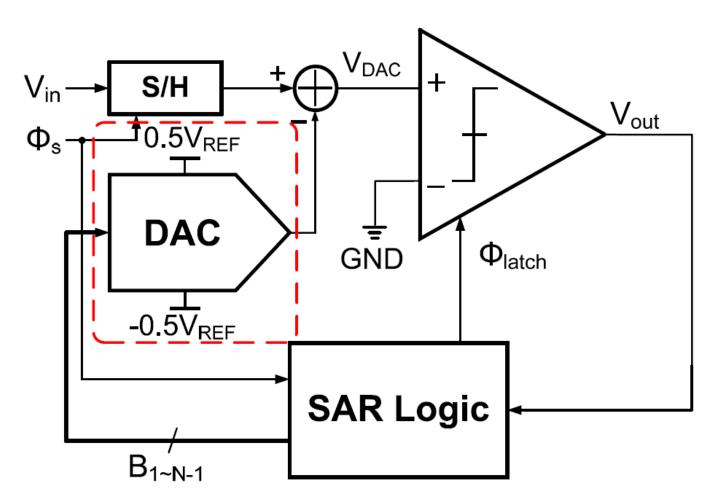

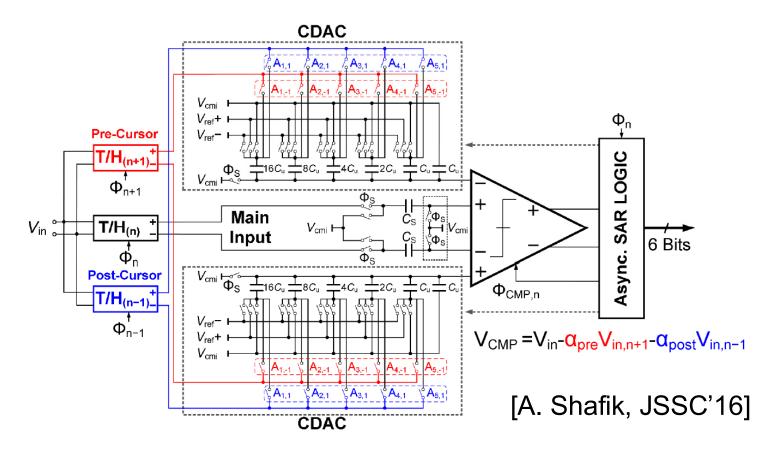

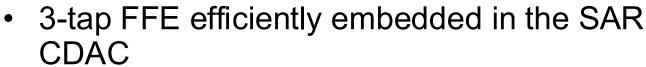

#### Unit SAR ADC with Embedded FFE

Main trade-off is increased T/H loading (3X)

Both pre- and post-cursor taps have ~33 LSB range and ~1.1 LSB resolution

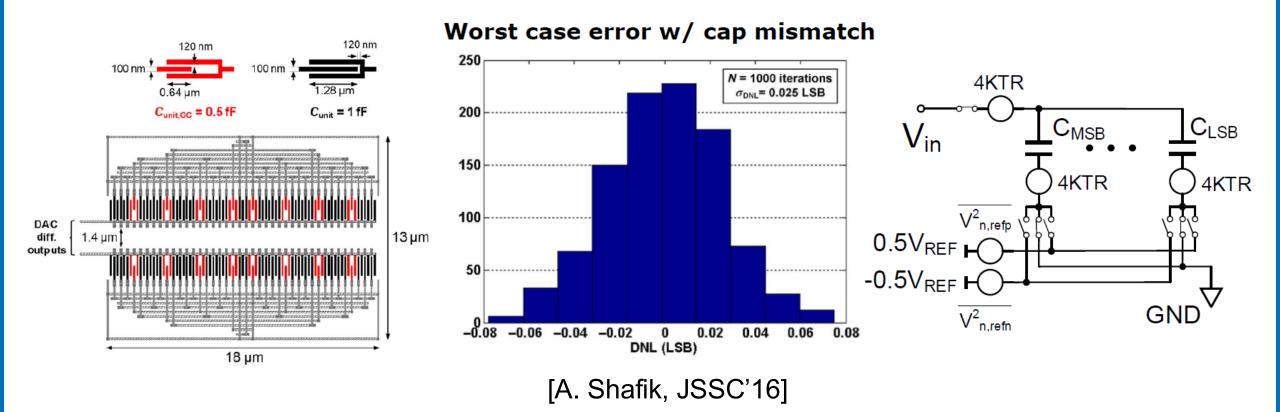

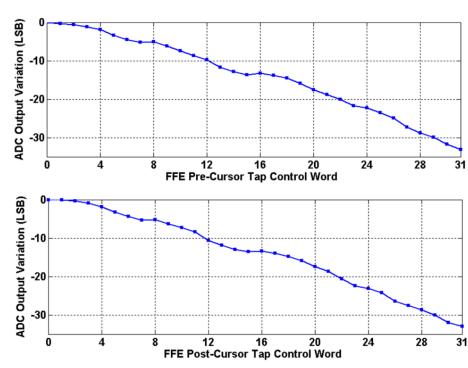

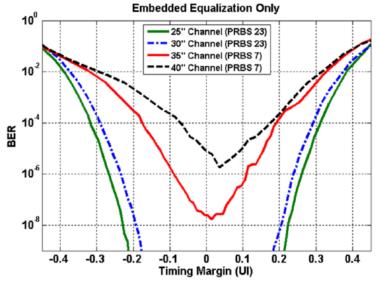

# 10Gb/s NRZ ADC-Based RX Prototype in 65nm

[A. Shafik, JSSC'16]

- 10GS/s 32-way interleaved SAR ADC with embedded 3-tap FFE

- Embedded equalization alone is sufficient for the two lowest-loss (21, 25dB) channels

- Additional digital equalization is necessary for the two highest-loss (32, 36dB) channels

#### **Outline**

- Motivation

- Electrical vs Optical Link

- RX Architecture

- Wireline vs Optical Receiver

- ADC-Based Receiver

- Circuit Implementations

- PD Interface

- Multi-peaking TIA

- Modified Cherry-Hooper Amplifier

- FFE and DFE Implementation

- Practical Issue

- On-Chip LDO for Improved Sensitivity

- Conclusion

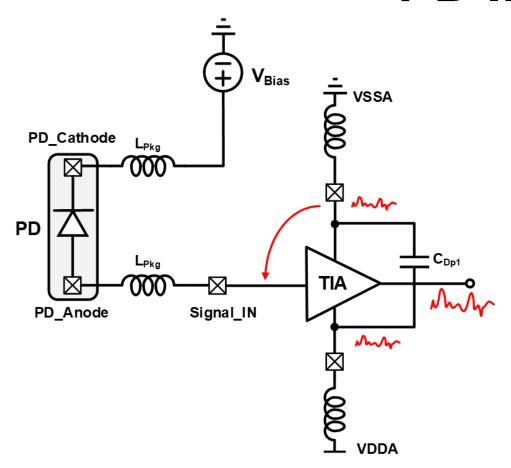

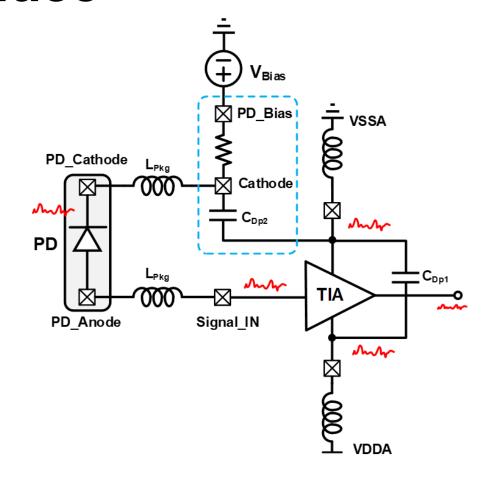

# A 41-mW 30-Gb/s CMOS Optical Receiver with Digitally-Tunable Cascaded Equalization

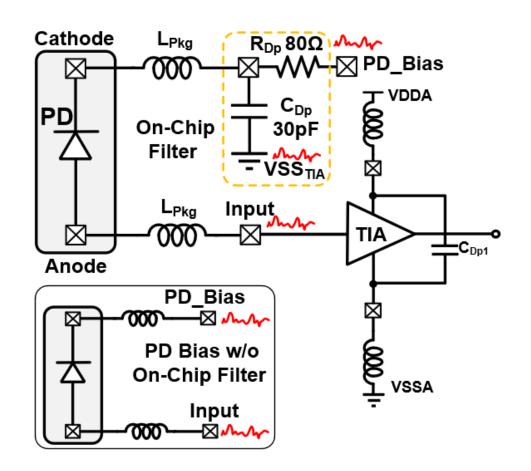

#### **PD Interface**

- External PD bias

- Transfer the supply noise to TIA output

- On-chip PD bias

- Prevent the supply noise to TIA output

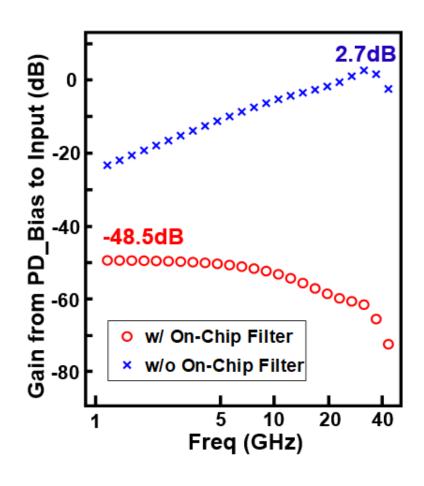

#### PD-to-RX Interface with Bond Wire

- On-chip PD bias and simulated conversion gain from PD bias to TIS input

- On-chip filtering prevents the noise at PD bias converting to TIA input

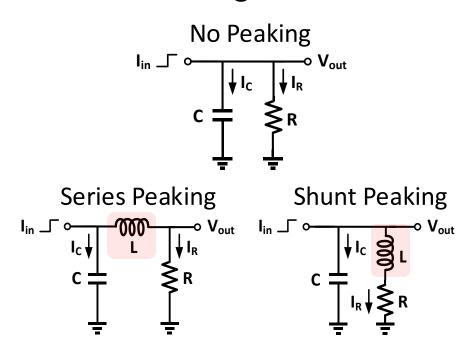

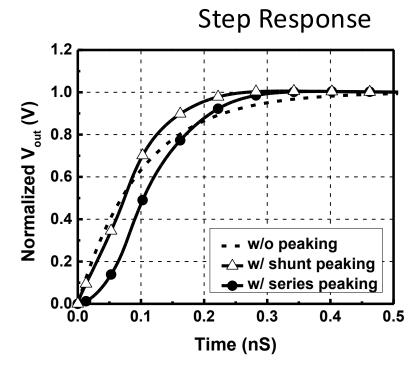

#### **Bandwidth Enhancement Technique**

Inductive Peaking

- Loading capacitor slows down output transition

- Series or shunt peaking inductor allows more high-frequency current to charge C -> Faster step response

- Faster response <-> Higher bandwidth

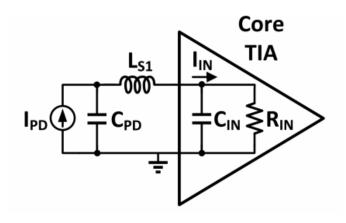

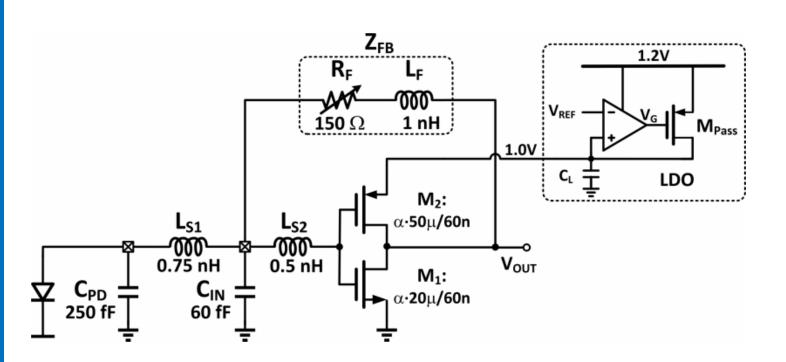

# **Bandwidth Enhancement Technique**

Multiple Inductive Peaking Technique

- Equivalent circuit of the input series peaking network

- L<sub>S1</sub>: bond-wire inductance

- Small-signal model of the core TIA

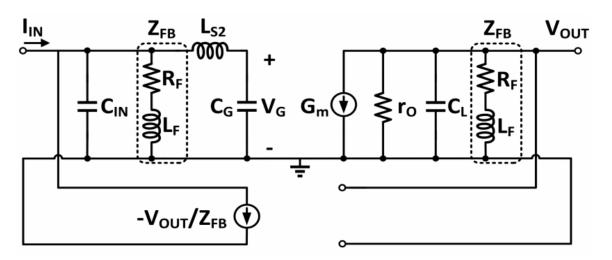

- L<sub>F</sub> and L<sub>S2</sub> create the second and the third peaking

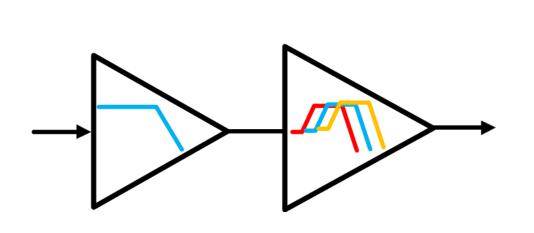

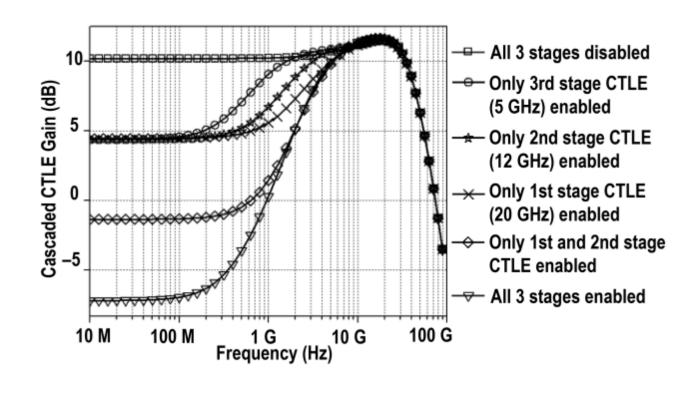

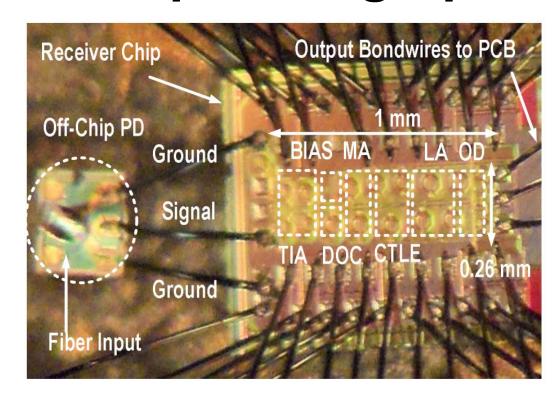

#### **Bandwidth Enhancement Technique**

Multi-Stage Cascaded CTLE

- Multi-stage CLTE provides different peaking at different frequencies

- Simulated frequency responses of the 3-stage cascaded CTLE

#### **TIA and CTLE**

Schematic of TIA with integrated LDO

Schematic of the CTLE

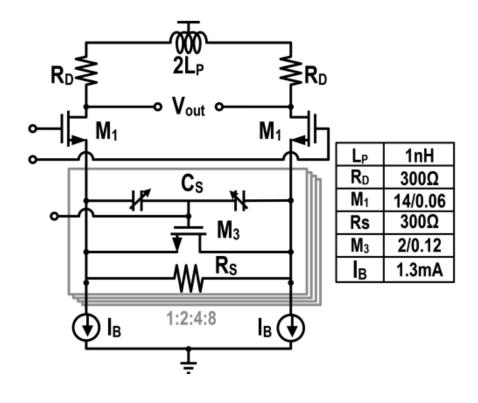

#### Modified CH MA/LA and Output Driver

- Schematic of the modified CH MA/LA

Schematic of the output driver

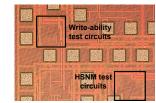

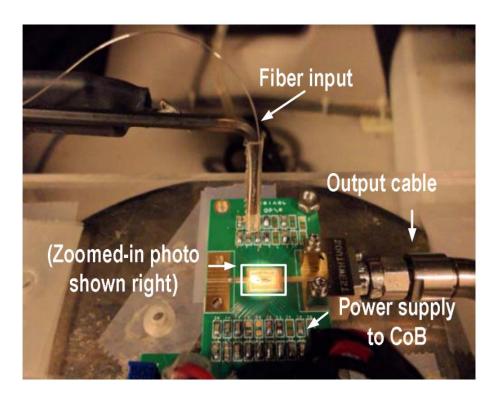

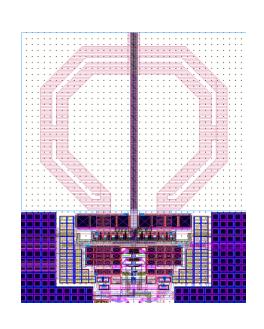

# Measurement Setup and Chip Micrograph

- Optical measurement setup

- Optical light is coupled through a single-mode fiber (SMF)

- Chip micrograph

- Fabricated in 65nm CMOS technology

- Wire-bonded with a commercial PD

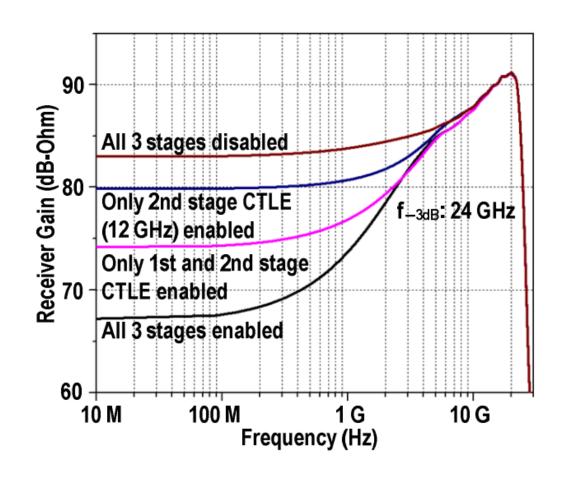

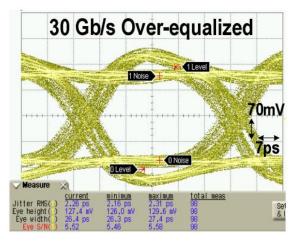

#### **Electrical Measurement Results**

- Measured electrical frequency response

- 67-83 dBΩ, with 24-GHz bandwidth

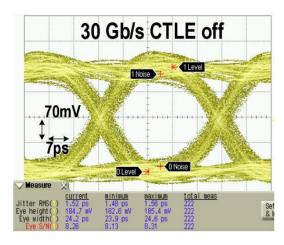

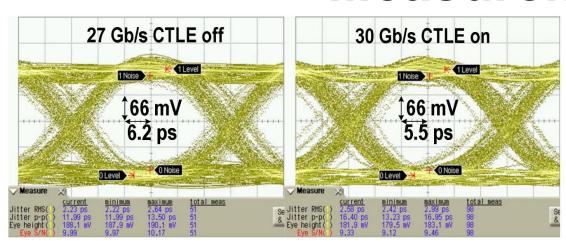

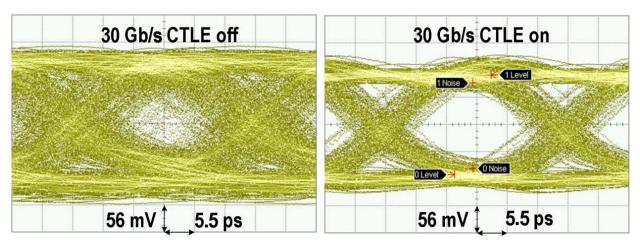

Measured electrical eye diagram at 30 Gb/s with CTLE off and on

#### **Measurement Results**

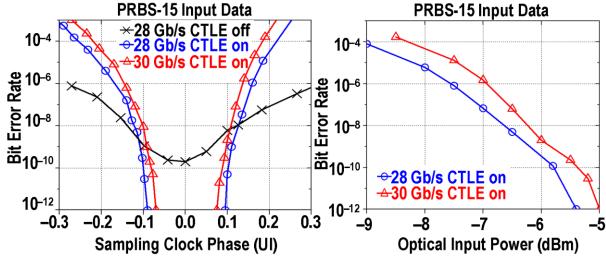

- Optical measurement results with a 30-Gb/s PD

- **PRBS-15 Input Data PRBS-15 Input Data**  $\times$  25 Gb/s 10-4 10-4 → 28 Gb/s → 30 Gb/s  $\times$  25 Gb/s → 28 Gb/s 10-12 0.0 0.2 0.3 Sampling Clock Phase (UI) **Optical Input Power (dBm)**

- BER bathtub curves and input sensitivity

Optical measurement results with a 14-Gb/s PD

BER bathtub curves and input sensitivity

# **Performance Summary and Comparison**

|                     | [1] ISSCC'13 | [2] ISSC'13 | [3] ISSCC'12 | This Work       |      |  |

|---------------------|--------------|-------------|--------------|-----------------|------|--|

| CMOS Technology     | 65nm         | 65nm        | 90nm         | 65nm            |      |  |

| Supply Voltage      | 1            | 3.3/1       | 1.2          | 1 (1.2 for LDO) |      |  |

| Gain (dBΩ)          | 72.5         | 76.8        | 78.3         | 83              |      |  |

| Bandwidth (GHz)     | 21           | 21.4        | 20           | 24              |      |  |

| Power (mW)          | 48.8         | 90.9        | 44.4         | 41              |      |  |

| Data Rate (Gb/s)    | 25           | 25-28       | 25           | 30              |      |  |

| Sensitivity (dBm)   | -6.8         | -9.7        | -4           | -5.6            | -5.0 |  |

| Eye Opening (1-UI)  | N/A          | 65%         | 22%          | 24%             | 18%  |  |

| Efficiency (pJ/bit) | 1.95         | 3.25        | 1.78         | 1.37            |      |  |

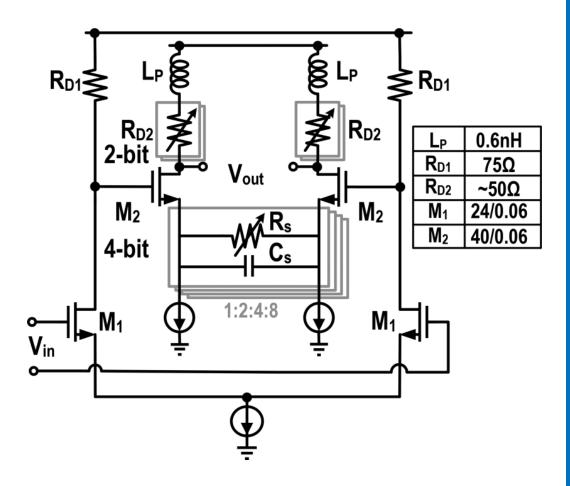

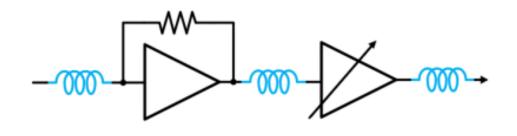

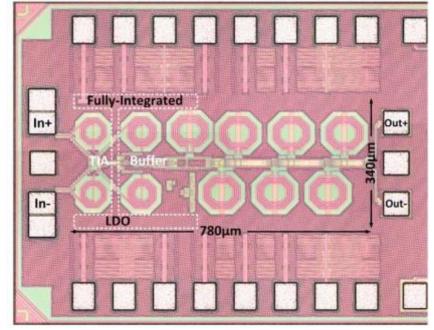

# An Energy- and Area-Efficient Inductorless CMOS PAM4 Optical Receiver Achieving 700 Gb/s/mm<sup>2</sup> Towards Silicon Photonic Chiplet

# **Optical Receiver Architecture Comparison**

- Distributed inductive peaking

- Large area

- Low-BW TIA + CTLE

- Power hungry

- Inductorless TIA + FFE + DFE

- Compact and energy-efficient

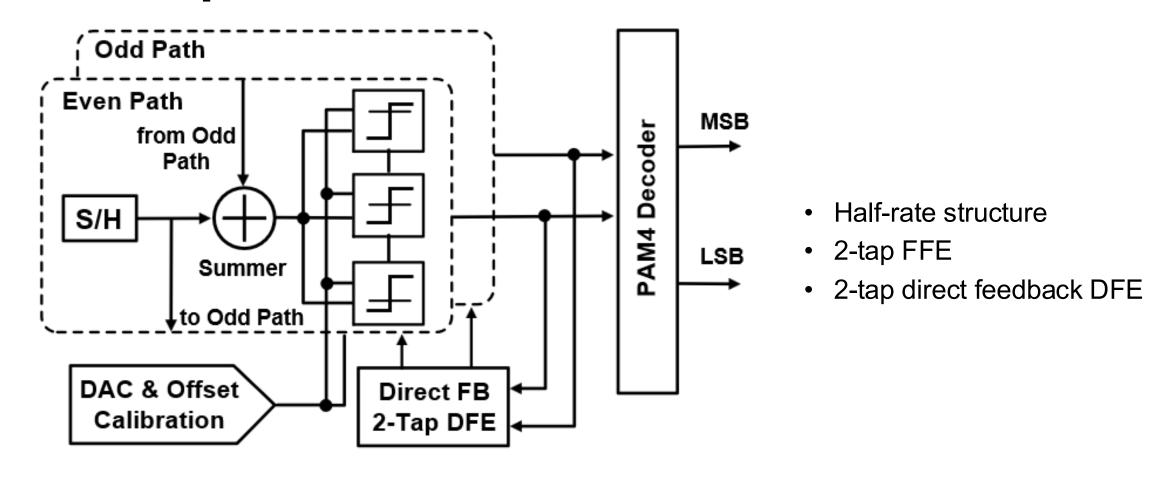

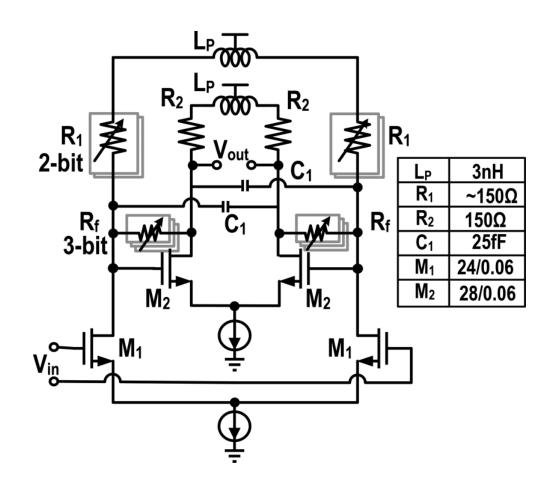

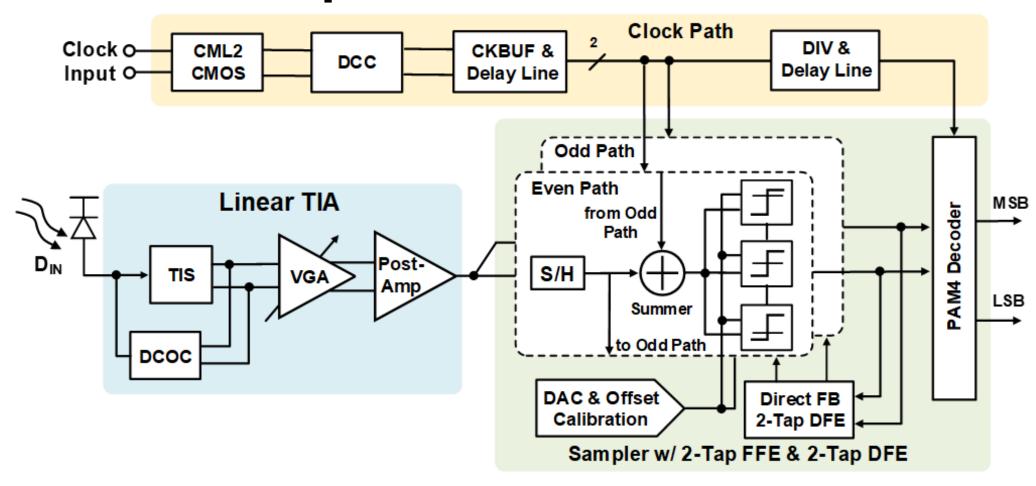

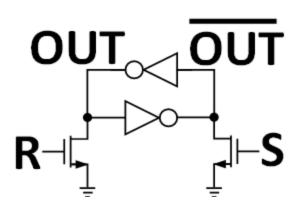

# **Proposed Architecture**

- Half-rate structure

- 2-tap FFE and 2-tap DFE integrated with sampler

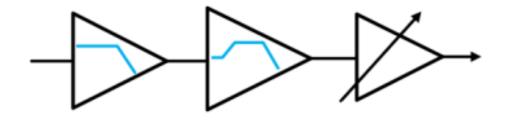

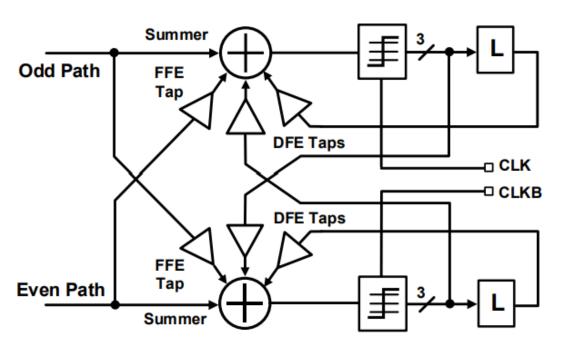

#### **FFE and DFE**

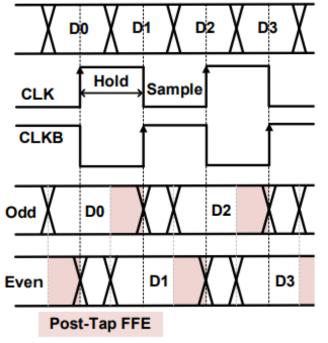

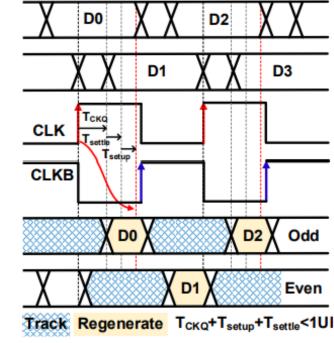

#### **Timing Diagram of FFE and DFE**

#### Half-rate FFE and DFE

- Post-tap FFE can be achieved by summing the odd and even signal path

- 1-UI timing constrain should be met for the first tap direct DFE

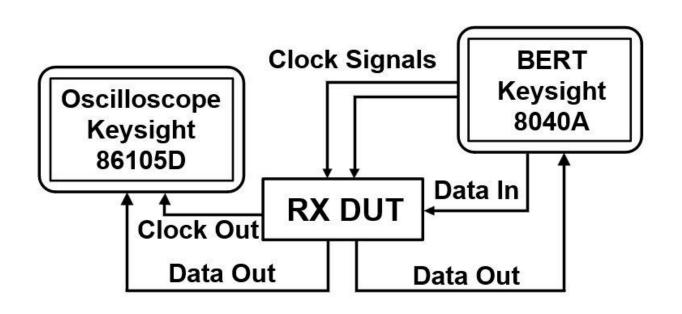

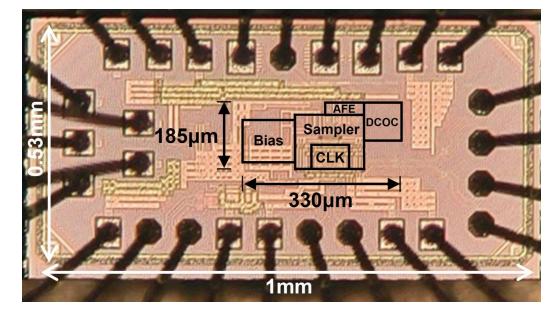

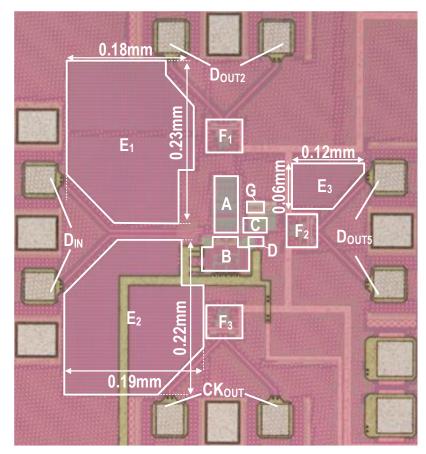

# Measurement Setup and Chip Micrograph

Measurement setup

- Chip micrograph

- Core area: 0.06mm<sup>2</sup>

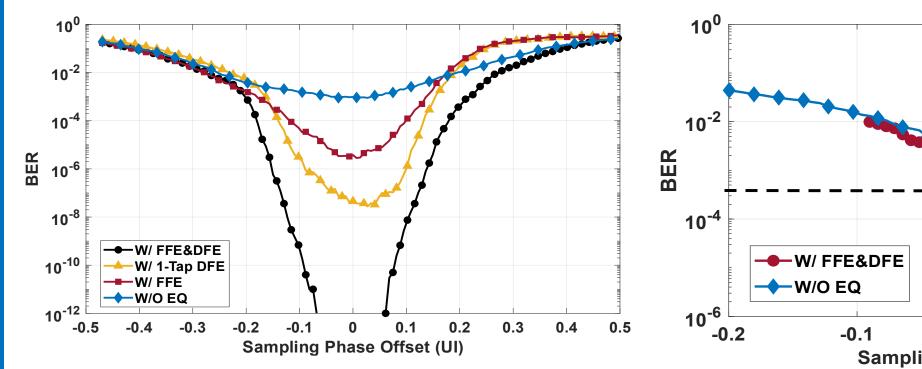

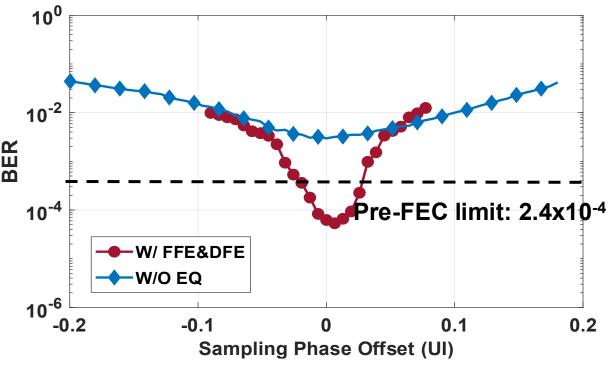

#### **Measurement Results**

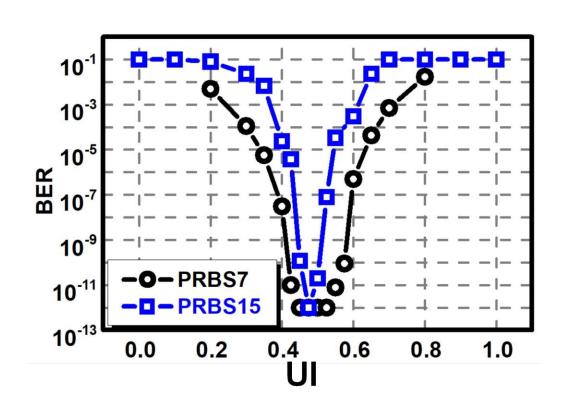

Bathtub curve at 30 Gb/s NRZ

Bathtub curve at 42 Gb/s PAM4

# **Performance Summarv and Comparison**

|                                     | JSSC'21      | OJCS'21      | ISSCC'21                 |             | RFIC'23         | This Work                 |              |  |

|-------------------------------------|--------------|--------------|--------------------------|-------------|-----------------|---------------------------|--------------|--|

| Technology                          | 65nm<br>CMOS | 40nm<br>CMOS | 28nm<br>CMOS             |             | 28nm<br>CMOS    | 28nm CMOS                 |              |  |

| Data Rate (Gb/s)                    | 16           | 36           | 100                      |             | 42.7            | 42                        |              |  |

| Signaling                           | Duobinary    | PAM4         | PAM4                     |             | NRZ             | PAM4                      |              |  |

| Number of<br>Inductors              | 0            | 6            | >16                      |             | 3               | 0                         |              |  |

| NRZ OMA Sens. at<br>BER 1e-12 (dBm) | -16.8        | N/A          | -11.1<br>@56Gb/s         |             | -3.6*           | -8.2<br>@28Gb/s           |              |  |

| PAM4 OMA Sens.<br>at 2.4e-4 (dBm)   | N/A          | -4.8*        | -8.9                     |             | N/A             | -5.1 @48Gb/s              |              |  |

| Rx EQ Capabilities                  | N/A          | 2-Tap DFE    | 2-Tap FFE +<br>2-Tap DFE |             | N/A             | 2-Tap FFE + 2<br>-Tap DFE |              |  |

| Area (mm²)                          | 0.09         | 0.23         | 0.45                     |             | 0.11**          | 0.0                       | )6           |  |

| Power (mW)                          | 23 (RX)      | 128.8 (RX)   | 117<br>(TIA)             | 381<br>(RX) | 145.2**<br>(RX) | 13.1<br>(TIA)             | 57.3<br>(RX) |  |

| Efficiency (pJ/bit)                 | 1.9          | 4.0          | 1.17                     | 3.9         | 3.4             | 0.31                      | 1.36         |  |

| FoM (Gb/s/mm²)                      | 100          | 139          | 222                      |             | 222 388         |                           | 700          |  |

<sup>\*</sup>Estimated from the reported sensitivity curve

<sup>\*\*</sup>CDR included

#### **Outline**

- Motivation

- Electrical vs Optical Link

- RX Architecture

- Wireline vs Optical Receiver

- ADC-Based Receiver

- Circuit Implementations

- PD Interface

- Multi-peaking TIA

- Modified Cherry-Hooper Amplifier

- FFE and DFE Implementation

- Practical Issue

- On-Chip LDO for Improved Sensitivity

- Conclusion

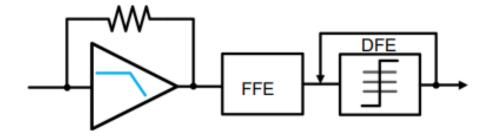

# A Fully-Integrated Low-Dropout Regulator With Full-Spectrum Power Supply Rejection

### **Motivations**

Fully-integrated and area-efficient low dropout regulator (LDO) are highly desirable for point-of-load power delivery.

LDOs with power supply rejection (PSR) up to **GHz range** are in demand for

wideband communication systems.

PIT

# **LDO Requirements**

To make a comparison, a figure-of-merit (FOM) of speed is defined

$$FOM = T_R \frac{I_Q}{I_{MAX}} = \frac{C \times \Delta V_{OUT}}{I_{MAX}} \times \frac{I_Q}{I_{MAX}}$$

[Hazucha JSSC 05]

- Fast transient response

- Small quiescent current  $(I_{O})$

- Good PSR

- Area-efficient and scalable with process

# LDOs with Off-/On-Chip Capacitor

- LDO Regulators with Off-Chip µF range Capacitor

- Off-chip cap is conventionally connected for filtering

- Dominate pole located the output node

- Small load transient glitches

- High PSR

- LDO Regulators with On-Chip sub-nF range Capacitor

- Dominate pole at the internal node (in previous designs)

- Large undershoot and overshoot during load transient

- Poor PSR

Improving the PSR and transient performances of the fully-integrated LDO is our key design issue

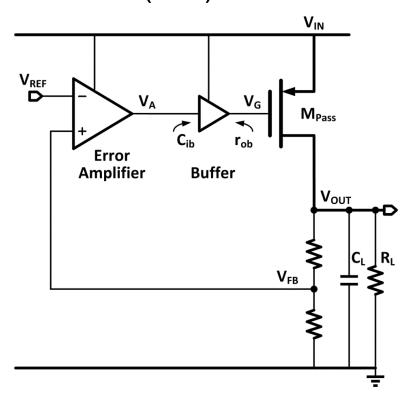

# Schematic of the FVF Topology

- **Basic idea**: take the advantage of the advanced processes, push the internal poles to be higher than the UGF.

- Technique: Flipped Voltage Follower (FVF)

[Man TCAS-I 08]

0.35μm CMOS

$p_{\mathsf{Gate}}$  Dominated

**Poor DC Regulation**

# Schematic of the BIA Topology

- Basic idea: take the advantage of the advanced processes, push the internal poles to be higher than the unity-gain frequency (UGF).

- Technique:

Buffer Impedance Attenuation (BIA)

[Al-Shyoukh JSSC 07]0.35μm CMOSWith 1μF Capacitor

# Schematic of the FVF + BIA Topologies

- Basic idea: take the advantage of the advanced processes, push the internal poles to be higher than the UGF.

- Techniques: Flipped Voltage Follower (FVF) Buffer Impedance Attenuation (BIA)

65nm CMOS

$p_{\text{Out}}$  Dominated

Poor DC Regulation

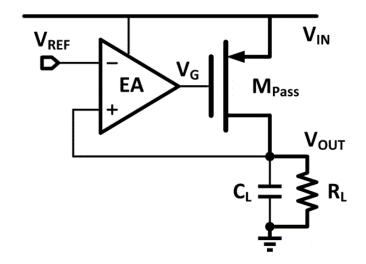

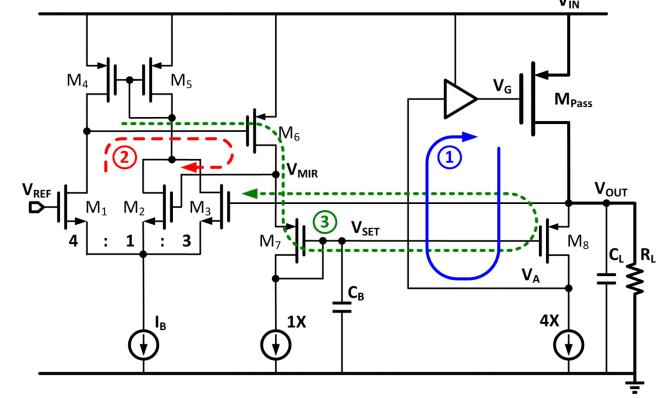

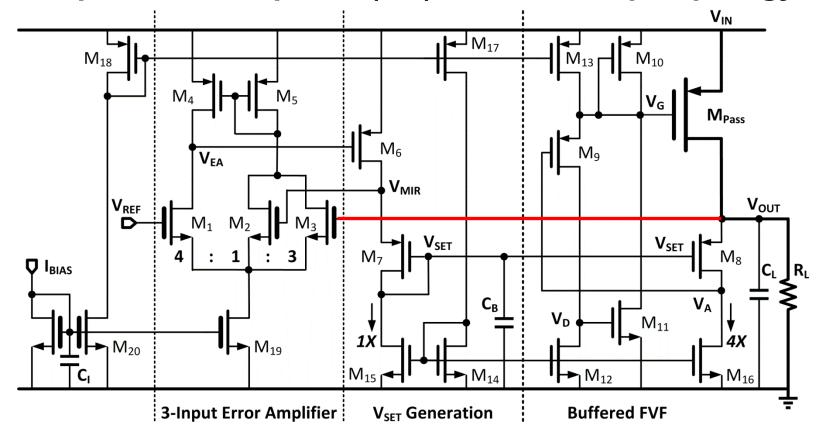

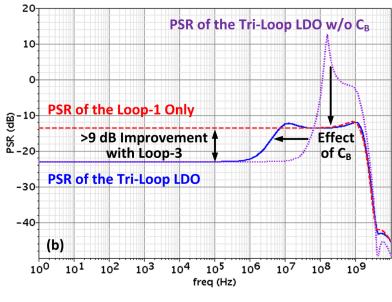

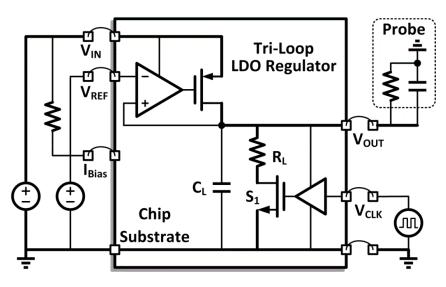

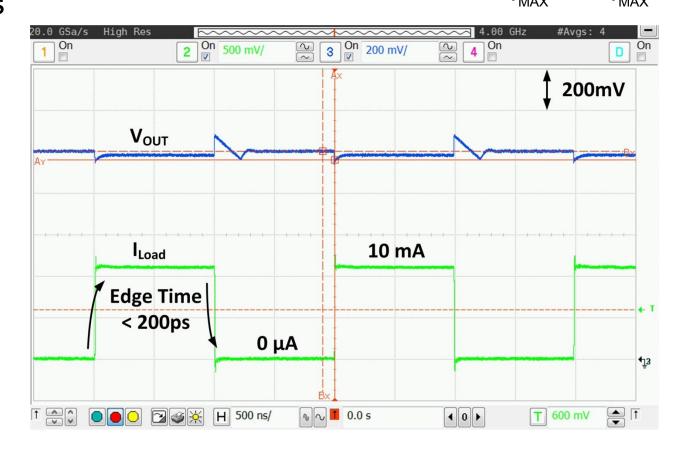

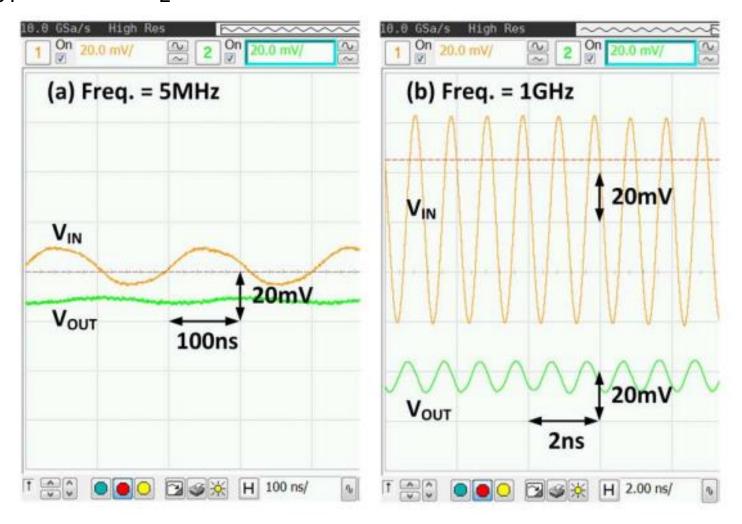

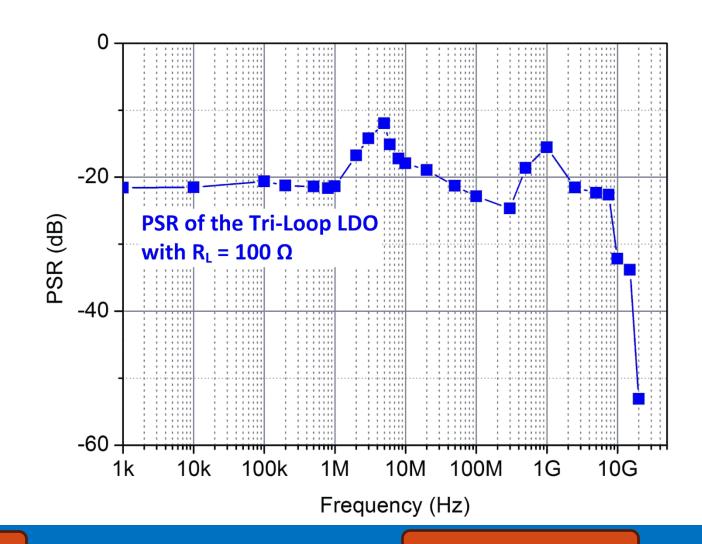

### **Tri-Loop in the Proposed LDO**

- Loop-1: an ultra-fast low-gain loop with  $p_{\text{Out}}$  being its dominant pole and  $p_{\text{Gate}}$  be pushed to GHz range by BIA technique;

- Loop-2: a slow loop that generates  $V_{MIR} \& V_{SET}$ ;

- Loop-3: feed  $V_{\text{OUT}}$  back to the EA to improve the DC accuracy.

### Schematic of the Proposed Tri-Loop LDO

- Techniques: Flipped Voltage Follower (FVF) and Buffer Impedance Attenuation (BIA)

- Proposed 3-Input Error Amplifier (EA), and Tri-Loop Topology

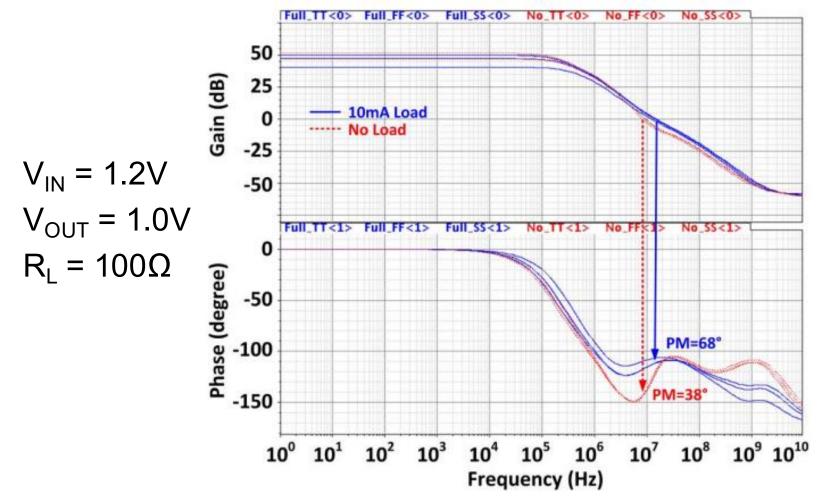

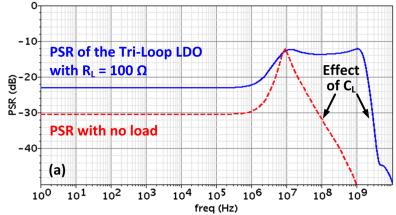

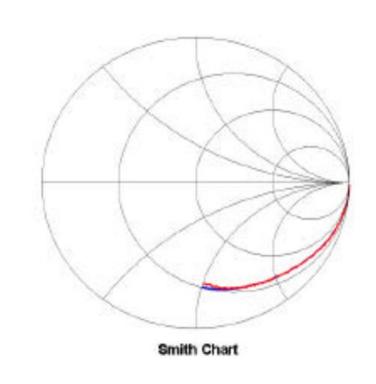

### Simulated Bode Plot of LDO and PSR

Bode plot of the LDO

PSR

•  $V_{IN} = 1.2V$

$R_I = 100\Omega$

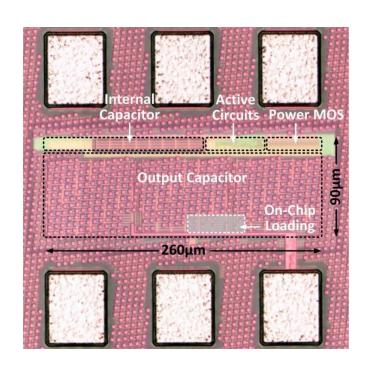

### Chip Micrograph of the LDO in 65nm