# **Energy-Efficient CMOS Fiber-Wireless Communication System-on-a-Chip**

by

Yipeng WANG

A Thesis Submitted to

The Hong Kong University of Science and Technology in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

in the Department of Electronic and Computer Engineering

September 2016, Hong Kong

# **Authorization**

I hereby declare that I am the sole author of the thesis.

I authorize the Hong Kong University of Science and Technology to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize the Hong Kong University of Science and Technology to reproduce the thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Yipeng WANG

September 2016

## **Energy-Efficient CMOS Fiber-Wireless Communication System-on-a-Chip**

by

#### Yipeng WANG

This is to certify that I have examined the above PhD thesis and have found that it is complete and satisfactory in all respects, and that any and all revisions required by the thesis examination committee have been made.

Prof. C. Patrick YUE, ECE Department (Thesis Supervisor)

Prof. Shiheng WANG, ACCT Department (Chairperson)

Prof. Wing-Hung KI, ECE Department (Committee Member)

Prof. Kevin J. CHEN, ECE Department (Committee Member)

Prof. Lilong CAI, MAE Department (Committee Member)

Prof. Bert SHI, Head of ECE Department

Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology September 2016 To my parents

#### **Abstract**

The growing deployment of bandwidth-intensive multimedia applications and cloud computing continue to escalate the burden on today's mobile communication network. Meanwhile, the demand for high-performance data traffic has gradually migrated from centralized telecommunication infrastructures to cost-sensitive mobile applications and consumer electronics. Therefore, the need for cost reduction of peripheral devices in mobile networks are accelerating, as the number of such devices increases to maintain network coverage with shrinking mobile network cell size and higher user data throughput. A hybrid fiber-wireless network is a promising approach to provide a flexible and high performance solution for short-range (< 1 km) backhaul links deployment in high data traffic areas. Such systems will require the integration of optical and wireless communication transceiver circuits. To address this emerging trend, this thesis presents the design and implementation of optical-to-millimeter-wave (mmW) modulator system-on-a-chip (SoC) using mainstream CMOS technology for supporting low-cost deployment of such network. In this thesis, an optical-to-mmW modulator SoC with a fully integrated 850-nm wavelength

optical receiver front-end and a 60-GHz QPSK modulator is presented for the first time. As the first block in an optical receiver chain, the transimpedance amplifier (TIA) dictates the overall system noise and gain-bandwidth performance. An inverter-based TIA with a multiple-peaking network is proposed to address design challenges of conventional CMOS TIAs. The peaking network effective extends the TIA bandwidth by 2.8 times. A power efficiency of 0.12 pJ/bit is achieved by the optimized inverter based core amplifier. Realized in 65-nm CMOS, the overall optical receiver front-end achieves –3-dBm input sensitivity at 4 Gb/s with 10<sup>-12</sup> BER. The quadrature modulator directly up-converts the de-multiplexed 2-Gb/s I&Q NRZ data to a 4-Gb/s QPSK signal at 60-GHz in the unlicensed mmW band. Our design demonstrates that a small

form factor and low-cost optical-to-mmW modulator can be realized in mainstream CMOS technology to support cost-effective implementation of fiber-wireless networks. In the optical receiver, a clock and data recovery (CDR) unit is required following the TIA front-end for generating a phase-aligned clock to de-serialize the high-speed incoming data for baseband processing. A power-efficient CDR with embedded equalization to achieve error free operation (BER  $< 10^{-12}$ ) up to 26 Gb/s under 13-dB channel loss at Nyquist frequency has been developed. The proposed CDR could be further integrated with the fiber-wireless modulator to realize a complete fiber-wireless SoC.

The design, implementation and characterization results of prototypes are presented in this thesis along with the proposed direction of future work.

# Acknowledgement

The first person I would like to thank is my supervisor Prof. Patrick Yue for giving me the opportunity of exploring high-speed IC design. His vision of technology inspired me a distinctive research area in my PhD study. His in-depth experience with startups and semiconductor industry equipped me with an exclusive mindset for my future career. His strong physique and endless energy motived me to train hard in the gym and work even harder in the office.

Besides my supervisor, I would like to thank the rest of my thesis committee: Prof. Wing-Hung Ki, Prof. Kevin J. Chen, Prof. Lilong Cai and Prof. Shiheng Wang for reviewing my thesis and giving me valuable comments to widen the scope of my research from various perspectives. I also like to thank Prof. Quan Xue for serving as the external committee member and giving me insightful guidance.

I would like to thank my mentor at UCSB Prof. Steve Long for his guidance and encouragement on both technical and personal developments. Prof. Long introduced me to high-frequency circuit design with unlimited patience and encouraged me to explore further in this area. I am deeply indebted to him for his kindness and help.

It has been my honor and pleasure working with many brilliant and dedicated researchers and staffs at HKUST. This thesis was built upon the work done by many Yue group members. I would like to thank Dr. Li Sun, Dr. Quan Pan, Dr. Yan Lu, Zhengxiong Hou, Duona Luo, Liwen Jing, Zhixin Li and Guang Zhu for all their hard work in multiple tape-outs. I also like to thank Prof. Andrew Poon and Dr. Yu Li for generously lending the BERT equipment. Also, Yue group members: Dr. Liang Wu, Fengyu Che, Xianbo Li, Babar Hussain, Haikun Jia, Liusheng Sun, Clarissa Prawoto, Salahuddin Raju, Qasim Maqbool and Xiao Wang for all the inspiring discussions and enjoyable time I had in the last four years. I am also grateful for the friendship with

other IC research groups at HKUST, especially: Dr. Yue Chao, Alvin Li and Zhiqiang Huang of Wireless Communications Integrated Circuits Lab (Analog Research Lab); Dr. Jing Guo of MIXIC Lab; Dr. Cheng Huang, Fan Yang of Integrated Power Electronics Lab and Lexi Ren of Prof. Jonny Sin's group. Thanks must also be given to all conscientious technicians and staffs at HKUST, in particular: S.F. Luk for die cutting and bonding in every project; K.W. Chan and Fred Kwok for their assistance with high frequency measurement and equipment purchase; Kenny Pang for computing server maintenance; Foner Chan for accounting assistance.

I would also like to take this opportunity to thank my friends who accompany me all the way: Songhua Chen, Zhimin Ye, Shao Huang, Naping Zheng, A-xuan Wu, Yi Huang, Dr. Wen Chen, Dr. Yang Li, Dr. Ming Li, Huiying Zhu, Xiaoyu Tan and Miao He. This adventure would be much lonelier and tougher without your support.

Last but not least, I would like to thank my parents, Jinlian Wang and Libin Qiu, for their unconditional support and endless love. Without them, I would not have the freedom and luxury to discover and pursuit my way of life.

# **Table of Contents**

| Abstract     | •••••••••••••••••••••••••••••••••••••••               | v    |

|--------------|-------------------------------------------------------|------|

| Acknowled    | gement                                                | vii  |

| Table of Co  | ontents                                               | ix   |

| List of Figu | res                                                   | xi   |

| List of Tabl | les                                                   | xvi  |

| List of Abb  | reviations                                            | xvii |

| Chapter 1    | Introduction                                          | 18   |

| 1.1 Researc  | h Background                                          | 18   |

| 1.2 Thesis C | Organization                                          | 23   |

| Chapter 2    | CMOS Transimpedance Amplifier                         | 25   |

| 2.1 Introduc | ction                                                 | 25   |

| 2.2 CMOS '   | TIA Design Challenges                                 | 26   |

| 2.3 Propose  | d Multiple Peaking TIA                                | 31   |

| 2.4 Experim  | nental Results                                        | 47   |

| Chapter 3    | Fully Integrated Optical-to-Millimeter-Wave Modulator | 51   |

| 3.1 Introduc | ction                                                 | 51   |

| 3.2 Optical- | to-mmW Modulator System                               | 53   |

| 3.3 Fully In | tegrated Optical Receiver                             | 54   |

| 3.4 60-GHz   | QPSK Modulator                                        | 66   |

| 3.5 Modula   | tor System Experimental Results                       | 72   |

| Chapter 4    | Clock and Data Recovery with Embedded Equalization    | 78   |

| 4.1 Backgro  | ound of CDR                                           | 79   |

| 4.2 Background of Discrete-Time Equalization | 85  |

|----------------------------------------------|-----|

| 4.3 Proposed CDR with Embedded FFE and DFE   | 90  |

| 4.4 Experimental Results                     | 104 |

| Chapter 5 Conclusion and Future Work         | 113 |

| 5.1 Summary of main contributions            | 114 |

| 5.2 Future work                              | 114 |

| Appendix: High-Speed PCB Design              | 116 |

| Bibliography                                 | 118 |

# **List of Figures**

| Fig. 1.1 Global IP traffic estimation by Cisco, 2014–2019 [1]                                                 |

|---------------------------------------------------------------------------------------------------------------|

| Fig. 1.2 Evolution of mobile networks                                                                         |

| Fig. 1.3 Hybrid fiber-wireless network [4].                                                                   |

| Fig. 1.4 Fiber-wireless network architectures [5].                                                            |

| Fig. 1.5 Fiber-wireless modulator architectures.                                                              |

| Fig. 2.1 Schematic of (a) open-loop CG TIA and (b) closed-loop feedback TIA26                                 |

| Fig. 2.2 Output eye diagram of a PRBS sequence after (a) 0.7/T <sub>b</sub> bandwidth low-pass filter and (b) |

| 0.4/T <sub>b</sub> bandwidth low-pass filter                                                                  |

| Fig. 2.3 Noisy PRBS data sequence and its amplitude PDF curves                                                |

| Fig. 2.4 Calculated BER versus SNR [18].                                                                      |

| Fig. 2.5 Schematic of a feedback TIA with inverter or common-source amplifier as the core                     |

| amplifier31                                                                                                   |

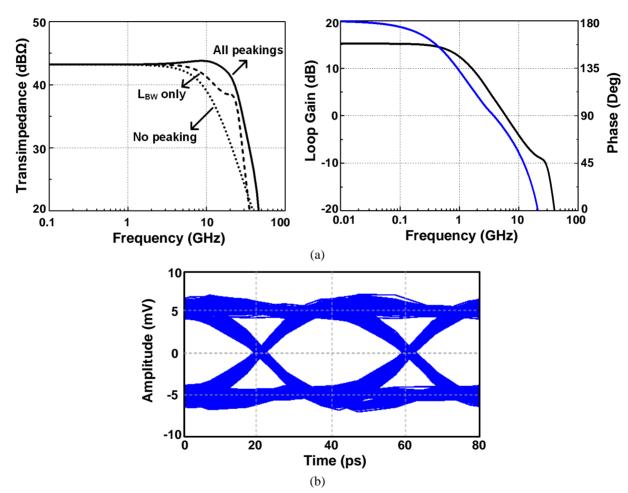

| Fig. 2.6 Simulated frequency response of (a) core amplifier open-loop gain and (b) closed-loop                |

| transimpedance gain                                                                                           |

| Fig. 2.7 Optimization of the inverter transistor sizing for (a) TIA gain and bandwidth and (b) IRN            |

| and power consumption                                                                                         |

| Fig. 2.8 (a) Schematic of first-order peaking networks and (b) simulated step responses36                     |

| Fig. 2.9 (a) Schematic of the proposed TIA, (b) input series peaking network and (c) small-signal             |

| model of the main TIA                                                                                         |

| Fig. 2.10 (a) Simulated frequency response and (b) BWER of the input series peaking network. 39               |

| Fig. 2.11 (a) Simulated BWER, (b) group delay variation and (c) frequency response of the main                |

| TIA41                                                                                                         |

| Fig. 2.12 Post-layout simulation of (a) $Z_T(s)$ frequency response and (b) 25-Gb/s output          | eye   |

|-----------------------------------------------------------------------------------------------------|-------|

| diagram with 50- $\mu$ A <sub>pp</sub> input current and 250-fF $C_{PD}$ .                          | 42    |

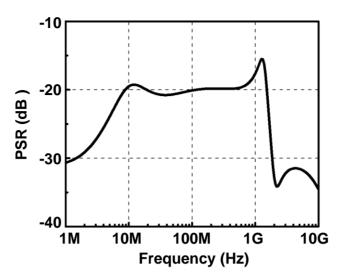

| Fig. 2.13 Schematic of the integrated LDO.                                                          | 44    |

| Fig. 2.14 Simulated LDO PSR.                                                                        | 45    |

| Fig. 2.15 Simulated 25 Gb/s TIA output eye diagram with 100-MHz 10-mV <sub>pp</sub> square-wave sur | pply  |

| noise: (a) with LDO and (b) without LDO.                                                            | 46    |

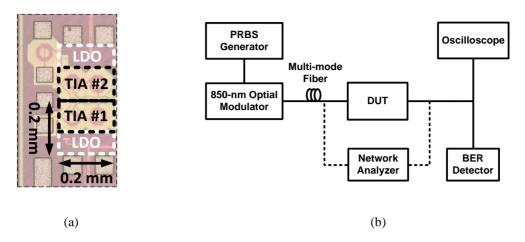

| Fig. 2.16 (a) TIA Chip micrograph and (b) measurement setup.                                        | 47    |

| Fig. 2.17 Measured TIA frequency response by direct on-chip probing.                                | 47    |

| Fig. 2.18 Measured optical eye diagram at 25 Gb/s with (a) LDO enabled (RMS Jitter = 2.6 ps         | s, P- |

| P Jitter = 11.6 ps) and (b) LDO disabled (RMS Jitter = 3 ps, P-P Jitter = 14.4 ps)                  | 48    |

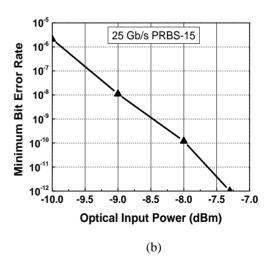

| Fig. 2.19 (a) BER bathtub curve with and without LDO enabled and (b) optical input sensiti          | ivity |

| curve                                                                                               | 49    |

| Fig. 3.1 Comparison between a conventional and the proposed fiber-wireless system                   | 51    |

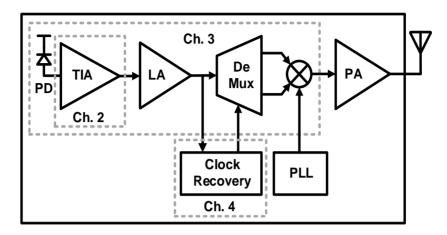

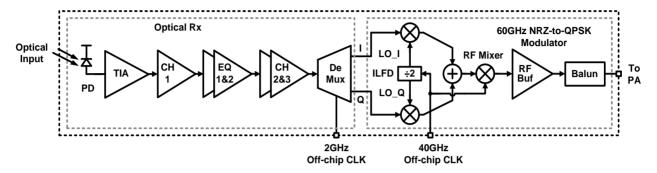

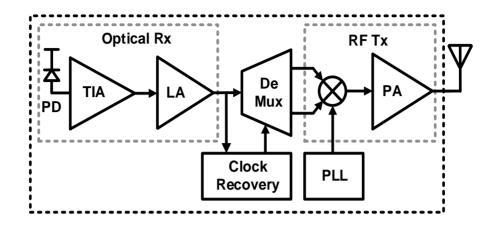

| Fig. 3.2 System diagram of the proposed modulator.                                                  | 53    |

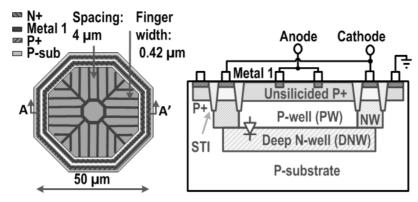

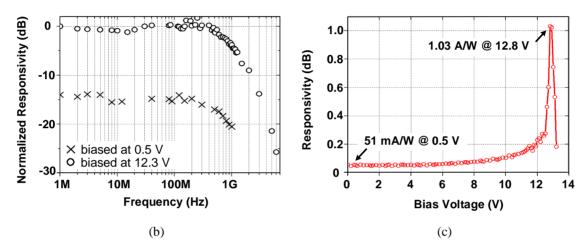

| Fig. 3.3 Layout and cross-section views of the CMOS PW/DNW PD.                                      | 56    |

| Fig. 3.4 (a) Measured PD frequency response and (b) PD responsivity versus biasing                  | 56    |

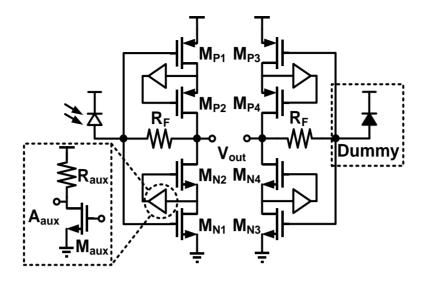

| Fig. 3.5 Schematic of the TIA based on a gain-boosted inverter.                                     | 58    |

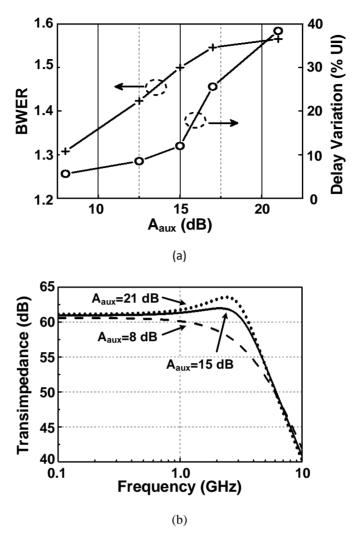

| Fig. 3.6 (a) BWER and group delay variation and (b) closed-loop frequency response                  | 59    |

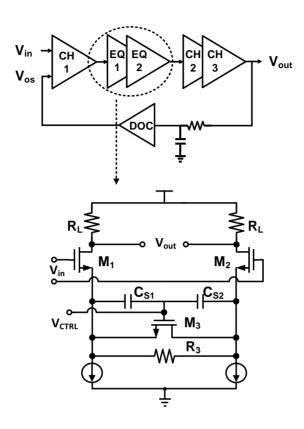

| Fig. 3.7 Schematic of the continuous time equalizer.                                                | 61    |

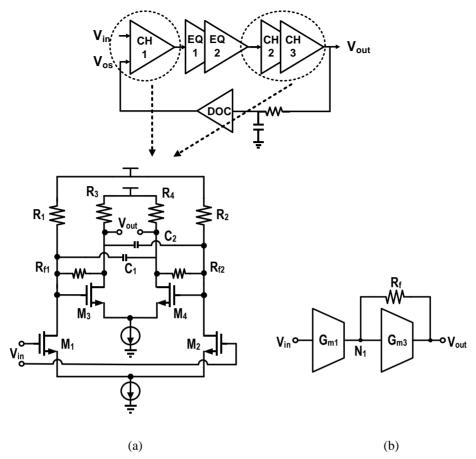

| Fig. 3.8 (a) Schematic of the Cherry-Hooper limiting amplifier and (b) equivalent small si          | gnal  |

| model                                                                                               | 63    |

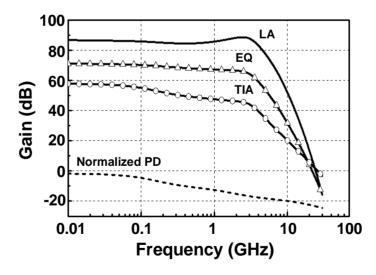

| Fig. 3.9 Simulated progressive frequency response of the optical receiver.                          | 63    |

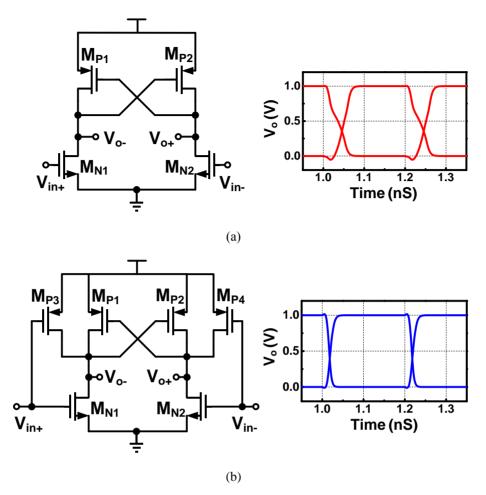

| Fig. 3.10 Schematic and simulated transient waveform of (a) a conventional DCVSL inverter           | and   |

| (b) a modified DCVSL inverter.                                                                      | 65    |

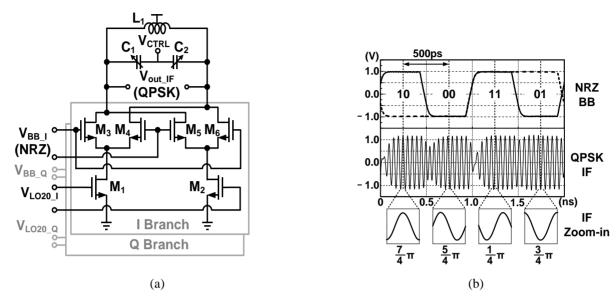

| Fig. 3.11 (a) Schematic of the IF NRZ-to-QPSK modulator and (b) its simulated output way | veforms  |

|------------------------------------------------------------------------------------------|----------|

| illustrating the four QPSK symbols.                                                      | 66       |

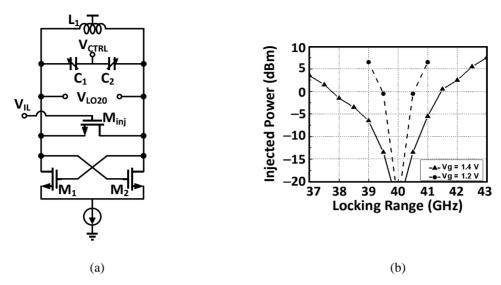

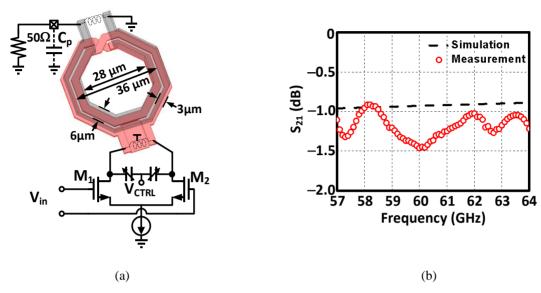

| Fig. 3.12 (a) Schematic of the ILFD and (b) measured locking range                       | 67       |

| Fig. 3.13 (a) Schematic of the output buffer with balun layout and (b) measured balun in | nsertion |

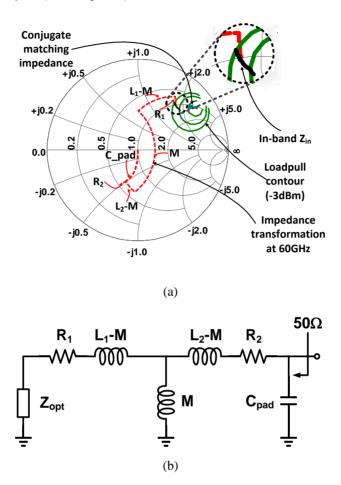

| loss                                                                                     | 68       |

| Fig. 3.14 (a) Matching network rotational path and (b) balun based matching network equ  | ıivalent |

| circuit                                                                                  | 69       |

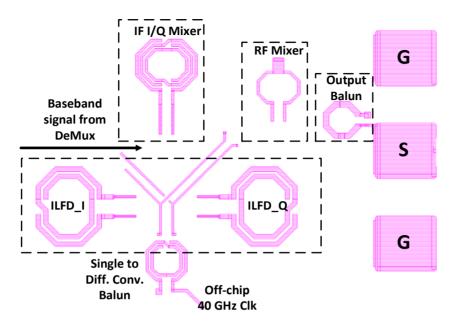

| Fig. 3.15 RF link layout floorplan.                                                      | 70       |

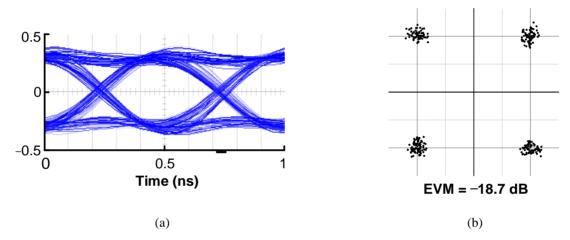

| Fig. 3.16 (a) Simulated 4-Gb/s demodulated eye diagram and (b) constellation diagram     | 71       |

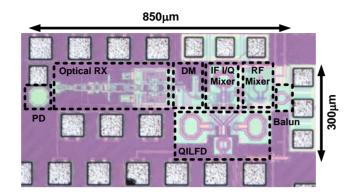

| Fig. 3.17 Fiber-wireless modulator chip micrograph.                                      | 72       |

| Fig. 3.18 Fiber-wireless modulator measurement setup.                                    | 72       |

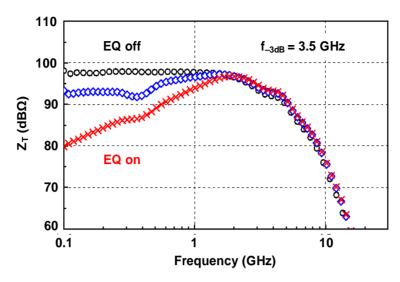

| Fig. 3.19 Measured optical receiver frequency response                                   | 73       |

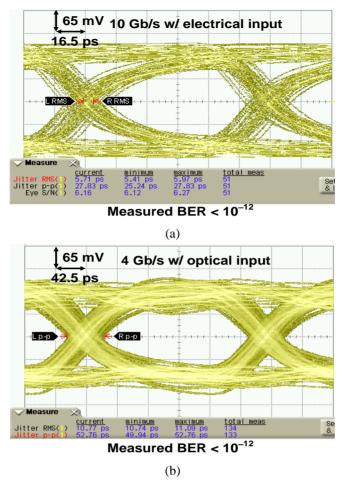

| Fig. 3.20 (a) 10-Gb/s output eye diagram with electrical input and (b) 4-Gb/s output eye | liagram  |

| under 850-nm optical input.                                                              | 74       |

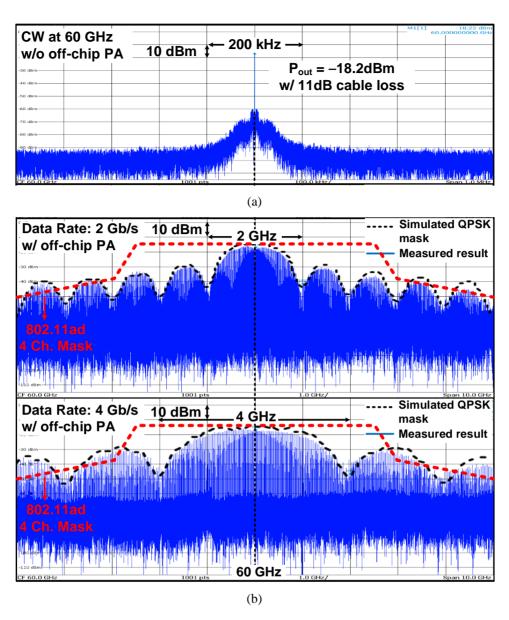

| Fig. 3.21 Measured output spectrum at 60 GHz of (a) CW output and (b) modulated 4-Gb/s   | s QPSK   |

| signal.                                                                                  | 75       |

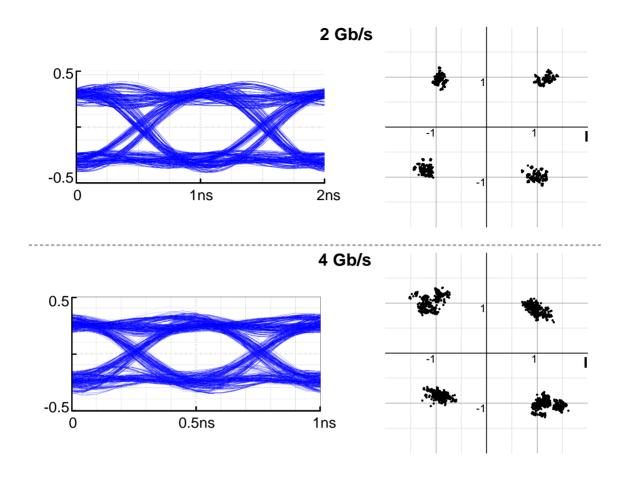

| Fig. 3.22 Measured demodulated eye diagrams and constellation diagram                    | 76       |

| Fig. 4.1 CDR in a fiber-wireless communication system.                                   | 78       |

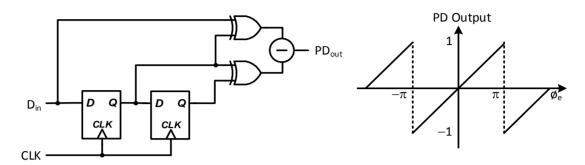

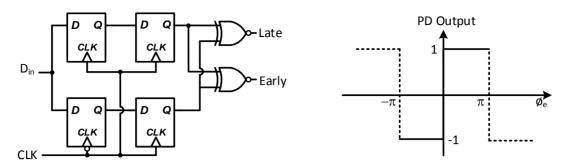

| Fig. 4.2 Linear Hodge phase detector.                                                    | 79       |

| Fig. 4.3 Non-linear Alexander phase detector.                                            | 80       |

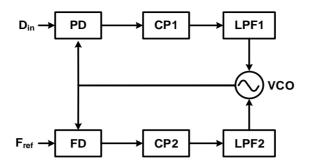

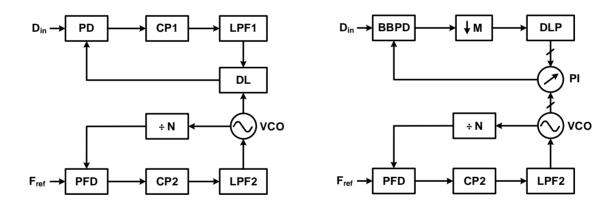

| Fig. 4.4 Block diagram of PLL-based CDR.                                                 | 81       |

| Fig. 4.5 Block diagram of DLL/PI-based CDR.                                              | 81       |

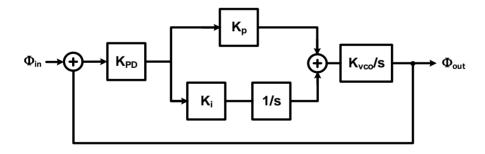

| Fig. 4.6 CDR phase domain model.                                                         | 82       |

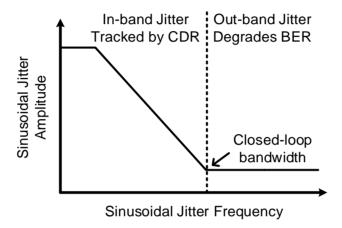

| Fig. 4.7 CDR jitter tolerance mask                                                       | 84       |

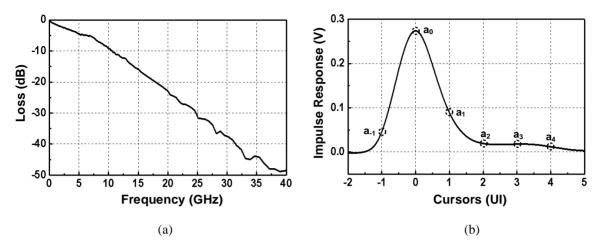

| Fig. 4.8 A lossy channel example: (a) measured channel insertion loss and (b) simulated impulse |

|-------------------------------------------------------------------------------------------------|

| response based on the measured s-parameter85                                                    |

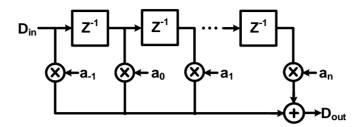

| Fig. 4.9 Block diagram of feed forward equalizer.                                               |

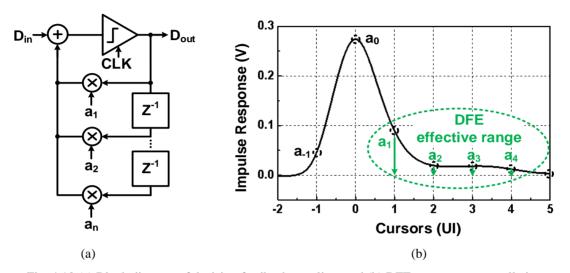

| Fig. 4.10 (a) Block diagram of decision feedback equalizer and (b) DFE post-cursor cancellation |

| 87                                                                                              |

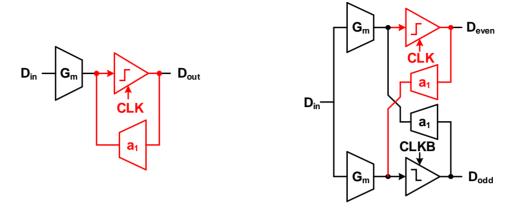

| Fig. 4.11 1-tap full-rate and half-rate direct feedback DFE.                                    |

| Fig. 4.12 1-tap loop-unrolling DFE                                                              |

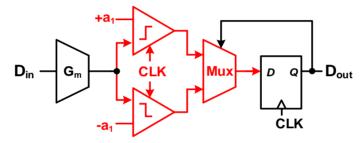

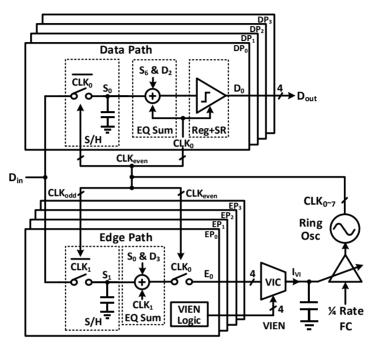

| Fig. 4.13 CDR system block diagram90                                                            |

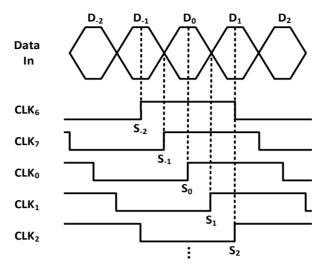

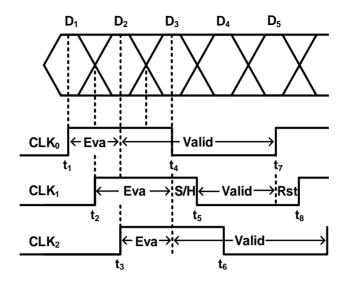

| Fig. 4.14 CDR system timing diagram91                                                           |

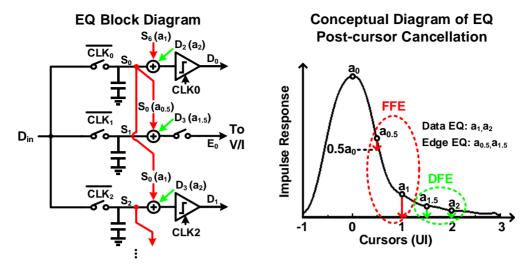

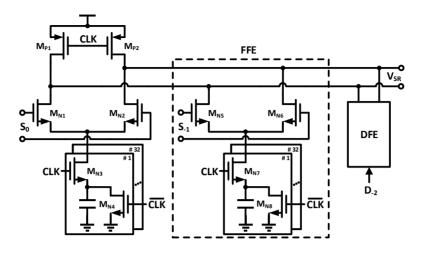

| Fig. 4.15 Block diagram of the embedded FFE and DFE                                             |

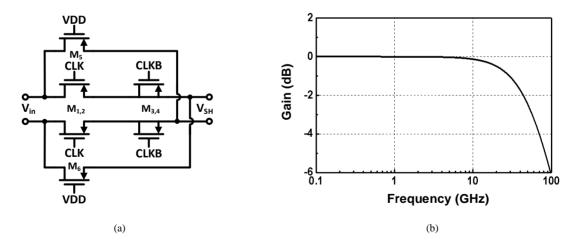

| Fig. 4.16 (a) Schematic of the sampler and (b) simulated frequency response92                   |

| Fig. 4.17 Operation of the charge steering differential pair                                    |

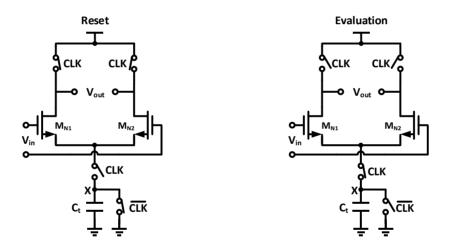

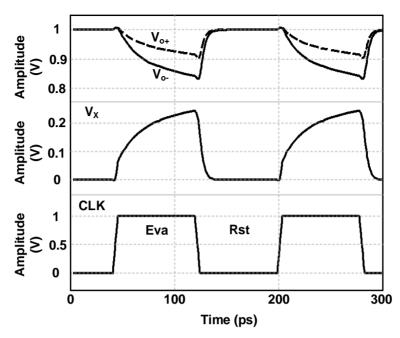

| Fig. 4.18 Simulated transient waveforms of the charge steering amplifier94                      |

| Fig. 4.19 Schematic of the charge-steering summer                                               |

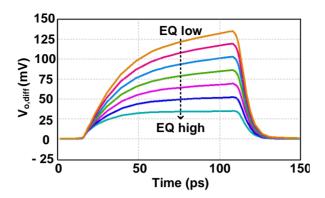

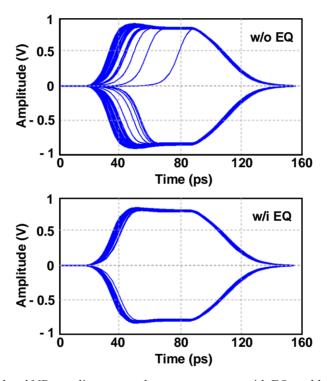

| Fig. 4.20 Simulated transient waveforms of summer differential output under various EQ tap      |

| settings96                                                                                      |

| Fig. 4.21 Simulated NR eye diagrams at the summer output with EQ enabled and disabled96         |

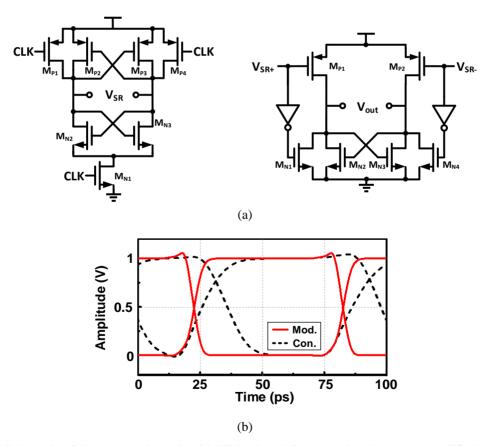

| Fig. 4.22 (a) Schematic of the regeneration pair with SR latch and (b) comparison between a     |

| modified SR latch and a conventional SR latch                                                   |

| Fig. 4.23 Edge transition examples.                                                             |

| Fig. 4.24 Edge path timing diagram.                                                             |

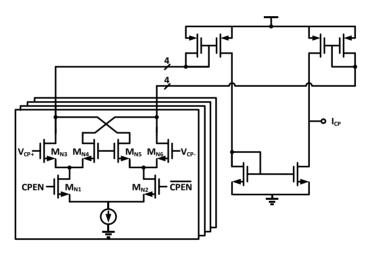

| Fig. 4.25 Schematic of the charge pump.                                                         |

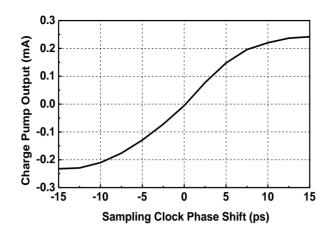

| Fig. 4.26 Simulated edge path transfer curve.                                                   |

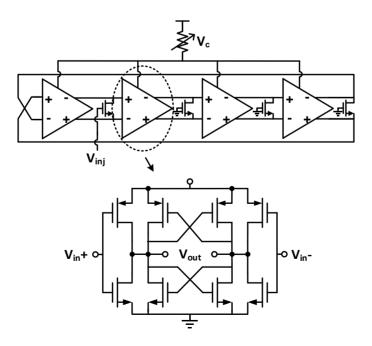

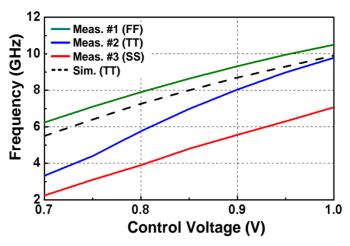

| Fig. 4.27 Schematic of the ring oscillator                                                      |

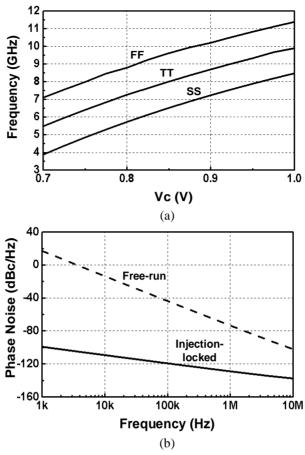

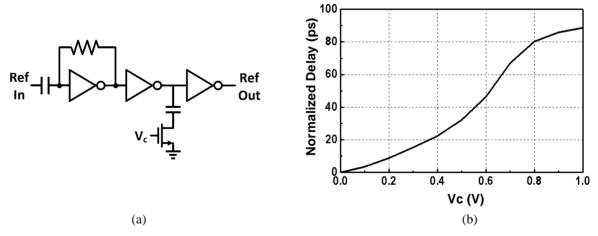

| Fig. 4.28 (a) Simulated ring oscillator frequency tuning range and (b) phase noise        | 102      |

|-------------------------------------------------------------------------------------------|----------|

| Fig. 4.29 (a) Schematic of the reference clock delay line and (b) simulated delay range   | 102      |

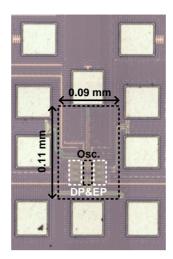

| Fig. 4.30 CDR chip micrograph.                                                            | 104      |

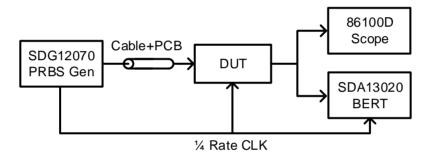

| Fig. 4.31 CDR measurement setup.                                                          | 104      |

| Fig. 4.32 Measured ring oscillator tuning curve.                                          | 105      |

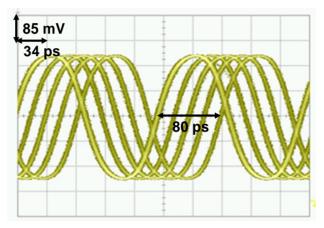

| Fig. 4.33 Measured delay line phase tuning range.                                         | 105      |

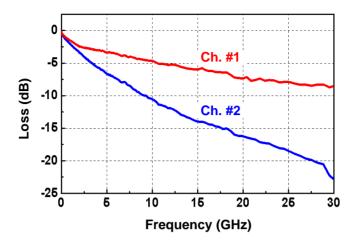

| Fig. 4.34 Measured insertion loss of input channels.                                      | 106      |

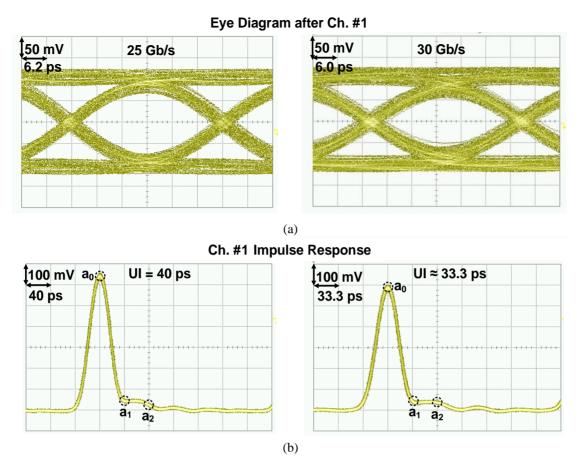

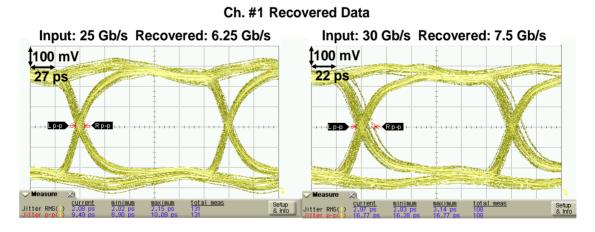

| Fig. 4.35 (a) Eye diagrams of 25 Gb/s and 30 Gb/s data over the channel #1 and (b) char   | nnel #1  |

| impulse responses.                                                                        | 107      |

| Fig. 4.36 Measured recovered data eye diagrams with 25 Gb/s and 30 Gb/s input data o      | ver the  |

| channel #1.                                                                               | 107      |

| Fig. 4.37 Measured BER bathtub curves of the recovered data shown in Fig. 4.36            | 108      |

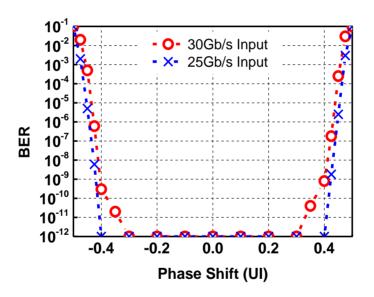

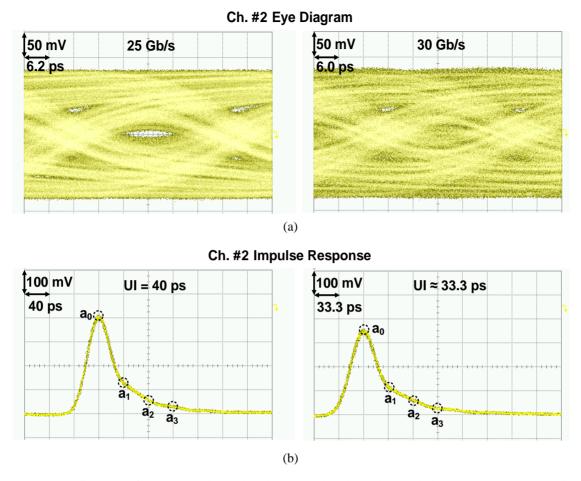

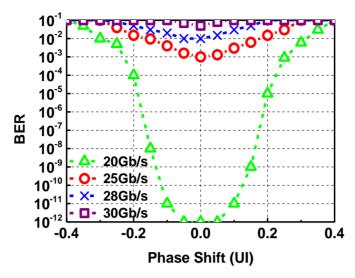

| Fig. 4.38 (a) Eye diagrams of 25 Gb/s and 30 Gb/s data over the channel #2 and (b) me     | easured  |

| channel #2 impulse responses.                                                             | 109      |

| Fig. 4.39 Measured BER bathtub curves for CDR input data over the channel #2              | 110      |

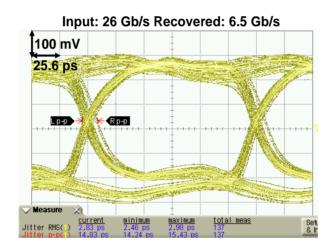

| Fig. 4.40 Measured recovered data eye diagram with 26 Gb/s input over the channel #2      | 110      |

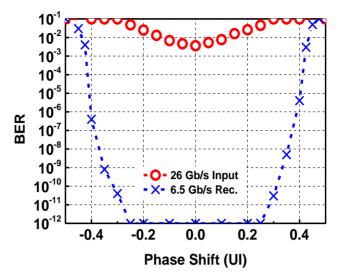

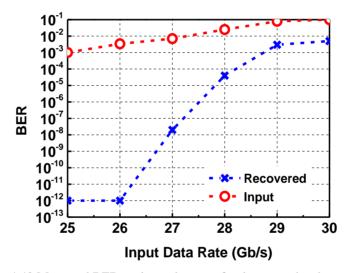

| Fig. 4.41 Measured BER of the 26 Gb/s input data and the 6.5 Gb/s recovered data          | 111      |

| Fig. 4.42 Measured BER vs. input data rate for data over the channel #2                   | 111      |

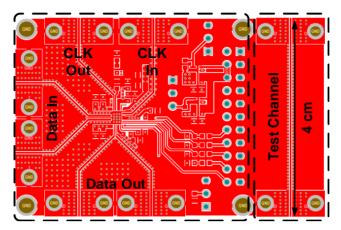

| Fig. A-1 PCB top layer layout view                                                        | 116      |

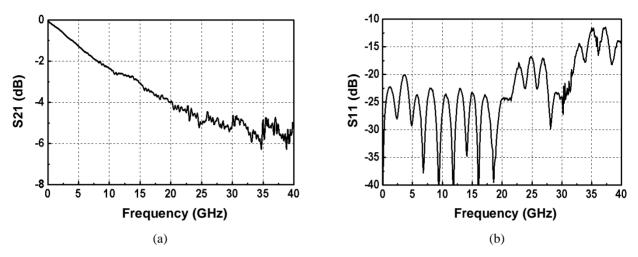

| Fig. A-2 Measurement of the 4cm test channel: (a) insertion loss (S21) and (b) reflection | (S11).   |

|                                                                                           | 117      |

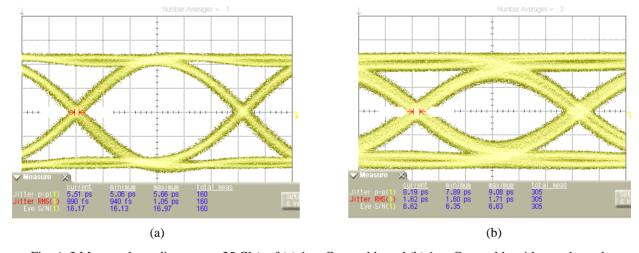

| Fig. A-3 Measured eye diagrams at 25 Gb/s of (a) 1-m Gore cable and (b) 1-m Gore cable w  | ith test |

| channel                                                                                   | 117      |

# **List of Tables**

| Table I Summary of TIA Target Applications                     | 24   |

|----------------------------------------------------------------|------|

| Table II Comparison of Inverter and Common Source Amplifier    | 31   |

| Table III Summary of Multiple Peaking Network                  | 42   |

| Table IV TIA Performance Comparison and Summary                | 50   |

| Table V: Fiber-Wireless Modulator System Performance Breakdown | 54   |

| Table VI: Fiber-Wireless Modulator Performance Comparison.     | 77   |

| Table VII: CDR Performance Comparison.                         | .112 |

# **List of Abbreviations**

| BER                          | Bit error rate                                                                                                                                              | LDO                               | Low dropout regulator                                                                                                                             |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| BERT                         | Bit error rate tester                                                                                                                                       | mmW                               | Millimeter wave                                                                                                                                   |

| BS                           | Base station                                                                                                                                                | NRZ                               | Non-return-to-zero                                                                                                                                |

| BoF                          | Baseband-over-Fiber                                                                                                                                         | NIC                               | Negative impedance compensation                                                                                                                   |

| BW                           | Bandwidth                                                                                                                                                   | OEIC                              | Optoelectronic integrated circuits                                                                                                                |

| BWER                         | Bandwidth enhancement ratio                                                                                                                                 | O/E                               | Optical                                                                                                                                           |

| CDR                          | Clock and data recovery                                                                                                                                     | PLL                               | Phase locked loop                                                                                                                                 |

| CO                           | Central office                                                                                                                                              | PI                                | Phase interpolator                                                                                                                                |

| CML                          | Common-mode logic                                                                                                                                           | PD                                | Photodetector                                                                                                                                     |

| CTLE                         | Continuous-time linear                                                                                                                                      | PRBS                              | Pseudorandom binary sequence                                                                                                                      |

|                              | equalizer                                                                                                                                                   |                                   |                                                                                                                                                   |

| СН                           | Cherry-Hooper                                                                                                                                               | QPSK                              | Quadrature Phase Shift Keying                                                                                                                     |

|                              |                                                                                                                                                             |                                   |                                                                                                                                                   |

| CS                           | Common source                                                                                                                                               | RGC                               | Regulated cascode                                                                                                                                 |

| CS<br>DCVSL                  | Common source Differential cascade voltage                                                                                                                  | RGC<br>RoF                        | Regulated cascode<br>RF-over-Fiber                                                                                                                |

|                              |                                                                                                                                                             |                                   | <b>G</b>                                                                                                                                          |

|                              | Differential cascade voltage                                                                                                                                |                                   | <b>G</b>                                                                                                                                          |

| DCVSL                        | Differential cascade voltage switching logic                                                                                                                | RoF                               | RF-over-Fiber                                                                                                                                     |

| DCVSL<br>DFE                 | Differential cascade voltage<br>switching logic<br>Decision feedback equalizer                                                                              | RoF<br>RZ                         | RF-over-Fiber Return-to-zero                                                                                                                      |

| DCVSL DFE DLL                | Differential cascade voltage<br>switching logic<br>Decision feedback equalizer<br>Delay locked loop                                                         | RoF<br>RZ<br>SoC                  | RF-over-Fiber  Return-to-zero System-on-a-chip                                                                                                    |

| DCVSL DFE DLL EQ             | Differential cascade voltage<br>switching logic<br>Decision feedback equalizer<br>Delay locked loop<br>Equalizer                                            | RoF<br>RZ<br>SoC<br>SNR           | RF-over-Fiber  Return-to-zero System-on-a-chip Signal to noise ratio                                                                              |

| DCVSL  DFE  DLL  EQ  EVM     | Differential cascade voltage<br>switching logic<br>Decision feedback equalizer<br>Delay locked loop<br>Equalizer<br>Error vector magnitude                  | RoF<br>RZ<br>SoC<br>SNR<br>S/H    | RF-over-Fiber  Return-to-zero System-on-a-chip Signal to noise ratio Sample and hold                                                              |

| DCVSL  DFE  DLL  EQ  EVM  FB | Differential cascade voltage switching logic Decision feedback equalizer Delay locked loop Equalizer Error vector magnitude Feedback                        | RoF  RZ  SoC  SNR  S/H  ILFD      | RF-over-Fiber  Return-to-zero System-on-a-chip Signal to noise ratio Sample and hold Injection-locked frequency divider                           |

| DCVSL  DFE DLL EQ EVM FB FFE | Differential cascade voltage switching logic Decision feedback equalizer Delay locked loop Equalizer Error vector magnitude Feedback Feed forward equalizer | RoF  RZ  SoC  SNR  S/H  ILFD  ISI | RF-over-Fiber  Return-to-zero System-on-a-chip Signal to noise ratio Sample and hold Injection-locked frequency divider Inter symbol interference |

# **Chapter 1 Introduction**

## 1.1 Research Background

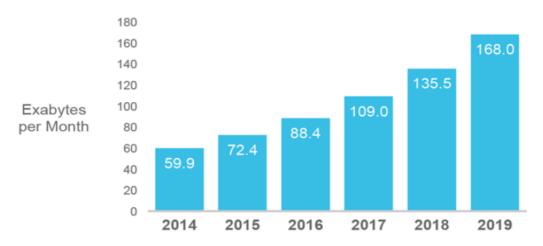

Fig. 1.1 Global IP traffic estimation by Cisco, 2014–2019 [1].

The widespread popularity of mobile internet, multi-media streaming and cloud computing has rapidly increased the requirements for high-speed data communication. According to the Cisco Visual Networking Index Forecast [1], the global data traffic is projected to enter zettabyte (10<sup>21</sup> byte) era in 2016. As shown in Fig 1.1, the monthly global traffic is projected to reach 168 exabytes (10<sup>18</sup> byte) in 2019 at an annual growth rate of 23%. This surge demand on data transmission puts considerable pressure on both wired and wireless communication networks.

For wireline communication systems like metropolitan area network and high-speed local area network, 100 Gigabit Ethernet (GbE) systems are widely deployed and are migrating from 10 lanes of 10 Gb/s to 4 lanes of 25 Gb/s to increase the network I/O density and power efficiency. In addition to wireline links, wireless communication networks play an equally important role in the modern life as the traffic from mobile devices is predicted to exceed the traffic from wired devices by 2016 [1]. Therefore, researchers are exploring new network architectures to meet the consistent growth of data traffic.

#### A. Optical Communication System

The physical transmission media of the 100GbE systems includes cooper cables and optical fibers. Cooper cables like twisted pair and twinax are usually adopted in low-cost short reach applications like rack-to-rack interconnection in data center. The performance of cooper cable is significantly constrained by its high propagation loss. Thus, sophisticated equalization techniques are usually required to achieve high data rate. On the other hand, for applications requiring a bandwidth-distance product larger than 10<sup>4</sup> Gb/s·km, optical fibers are almost mandatory due to its low loss property.

Traditionally, optical transceivers are implemented in expensive III-V technologies [2], [3] to achieve superior performance for high-end applications like long-haul links. In this case, the infrastructure cost is shared by a large number of end-users. However, the emerging high-speed LAN market is much more sensitive to the system cost as the demand for the high-performance data traffic has gradually migrated from telecom infrastructures to cost-sensitive enterprise applications and consumer electronics. In the meanwhile, the system form factor and power dissipation are also strictly regulated in order to fit into existing mechanical packages like SFP and CFP2. Therefore, developing a cost-effective, low power optical I/O solution is critical for next generation high-speed wireline communication network.

To achieve above mentioned criteria, optical transceivers implemented in the standard CMOS technology draw great attention in recent years. Compared to traditional optical communication systems realized in the III-V technologies, CMOS monolithic optoelectronic integrated circuits (OEICs) ensure low-cost, small system form factor and high volume manufacturing capacity. However, the performance of OEICs is usually inferior. For example, the receiver sensitivity and achievable data rate are severely constrained by the responsivity and bandwidth of the on-chip

photodetector, insufficient device transit frequency and large noise. Therefore, advancements on both circuit level and device level are required to further push the performance of OEICs.

#### **B.** Wireless Communication System

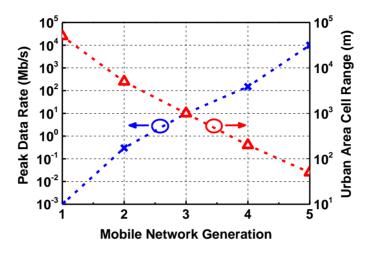

Fig. 1.2 Evolution of mobile networks.

In addition to the advancement in wireline networks, the urgent demand for the multi-gigabit wireless communication and the exhausted spectrum resource draw great attention to the next generation mobile network. Fig. 1.2 shows the evolution of the mobile network peak data rate and cell coverage range. The peak data rate rises rapidly from 300 kb/s in 2G to the proposed 10 Gb/s in 5G. To realize this exponential growth in data rate, the cell coverage range shrinks significantly from 5 km in 2G to the projected 50 m (Femtocell [4], [5]) in 5G for improving link SNR, latency, spectrum efficiency and network capacity. However, forwarding the wireless data traffic to the backhaul network is challenging when such an ultra-dense network is deployed.

Recent researches have demonstrated that the 60-GHz band could be used to accomplish mmW backhaul links [6], [7] to resolve the great challenge of forwarding wireless traffic to core networks in the 5G network. The widely available bandwidth, low latency and directional propagation property make 60-GHz band a suitable candidate for the multi-gigabit wireless

backhaul link. The high oxygen absorption characteristic can also be utilized to construct high density network without significant interference issue between cells.

#### C. Fiber-Wireless Communication System

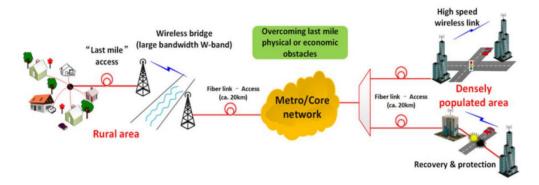

Fig. 1.3 Hybrid fiber-wireless network [4].

Over the last decade, much research has been conducted on the hybrid fiber-wireless network [7]-[9] to explore the alternative backhaul network architecture for the next generation ultra-dense mobile network. Conventionally, the use of optical backhaul link is necessary to reach the demanded data throughput between BS and pico-cells. However, wired connection between BS and pico-cells is sometimes physically impractical or costly in rural or densely populated areas as shown in Fig. 1.3. In these cases, a hybrid fiber-wireless network is desirable to provide a flexible and high performance solution for short-range backhaul links deployment.

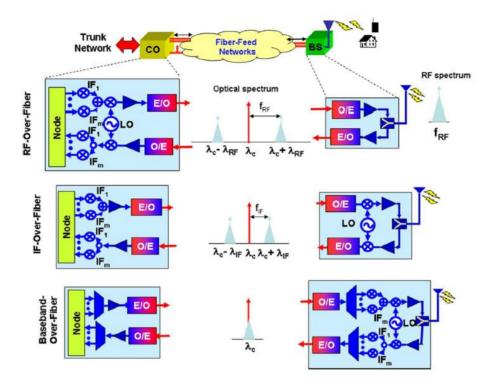

The physical implementation of a fiber-wireless network varies considerably as shown in Fig. 1.4. For example, the RF-over-Fiber (RoF) scheme directly transmits modulated RF signal through optical links. In this architecture, the RF modulation is conducted at the central office (CO). The remote BS and pico-cells only perform optical-to-electrical (O/E) conversion and RF transmission. Even though the overhead of RF modulations is eliminated at remote cells, the RoF scheme requires high-speed high-linearity optical links, resulting in costly and bulky system. In contrast, an alternative solution is called Baseband-over-Fiber (BoF). The BoF scheme transmits

Fig. 1.4 Fiber-wireless network architectures [5].

the baseband signal between CO and BS in the optical domain and up-converts the signal to the mmW band for wireless transmission between cells. Compared to the RoF scheme, the BoF system eliminates the need for high performance optical links since only the baseband signal is transmitted in the optical domain. However, energy efficient and cost effective O/E conversion and RF transmission systems at remote cells are necessary for the BoF network to outperform the RoF network. Therefore, an integrated module capable of directly converting signals between the optical and the mmW domain is needed to reduce the overhead in system size and cost for supporting fiber-wireless backhaul links.

# 1.2 Thesis Organization

Fig. 1.5 Fiber-wireless modulator architectures.

The remainder of this thesis focuses on the design and implementation of sub-systems of a fiber-wireless modulator as shown in Fig. 1.5. Chapter 2 presents a power efficient CMOS transimpedance amplifier as the foundation of a CMOS optical receiver design. Chapter 3 focuses on a fully integrated optical-to-wireless modulator to demonstrate the feasibility of a low-cost fiber-wireless hybrid system. Chapter 4 extends the research scope to the clock and data recovery circuit which is essential for a complete fiber-wireless communication system. Finally, Chapter 5 concludes the thesis and propose directions for the future work.

A summary of target applications for TIAs presented in Chapter 2 and 3 is shown in Table I. The TIA in Chapter 2 is targeted at high-speed long reach applications like 100 Gigabit Ethernet (GbE). Therefore, it is optimized for high gain-bandwidth product and sensitivity. On the other hand, the TIA presented in Chapter 3 is part of the optical frontend in a short-reach BoF link. To achieve a compact and low-cost fully integrated BoF modulator design, this TIA is optimized for low power consumption and small chip area.

**Table I Summary of TIA Target Applications**

|                          | TIA in Ch. 2 | TIA in Ch. 3         |

|--------------------------|--------------|----------------------|

| Application              | 100GbE       | Short reach BoF link |

| Data Rate (Gb/s)         | 25           | 4                    |

| Max. Distance (km)       | 10           | 0.2                  |

| Optical Wavelength (nm)  | 1550         | 850                  |

| Fiber                    | SMF          | MMF                  |

| Target Sensitivity (dBm) | -10          | -5                   |

# **Chapter 2 CMOS Transimpedance Amplifier**

#### 2.1 Introduction

A transimpedance amplifier (TIA) converts an input current to an output voltage. Compared to a voltage-mode amplifier, a TIA exhibits a low input impedance to overcome the bandwidth limitation due to the large parasitic capacitance of the photodetector (PD). Meanwhile, the transimpedance gain ( $Z_{TIA}$ ) for converting the input PD current to the voltage needs to be large to suppress the input-referred noise contributed by subsequent stages in the receiver. Furthermore, a TIA should be designed with a bandwidth that is just sufficiently large to eliminate the intersymbol-interference (ISI) while avoiding excessive in-band integrated noise.

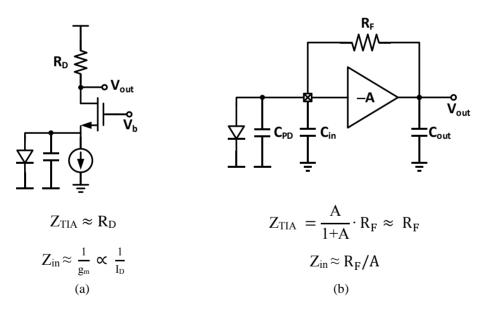

In general, TIAs can be categorized as open-loop or closed-loop architecture. The open-loop TIAs extend bandwidth by inserting a common gate transistor to provide a low input impedance and isolation between the photodetector capacitance (C<sub>PD</sub>) and the transimpedance resistor. Despite its simplicity and robustness, the conventional open-loop topology suffers from a difficult trade-off between the Z<sub>TIA</sub> and output voltage headroom. Even though the regulated cascode (RGC) technique [10] can be employed to alleviate such shortcomings, the added devices in the local feedback loop introduce additional noise and hence degrade input sensitivity. Moreover, in scaled CMOS technologies, the single-stage common source (CS) amplifier employed in the RGC local feedback loop can only provide moderate gain and hence making RGC design less effective. In contrast, the closed-loop TIAs utilize shunt-shunt feedback to reduce their input impedance [11]-[13]. Since the feedback resistor does not carry any bias current, the trade-off between the Z<sub>TIA</sub> and output headroom is greatly relaxed. In particular, closed-loop TIAs utilizing negative impedance compensation (NIC) [11] and active feedback [12] have been reported to extend the gain-bandwidth product (GBW). However, the bandwidth boosting effect of NIC diminishes at

frequencies beyond 10 GHz while the active feedback technique suffers from excess power consumption and stability issue. Although equalization techniques [14]-[15] have been demonstrated to extend the TIA bandwidth, power penalty and ripples in the frequency response of multi-stage equalizers can be severe. Therefore, bandwidth enhancement techniques are still of great value for broadband low-power TIA design.

This section presents a low-power, broadband, inverter-based TIA design for 100GbE applications. employing input series peaking and shunt-shunt inductive feedback to boost the bandwidth by 2.8 times to 24 GHz in 65-nm CMOS process.

# 2.2 CMOS TIA Design Challenges

#### 2.2.1 Supply Voltage Constrain

Fig. 2.1 Schematic of (a) open-loop CG TIA and (b) closed-loop feedback TIA.

CMOS TIAs designed in advanced technologies suffer from the ever decreasing supply voltage since the transistor threshold voltage does not reduce proportionally with the supply voltage. The limited headroom significantly constrains the achievable transimpedance gain and input impedance.

Therefore, the choice of TIA architecture under various process nodes and power supply voltages could be quite different.

Fig. 2.1 shows the schematic of open-loop and closed-loop TIAs. For the open-loop architecture, the transimpedance gain ( $Z_{TIA}$ ) is approximately equal to  $R_D$  at low frequencies. However, the input impedance of the open-loop TIA is inversely proportional to the common-gate device transconductance so as the bias current  $I_D$ . Therefore, a direct trade-off between  $Z_{TIA}$  and  $Z_{in}$  is observed if the supply voltage is low.

In contrast, the closed-loop TIA shown in Fig. 2.1(b) utilizes the shunt-shunt feedback to reduce the input impedance. Since the feedback resistor ( $R_F$ ) does not carry any bias current, the trade-off between the  $Z_{TIA}$  and the output headroom is greatly relaxed. However, the insufficient open-loop gain of the core amplifier in advanced technology nodes limits the effectiveness of the feedback on bandwidth extension.

#### 2.2.2 Bandwidth Requirement

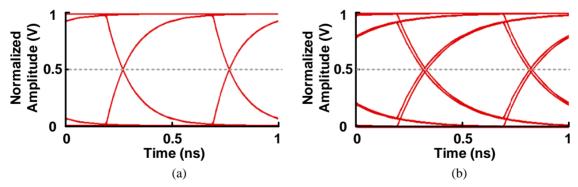

Fig. 2.2 Output eye diagram of a PRBS sequence after (a)  $0.7/T_b$  bandwidth low-pass filter and (b)  $0.4/T_b$  bandwidth low-pass filter.

The finite bandwidth of TIAs limits the maximum transition speed of the input data and degrades the time margin of the system. In time domain, the insufficient bandwidth causes a spreading of the data pulse beyond its time interval. This spreading leads to an unwanted interference between each incoming bit, which is called inter symbol interference (ISI).

A simple RC low-pass filter can be used to model the effect of ISI in the first order. The amplitude distortion of a RC network with PRBS data input is given by

$$V_o - V_{out}(T_b) = V_o e^{-T_b/\tau},$$

(2-1)

where  $V_o$  is the input amplitude and  $V_{out}$  is the output amplitude after one bit period,  $T_b$  is the input data bit period and  $\tau$  is the filter's RC time constant. If the filter bandwidth is chosen as  $f_{-3dB} = 0.7/T_b$ , the total eye closure introduced by the low pass filter is only 2.5% as shown in Fig. 2.2(a). On the other hand, the eye closure introduced by the low pass filter would be about 30% when  $f_{-3dB} = 0.4/T_b$  as shown in Fig. 2.2(b).

The timing jitter introduced by the finite bandwidth can also be analyzed by the RC filter in the first order under two boundary conditions of the input data sequence. The first boundary condition is an input data sequence consists of a logic one preceded by a long consecutive sequence of logic zero. In this case, the threshold crossing time instant  $T_1$  is

$$T_1 = \tau ln2. \tag{2-2}$$

The other boundary condition is an input data sequence consists of a logic zero in between two long consecutive sequences of logic one. Due to the insufficient bandwidth, the circuit is not capable of responding to the sudden change. Thus, the RC filter output does not have enough time to settle to the stable logic level but rise again after 1UI. This slow response makes the threshold crossing time instant  $T_2$  happens much earlier than the  $T_1$  in the first case and leads to timing jitter. The  $T_2$  is expressed as

$$T_2 = \tau ln 2 \left[ 2 \left( 1 - e^{-\frac{T_b}{\tau}} \right) \right]. \tag{2-3}$$

The difference between  $T_1$  and  $T_2$  can be considered as the peak-to-peak jitter at the crossing point. In practice, the targeted TIA bandwidth is a trade-off between power consumption, chip area, ISI as well as total in-band integrated noise. Since practical TIA structures inevitably contain multiple poles and experience PVT variations, a bandwidth around  $0.7/T_b$  is usually chosen as the design starting point. The actual optimal bandwidth should be determined by careful time-domain simulations.

In addition to the limited bandwidth, the phase linearity of TIA frequency response also plays an important role in reducing ISI. Poor phase linearity results in distortions in the form of data dependent jitter[16]-[18]. The phase linearity is characterized as group delay given by

$$\tau = -\frac{d\emptyset(\omega)}{d\omega}. (2-4)$$

In generally, the maximum group delay variation is controlled to be less than 10% of the bit period over the specified bandwidth to void introducing excessive jitter.

#### 2.2.3 Noise and Sensitivity

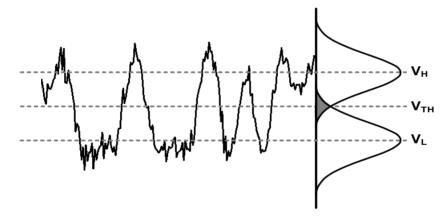

Fig. 2.3 Noisy PRBS data sequence and its amplitude PDF curves.

The noise of a TIA usually determines the achievable input sensitivity of an optical receiver since it is not degenerated by any preceding stage. The noise performance of a TIA can be quantified by its input referred noise current  $I_{n,in}$  by dividing the rms output noise voltage by the squared TIA midband transimpedance gain. The influence of noise on the NRZ data can be modeled as shown in Fig. 2.3 assuming the additive noise exhibits a Gaussian distribution. Thus, a bit error occurs when the logic high or low level erroneously crosses the decision threshold ( $V_{TH}$ ).

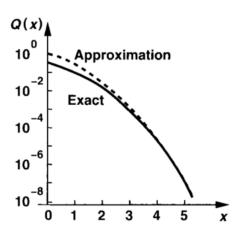

The overlapped region of the amplitude distribution PDF curves shown in Fig. 2.3 indicates the error probability. The probability of bit error can be estimated from the SNR at the TIA input node (ratio of input signal current and input referred noise current) and derived from the "Q function"[18]:

$$Q(x) = \int_{x}^{\infty} \frac{1}{\sqrt{2\pi}} exp \frac{-u^2}{2} du, \qquad (2-5)$$

$$P_{tot} = Q(\frac{I_{pp}}{2I_{n,in}}) \tag{2-6}$$

where  $P_{tot}$  is the error probability,  $I_{pp}$  is the signal peak-to-peak amplitude and  $I_{n,in}$  is the rms input referred noise current. Fig. 2.4 shows the calculated curve of  $P_{tot}$  versus SNR. To achieve a BER <  $10^{-12}$ , a SNR > 7 is generally required.

Fig. 2.4 Calculated BER versus SNR [18].

## 2.3 Proposed Multiple Peaking TIA

A closed-loop feedback TIA design based on an optimized inverter core amplifier and a multiple inductive peaking scheme [19] is proposed in this work. The multiple peaking scheme negates the capacitive loading of the PD input bond pad and the inverter amplifier to achieve bandwidth enhancement ration of 2.8. Moreover, an on-chip LDO with full-spectrum PSR [20] is employed to improve the TIA sensitivity by minimizing supply noise at the point-of-load and to alleviate parasitic effect due to power supply bond-wire inductance.

## 2.3.1 Inverter Based Core Amplifier Optimization

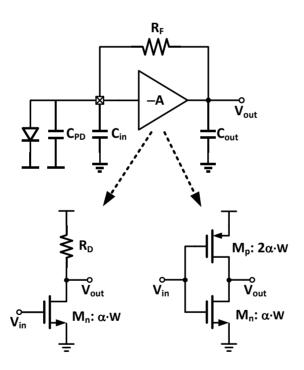

Fig. 2.5 Schematic of a feedback TIA with inverter or common-source amplifier as the core amplifier.

**Table II Comparison of Inverter and Common Source Amplifier**

|           | Low Frequency Gain              | Unity Gain Bandwidth    |

|-----------|---------------------------------|-------------------------|

| Inv. Amp. | $2g_m \cdot (r_{on} // r_{op})$ | $2g_m/(2\pi\cdot 3C_X)$ |

| CS Amp.   | $g_m \cdot R_D$                 | $g_m/(2\pi\cdot C_X)$   |

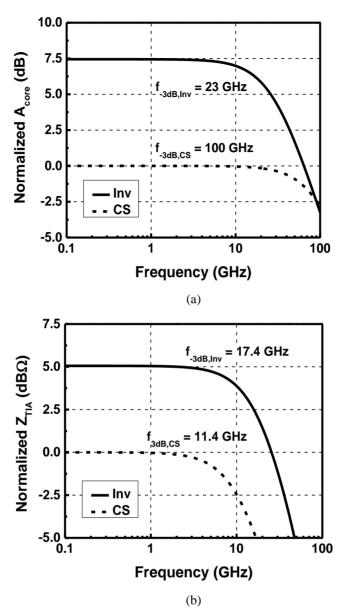

The open-loop gain of the TIA core amplifier strongly affects the effectiveness of the feedback on bandwidth extension. Therefore, it is critical to optimize the core amplifier especially under low supply voltage. Fig. 2.5 shows the schematic of a feedback TIA adopting two typical core amplifier topologies, namely, a common source (CS) amplifier and an inverter-based amplifier. To compare their properties and performance, both core amplifiers are biased under the same current and hence equal power consumption. The PMOS transistors are sized to provide the same transconductance  $(g_m)$  as NMOS transistors  $(W_p = 2W_n)$  in this case). A summary of the first-order gain and bandwidth expression for two core amplifiers is listed in Table I, where  $r_{on}$  and  $r_{op}$  are the output resistance of NMOS and PMOS transistors and  $C_X$  is the equivalent parasitic capacitance for each unit size transistor, respectively. Since the loading resistor  $R_D$  in the CS amplifier is usually limited to few hundred ohms when  $M_n$  is biased with high current for large  $g_m$  and  $f_n$ , the intrinsic output impedance of the inverter amplifier  $(r_{on} / / r_{op})$  is larger than the  $R_D$ . Thus, the CS amplifier has an inferior low-frequency gain compared to the inverter amplifier counterpart, as shown in Fig. 2.6(a). However, the extra capacitance loading from the PMOS transistor in the inverter amplifier limits its -3-dB bandwidth to be 4 times lower compared to the CS amplifier.

In order to analyze and quantify the trade-off between two core amplifiers, two feedback TIAs are designed based on them. The feedback TIA transimpedance gain is expressed as

$$Z_{TIA}(s) = R_F \cdot \frac{A_{core}(s)}{A_{core}(s) + sR_FC_{tot} + 1},$$

(2-7)

where  $R_F$  is the feedback resistor,  $A_{core}(s)$  is the core amplifier's open-loop gain response and  $C_{tot}$  is the total capacitance at the input node consisting of PD capacitance  $C_{PD}$  and parasitic capacitance of the core amplifier  $C_{in}$ . Then, the TIA's -3-dB bandwidth is given by

$$f_{-3dB, TIA} = \frac{A_{core}}{2\pi (R_F C_{tot} + 1/f_{-3dB, core})},$$

(2-8)

where  $A_{core}$  is the core amplifier's low-frequency gain and  $f_{-3dB,\,core}$  is the -3-dB bandwidth of

Fig. 2.6 Simulated frequency response of (a) core amplifier open-loop gain and (b) closed-loop transimpedance gain. the core amplifier. Since the  $R_FC_{tot}$  is usually much larger than the  $1/f_{-3dB,\,core}$ , Eq. (2-8) can be simplified to

$$f_{-3dB,TIA} \approx \frac{A_{core}}{2\pi (R_F C_{tot})} \ . \tag{2-9}$$

Eq. (2-9) leads to the design insight that  $A_{core}$  is more crucial for boosting TIA's bandwidth as long as the  $f_{-3dB, core}$  is sufficiently higher than the dominant pole  $1/2\pi(R_FC_{tot})$ . Fig. 2.6(b) shows the simulated frequency response of two feedback TIAs with core amplifiers designed above (with

their frequency response shown in Fig. 2.6(a). As predicted, the -3 dB bandwidth of the TIA with an inverter amplifier outruns by 6 GHz. In the meanwhile, its transimpedance gain is also 5 dB higher than the CS amplifier counterpart. Above analysis illustrates the superiority of an inverter as a core amplifier of a feedback TIA since it provides a higher low-frequency gain with a sufficient bandwidth in advanced technology.

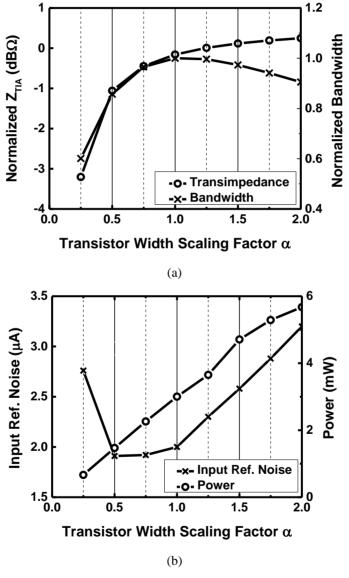

The optimization of the inverter sizing as the core amplifier in a feedback TIA design is studied next. To facilitate the analysis, a transistor width scaling factor  $\alpha$  is introduced. With  $\alpha$ , Eq. (2-9) can be rewritten as

$$f_{-3dB, TIA} \approx \frac{A_{core}}{2\pi R_F (C_{PD} + \alpha C_{in})},$$

(2-10)

where

$$A_{core} = \alpha G_m \cdot \left(\frac{R_o}{\alpha} // R_F\right)$$

(2-11)

is the low-frequency open-loop gain of the inverter amplifier.  $C_{in}$ ,  $G_m$  and  $R_o$  represent the input capacitance, small-signal transconductance and output resistance of the inverter, respectively. Although the inverter amplifier intrinsic gain  $(G_m R_o)$  is independent of  $\alpha$ , the extra loading from the feedback resistor  $(R_F)$  degrades  $A_{core}$  and thus  $Z_{TIA}$  when the transistors are undersized with  $\alpha < 1$ . The dependence of the low-frequency  $Z_{TIA}$  on  $\alpha$  is plotted in Fig. 2.7(a). When  $\alpha > 1$ , the  $Z_{TIA}$  reaches a plateau as  $A_{core}$  is saturated at  $G_m R_o$ . However, with  $\alpha > 1$ , the bandwidth suffers due to the extra parasitic capacitance. At the same time, more power is wasted, as shown in Fig. 2.7(b). Therefore, the transistor size should be optimized such that the open-loop gain is sufficiently high and thus the low-frequency  $Z_{TIA}$  saturates around  $R_F$ . For noise consideration, the input referred noise (IRN) current is plotted against  $\alpha$  in Fig. 2.7(b). The minimum IRN is observed when  $\alpha = 0.5$ , below which the IRN increases due to the reduced transimpedance gain. The IRN remains near its minimum level up to  $\alpha = 1$  because the total output noise and  $Z_{TIA}$  increase at nearly the same rate. Above  $\alpha = 1$ , the shrinkage in bandwidth causes IRN to increase as the high-

frequency noise is less suppressed when referred to the input as equivalent noise current. Using the 65-nm CMOS general purpose process device models, the optimized inverter amplifier design is achieved when  $\alpha = 1$  with  $(W/L)_n = 20\mu/60n$  and  $(W/L)_p = 50\mu/60n$ , respectively. This corresponds to the  $G_m/I_{bias}$  ratio of 7 mS/mA and  $G_mR_o$  of 8.5 at a current density of 125  $\mu$ A/ $\mu$ m in optimal bias range for maximizing  $f_t$ .

Fig. 2.7 Optimization of the inverter transistor sizing for (a) TIA gain and bandwidth and (b) IRN and power consumption.

## 2.3.2 Bandwidth Enhancement Technique

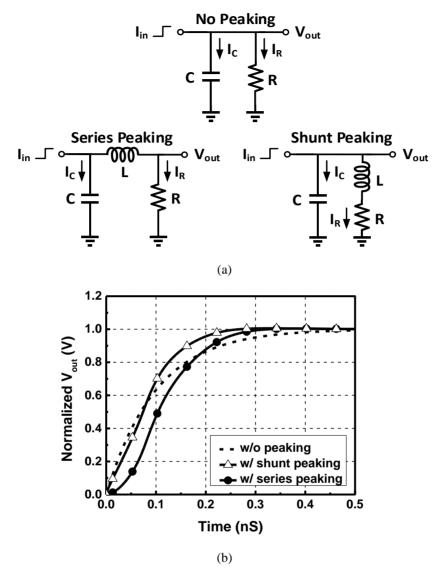

Fig. 2.8 (a) Schematic of first-order peaking networks and (b) simulated step responses.

The inductive peaking technique has been widely adopted to extend circuit bandwidth without power penalty [21], [22]. Before addressing the proposed multiple peaking bandwidth enhancement technique, it is beneficial to review the simple first-order series peaking and shunt peaking structures as depicted in Fig. 2.8. For a RC network stimulated by a step current input ( $I_{in}$ ), the output voltage ( $V_{out}$ ) takes a rising time delay ( $\tau_r$ ) to reach the steady-state voltage ( $I_{in}R$ ) due to

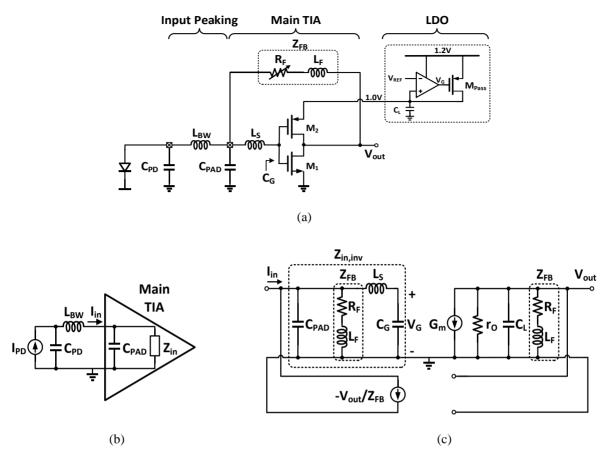

Fig. 2.9 (a) Schematic of the proposed TIA, (b) input series peaking network and (c) small-signal model of the main TIA.

the existence of the loading capacitor (*C*). Since a higher bandwidth is equivalent to having a smaller  $\tau_r$  in time domain, it would be of great interest to reduce the  $\tau_r$  for any broadband circuit. Consider the case that the resistor can be disconnected from the network before the capacitor is fully charged. In this way, all of the  $I_{in}$  would charge the capacitor such that  $\tau_r$  is minimized to  $\tau_{rl} = 0.8RC$  compared to  $\tau_{r0} = 2.2RC$  in the normal case [23]. The rising time is greatly reduced by the so-called "sequential charging technique", which leads to a higher bandwidth. Despite its effectiveness of the "sequential charging technique", it is impractical to implement a switch disconnecting the resistor precisely. However, we can still imitate this method by using an inductor in series with the resistor. Since an inductor tends to resist the high-frequency current change across it, a larger portion of  $I_{in}$  would charge the capacitor instead of flowing through the resistor and

extends the effective bandwidth. Depending on the node of output, they are known as series or shunt peaking as shown in Fig. 2.8.

Based on the above understanding of first-order peaking networks, a TIA with multiple inductive peaking network is proposed to boost the TIA gain-bandwidth product. As shown in Fig. 2.9(a), the large PD capacitance is isolated by an input series peaking inductor  $L_{BW}$ . In addition, the shunt feedback inductor  $L_F$  and the second series peaking inductor  $L_S$  further extend the bandwidth of the inverter core amplifier. The proposed TIA can be analyzed in two parts: the input series peaking network and the main TIA. The total transimpedance  $Z_T(s)$  is given by

$$Z_{T}(s) = \frac{V_{out}}{I_{PD}} = \frac{I_{in}}{I_{PD}} \cdot \frac{V_{out}}{I_{in}} = H_{s, in}(s) \cdot Z_{TIA, main}(s), \tag{2-12}$$

where  $H_{s,in}(s)$  is the current-mode transfer function of the input series peaking network and  $Z_{TIA,main}(s)$  is the transimpedance gain of the main TIA.

As depicted in Fig. 2.9(b), an equivalent circuit of the input series peaking network is utilized to derive  $H_{s,in}(s)$ . The series peaking inductor  $L_{BW}$  inserted at the input node of the TIA isolates the photodetector capacitor  $C_{PD}$  and the main TIA, which delays the current flowing into the main TIA and hence reduces the rising time. The transfer function from  $I_{PD}$  to  $I_{in}$  can be derived as

$$H_{s,in}(s) = \frac{I_{in}}{I_{PD}}$$

$$= \frac{sC_{PAD}Z_{in} + 1}{s^{3}C_{PD}C_{PAD}Z_{in}L_{BW} + s^{2}C_{PD}L_{BW} + s(C_{PD} + C_{PAD})Z_{in} + 1},$$

(2-13)

where  $Z_{in}$  is the effective input impedance of the main TIA. To analyze the peaking network using a generalized peaking factor  $m_1$ , Eq. (2-13) is rewritten as

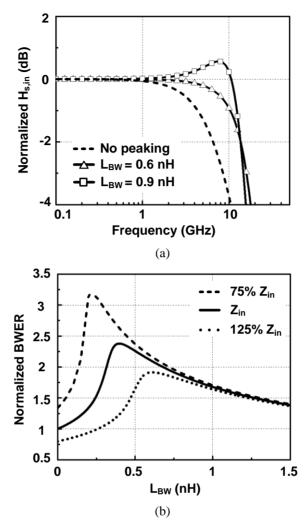

Fig. 2.10 (a) Simulated frequency response and (b) BWER of the input series peaking network.

$$H_{s,in}(s) = \frac{\frac{s}{\omega_o} k_1 + 1}{\left(\frac{s}{\omega_o}\right)^3 \frac{k_1}{m_1} (1 - k_1) + \left(\frac{s}{\omega_o}\right)^2 \frac{(1 - k_1)}{m_1} + \frac{s}{\omega_o} + 1},$$

(2-14)

where  $\omega_o = 1/Z_{in} C_{PD}$ ,  $k_1 = C_{PAD}/(C_{PAD} + C_{PD})$  and  $m_1 = Z_{in}^2 C_{PD}/L_{BW}$ . In our design,  $Z_{in}$  is about 60  $\Omega$  within the bandwidth of interest. Fig. 2.10 shows the simulated frequency response of  $H_{s,in}(s)$  for the target range of  $L_{BW}$ . The deviation of  $L_{BW}$  introduces small bandwidth variation and less than 1-dB amplitude overshoot. Realized by the input bond-wire inductance, the designed value of  $L_{BW}$  is targeted at 0.75 nH to facilitate practical implementation while avoiding the

bandwidth enhancement ratio (BWER) peaking region that is sensitive to  $L_{BW}$  as shown in Fig. 2.10(b). The BWER is relatively stable under variation of  $Z_{in}$  for  $L_{BW}$  around 0.75 nH. In this way, the required tolerance of  $L_{BW}$  is relaxed to +/-20% which is well within the control of standard wire bonding equipment. The target range of  $L_{BW}$  (0.6~0.9 nH) can be attained using typical wire bonding process. For the  $L_{BW}$  from 0.6 nH to 0.9 nH,  $m_1$  ranges from 1 to 1.5 in this design.

The second and third peaking are created by employing  $L_F$  and  $L_S$  at the input node of the main TIA to boost the open-loop bandwidth of the core inverter amplifier. As shown in Fig. 2.9(c), the shunt-shunt feedback can be equivalently modeled by an effective loading ( $Z_{FB} = R_F + sL_F$ ) at the input and output of the core inverter amplifier with an added ideal feedback current source ( $-V_{out}/Z_{FB}$ ). The  $Z_{FB}$  together with the series peaking inductor  $L_S$  form a shunt-series peaking network at the inverter input node. Based on the equivalent circuit, the inverter amplifier open-loop input impedance  $Z_{in,inv}$  is given by

$$Z_{in,inv}(s) = \frac{\frac{s}{\omega_0 m_2} + 1}{\left(\frac{s}{\omega_0}\right)^4 \frac{k_2}{m_2 m_3} (1 - k_2) + \left(\frac{s}{\omega_0}\right)^3 \frac{k_2}{m_3} (1 - k_2) + \left(\frac{s}{\omega_0}\right)^2 \left(\frac{1 - k_2}{m_3} + \frac{1}{m_2}\right) + \frac{s}{\omega_0} + 1}, \quad (2-15)$$

where  $m_2 = R_F^2(C_{PAD} + C_G)/L_F$ ,  $m_3 = R_F^2(C_{PAD} + C_G)/L_S$ ,  $k_2 = C_{PAD}/(C_{PAD} + C_G)$  and  $\omega_o = 1/R_F(C_{PAD} + C_G)$ . It follows that the inverter amplifier open-loop gain under a current-mode input can then be expressed as

$$A_{inv}(s) = Z_{in, inv}(s) \cdot G_m \cdot Z_{out, inv}(s), \tag{2-16}$$

where  $G_m = g_{m,n} + g_{m,p}$  is the total transconductance of the inverter amplifier and  $Z_{out,inv}(s) = R_o // 1/(sC_L) // Z_{FB}$  is the output impedance of the inverter amplifier. The proposed peaking scheme effectively expands the bandwidth of  $A_{inv}(s)$  through boosting  $Z_{in,inv}(s)$  and  $Z_{out,inv}(s)$  at high frequencies. By combining  $A_{inv}$  and  $Z_{FB}$ , the closed-loop main TIA transimpedance can now be expressed as

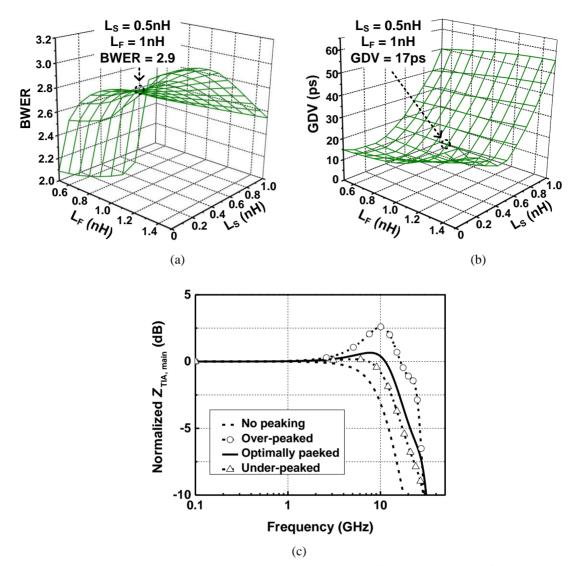

Fig. 2.11 (a) Simulated BWER, (b) group delay variation and (c) frequency response of the main TIA.

$$Z_{TIA, main}(s) = \frac{V_{out}}{I_{in}} = \frac{A_{inv}(s)}{1 + A_{inv}(s) \cdot Z_{FB}(s)}$$

(2-17)

With  $H_{s,in}(s)$  and  $Z_{TIA,main}(s)$  derived, the optimization of the three peaking factors for boosting the total TIA transimpedance gain  $Z_T(s)$ , listed as Eq. (2-12), can be carried out. The optimization of  $L_S$  and  $L_F$  is conducted with the consideration of both BWER and group delay variation (GDV) as shown in Fig. 2.11. The high-Q series peaking inductor  $L_S$  boosts bandwidth efficiently below 0.5 nH. Further increase of  $L_S$  results in excessive amplitude overshoot, reduced

**Table III Summary of Multiple Peaking Network**

|              | <b>m</b> 1 | m <sub>2</sub> | <b>m</b> 3 | Ripple (dB) | $Z_T$ BWER |  |

|--------------|------------|----------------|------------|-------------|------------|--|

| Over-peaked  | 0.5        | 1.3            | 2.5        | 3.6         | 2.7        |  |

| Opt. peaked  | 1          | 2.6            | 5          | 0.8         | 2.8        |  |

| Under-peaked | 1          | 5              | 7.5        | 0           | 1.7        |  |

Fig. 2.12 Post-layout simulation of (a) frequency response and (b) 25-Gb/s output eye diagram with 50- $\mu$ A<sub>pp</sub> input current and 250-fF  $C_{PD}$ .

BWER and significant GDV. On the other hand, the bandwidth boosting from  $L_F$  is moderate due to the large series resistor  $R_F$ . However, the presence of  $L_F$  is essential for achieving sufficient BWER with low GDV. Meanwhile,  $L_F$  compensates ripples in amplitude response to reduce the

deterministic jitter. The trade-off between occupied chip area, BWER and GDV eventually limits  $L_F$  to 1 nH. As summarized in Table II, the optimal peaking factor combination ( $m_1 = 1$ ,  $m_2 = 2.6$  and  $m_3 = 5$ ) yields a total BWER of 2.8 with ripple < 1 dB.

Post-layout simulations of  $Z_T(s)$  for the proposed TIA are plotted in Fig. 2.12. The TIA bandwidth is improved from 7.5 GHz to 21 GHz, indicating that an overall BWER of 2.8 is achieved by the proposed multiple peaking technique. The frequency response without  $C_{PD}$  is also plotted to facilitate the comparison to electrical measurement performed without the photodetector in place. The simulated TIA output eye diagram with 50  $\mu$ App input current at 25 Gb/s indicates low deterministic jitter and low IRN. The simulated average input-referred noise current density is 16 pA/ $\sqrt{Hz}$  within 25 GHz. The additional noise of bond-wire inductance  $L_{BW}$  is insignificant because of its low series resistance. The noise contribution due to the parasitic series resistance of  $L_F$  is negligible because it is absorbed as part of  $R_F$ . To keep the noise of  $L_S$  to a minimal level, its inductance is set to the minimum value for the target BWER.

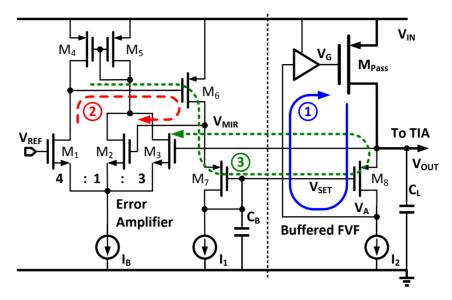

# 2.3.3 Fully-integrated LDO

Fig. 2.13 Schematic of the integrated LDO.

Fig. 2.13 shows the schematic of the fully-integrated LDO. The TIA core is designed to operate from a 1 V supply regulated by a point-of-load LDO to reject supply noise and mitigate parasitic supply bonding wire inductance. To provide the 2.5 mA for the TIA running at 25 Gb/s, the LDO should have ultra-fast response and also large output capacitor. Since the loading current of this LDO is small comparing to other general purpose (100 mA) LDOs, it is advantageous to place the LDO dominant pole at its output node for high PSR and fast transient response. Most of the limited available capacitance (silicon area) is allocated to its output node (dominant pole), while the internal poles are pushed to frequencies higher than the unity-gain frequency by using buffer impedance attenuation and flipped voltage follower (FVF) techniques [24]. A triple-input error amplifier is proposed to improve the DC accuracy. The  $V_{OUT}$  is regulated by the control loop at low frequency, and the noise is bypassed to ground by  $C_L$  at high frequency (> 1 GHz). In the FVF based structure,  $V_{OUT}$  is mainly determined by  $V_{SET}$ . Therefore, adding a bypass capacitor  $C_B$  at the  $V_{SET}$  node can improve the PSR in the medium frequency range (around 100 MHz to 1 GHz),

Fig. 2.14 Simulated LDO PSR.

by filtering out the ripple that comes from  $V_{MIR}$  to  $V_{OUT}$ . The total on-chip capacitance ( $C_B$  and  $C_L$ ) for the LDO is less than 140 pF.

Simulated LDO PSR is shown in Fig. 2.14. The LDO has a PSR better than –19 dB at low frequencies and the worst case occurs around 1.5 GHz with –12 dB rejection. Time domain verification of the supply noise rejection is performed by applying a 100-MHz 10-mV<sub>pp</sub> squarewave as the supply noise. Fig. 2.15 shows the simulated 25 Gb/s output eye diagram for TIAs with and without integrated LDO, respectively. The P-P jitter degradation of the TIA with integrated LDO is not noticeable. On the other hand, the one without on-chip LDO shows almost a 3 times P-P jitter deterioration. Above simulation results verify that the proposed fast-response integrated LDO can effectively reduce the supply noise induced P-P jitter in single-ended high-speed TIA frontend.

Fig. 2.15 Simulated 25 Gb/s TIA output eye diagram with 100-MHz 10-m $V_{pp}$  square-wave supply noise: (a) with LDO and (b) without LDO.

Another practical issue in implementing the single-ended TIA is the influence of the parasitic inductance from supply bond-wires. The parasitic bond-wire inductance manifests as the impedance degeneration to the inverter core amplifier at high frequencies, which significantly reduces high frequency transimpedance gain and creates large gain ripple. This issue is alleviated by integrating an on-chip LDO to isolate the Vdd bond-wire inductance and to provide an extra low-impedance ground path through the large area substrate contact in the LDO's loading MOS capacitor.

### 2.4 Experimental Results

Fig. 2.16 (a) TIA Chip micrograph and (b) measurement setup.

Fig. 2.17 Measured TIA frequency response by direct on-chip probing.

The receiver front-end has been designed and fabricated in a 65-nm CMOS technology. The die photo of the integrated TIA with LDO is shown in Fig. 2.16(a). The core circuit occupies 0.08 mm<sup>2</sup>. Fig. 2.16(b) shows the measurement setup for electrical frequency domain measurement and optical time domain measurement. The frequency response is obtained by measuring the TIA's s-parameter via on-die probing. The optical input signal is generated by an 850-nm Mach-Zehnder Modulator fed with a 25-Gb/s PRBS generator. The PD used in the optical measurement has a

(a)

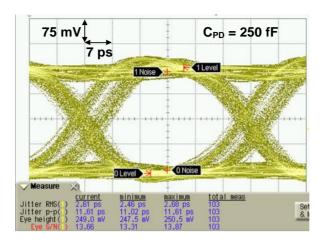

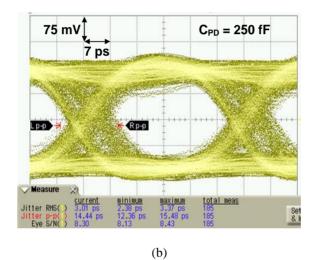

Fig. 2.18 Measured optical eye diagram at 25 Gb/s with (a) LDO enabled (RMS Jitter = 2.6 ps, P-P Jitter = 11.6 ps) and (b) LDO disabled (RMS Jitter = 3 ps, P-P Jitter = 14.4 ps).

responsivity of 0.4 W/A and 28-GHz bandwidth. The TIA's electrical output eye diagram is captured by a high-speed sampling scope. An error detector is used for the BER test.

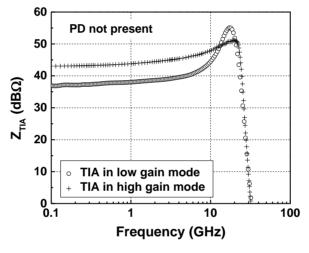

Fig. 2.17 shows the frequency response of the TIA in both high and low gain mode. The frequency response is converted from the measured S-parameters based on [25]

$$Z_{TIA} = \frac{s_{21}}{(1 - s_{11})(1 - s_{22})} \cdot Z_o, \tag{2-18}$$

where  $Z_o = 50~\Omega$  is the characteristic impedance of the equipment. A single-ended transimpedance gain of 42 dB $\Omega$  with 24-GHz bandwidth is achieved. A 4-dB $\Omega$  tuning range controlled by 4 digital

bits is designed to compensate the process and PD loading variation. The gain peaking at 20 GHz is an artifact due to the absence of the PD capacitive loading during s-parameter measurement by direct on-chip probing.

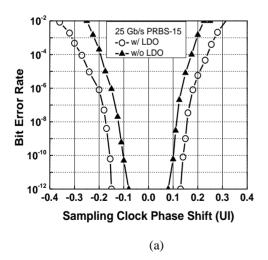

Fig. 2.18 shows the measured TIA output eye diagram with the LDO enabled and disabled respectively. The RMS and P-P jitter are improved by 0.4 ps (15%) and 2.8 ps (24%) respectively when the LDO is enabled. The reduced jitter improves the horizontal eye opening by 12% at a BER less than  $10^{-12}$  as observed in the BER bathtub curves shown in Fig. 2.19. The relatively narrow error free open range is limited by the insufficient sensitivity of the BER tester.

Table IV summarizes the performance of the proposed TIA and compares to recently published results. To facilitate the performance comparison, a FOM defined by

$$FOM = \frac{Gain \cdot Bandwidth}{Power \cdot Sensitivity}$$

(2-19)

is introduced. This work achieves the highest FoM by achieving state-of-the-art GBW and sensitivity with greatly reduced power dissipation.

Fig. 2.19 (a) BER bathtub curve with and without LDO enabled and (b) optical input sensitivity curve.

**Table IV TIA Performance Comparison and Summary**

|                      | TIA in [14]<br>JSSC '14 | TIA in [13]<br>ISSCC '13 | TIA in [26]<br>JSSC '13 | This work  |  |

|----------------------|-------------------------|--------------------------|-------------------------|------------|--|

| Topology             | LBW TIA<br>+EQ          | CML FB                   | XFM RGC                 | Inv. FB    |  |

| Bandwidth<br>(GHz)   | 20.5+                   | 21                       | 26                      | 24         |  |

| Data Rate<br>(Gb/s)  | 25                      | 25                       | 27^                     | 25         |  |

| C <sub>PD</sub> (fF) | 80                      | 150                      | 150                     | 250        |  |

| Gain (dBΩ)           | 57.2+                   | 41                       | 53                      | 42         |  |

| Sensitivity (µA)     | 59                      | 98                       | 93^                     | 74         |  |

| Supply (V)           | 1                       | 1                        | 1.9                     | 1.2/1      |  |

| Power (mW)           | N/A                     | 4.8                      | 28.2                    | 3          |  |

| Technology           | 65-nm CMOS              | 65-nm CMOS               | 0.25-μm<br>BiCMOS       | 65-nm CMOS |  |

| FOM                  | N/A                     | 5.0                      | 4.4                     | 13.6       |  |

<sup>&</sup>lt;sup>+</sup> Simulation result.

<sup>^</sup> Electrical measurement.

# **Chapter 3 Fully Integrated Optical-to-Millimeter-Wave Modulator**

### 3.1 Introduction

# Optical Base RF Mod PA mmW Output Proposed solution: Optical Base RF Mod PA mmW Output Optical RF Optical RF

Fig. 3.1 Comparison between a conventional and the proposed fiber-wireless system

Output

Mod

Rx

This chapter presents an optical-to-mmW modulator SoC with an integrated 850-nm wavelength optical receiver front-end for short-range backhaul connectivity in emerging fiber-wireless mobile networks. As discussed in Chapter 1, the BoF system alleviates the performance requirement on optical links since only the baseband signal is transmitted in optical domain. However, energy efficient and cost effective O/E conversion and RF transmission systems at remote cells are necessary for the BoF scheme to outperform the RoF scheme. Therefore, an integrated module capable of directly converting signals between the optical and the mmW domain is needed to reduce the overhead in system size and cost for supporting fiber-wireless backhaul links. As shown in Fig. 3.1, a conventional fiber-wireless system usually consists of discrete components and several chips to perform O/E conversion, baseband processing and RF transmission. In contrast, the proposed system integrates the photodetector on-chip and combines the optical and RF blocks to eliminate redundant baseband de-multiplexing and multiplexing, resulting in a more efficient and compact fiber-wireless system.

Compared to traditional implemented in III-V technology, CMOS monolithic optoelectronic integrated circuits (OEICs) is a promising technology to achieve low-cost, small system form factor and high volume manufacturing capacity in optical communication systems. However, the performance of OEICs is usually limited by the inferior CMOS optical components. Several techniques have been demonstrated to improve performance of CMOS on-chip PDs. A spatially-modulated PD [12] is presented to improve PD bandwidth by canceling the slow diffusion current at the price of lower responsivity. [25] presents CMOS PDs fabricated with process modification to achieve low parasitics and high bandwidth. However, extra process steps result in high cost and specific foundry limitation. To further push the performance, the CMOS on-chip PD can be biased at avalanche mode to realize over twofold improvement in responsivity and bandwidth. Nevertheless, the high bias voltage increases system design complexity and reliability risk.

The unlicensed 60-GHz band has been demonstrated to accomplish mmW backhaul links for