# Wireless Power Acquisition and Regulation: Power Management Integrated Circuits for Biomedical Implantable Devices

by

Yan Lu

A Thesis Submitted to

The Hong Kong University of Science and Technology

in Partial Fulfillment of the Requirements for

the Degree of Doctor of Philosophy

in the Department of Electronic and Computer Engineering

December 2013, Hong Kong

#### Authorization

I hereby declare that I am the sole author of the thesis.

I authorize the Hong Kong University of Science and Technology to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize the Hong Kong University of Science and Technology to reproduce the thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Yan Lu

December 2013

# Wireless Power Acquisition and Regulation: Power Management Integrated Circuits for Biomedical Implantable Devices

by

#### Yan Lu

This is to certify that I have examined the above PhD thesis and have found that it is complete and satisfactory in all respects, and that any and all revisions required by the thesis examination committee have been made.

Prof. Wing-Hung KI, ECE Department (Thesis Supervisor)

Prof. C. Patrick YUE, ECE Department (Thesis Co-Supervisor)

Prof. Pingbo HUANG, Division of Life Science, (Chairman)

Prof. Philip K.T/MOK, ECE Department (Committee Member)

Prof. Chi-Ying TSUI, ECE Department (Committee Member)

Za

Prof. Brian Kan Wing MAK, CSE Department (Committee Member)

Prof. Danny H. K. TSANG, Acting Head of Department

Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology December 2013 To my parents

#### ACKNOWLEDGEMENTS

First of all, I would like to express my tremendous and sincere thanks to my supervisor, my mentor, Professor Ki. I benefit really a lot from his free supervisory style. He always encourages me to think big, and do the research that I am much interested in. During my four years of PhD study under his guidance, I developed quite a lot in many aspects including but not limited to technical skills, research methodology and my personality. And he is always generous and supportive to me (and his other students) for conference, internship, exchange and many other opportunities. He is sometimes like a friend, and sometimes like a father to me. Without him, it won't be possible for me to achieve what I have done today.

I am also very grateful to Professor Patrick Yue as well. He had led me into another interesting (high frequency) research area, and had provided me the opportunities of using the advance processes. He also introduced me to the exciting industrial world by sharing his previous start-up experiences and taking me to the company trips. He and Prof. Ki are like my complementary supervisors who had significantly improved my efficiencies.

I would also like to thank Professor C. Y. Tsui for including me in his neuron stimulation project, which is also a very interesting and promising research topic. I enjoyed the trips to the University of Hong Kong for the lab rat experiments, which are conducted together with Prof. Ki, Prof. Tsui and my partner Xing Li.

I am sincerely grateful to Professor Pingbo Huang, Professor Philip K. T. Mok, Prof. C. Y. Tsui, Prof. Brian K. W. Mak and Prof. Danny H. K. TSANG for serving as my thesis examination committee, and Professor Seng Pan U for serving as my thesis external examiner, spending their invaluable time to read my thesis in details, and giving insightful comments for me to improve my thesis.

I'd like to give special thanks to Prof. Bram Nauta and Prof. Anne-Johan Annema for their guidance during my visit in their group at University of Twente.

I would like to thank my labmates and fellow students, for the technical and non-technical discussions, on- and off-campus activities, who had made the life of my PhD study delightful

and memorable. They are Dr. Jun Yi, Dr. Patrick Wu, Dr. Chenchang Zhan, Dr. Xiaocheng Jing, Dr. Vincent Chan, Dr. Edward Ho, Cheng Huang, Patrick Kwan, Oliver Lee, Erick Lai, Yonggen Liu, Xiaohao Hu, YK Teh, Lin Cheng, Fan Yang, Min Tan, Xing Li, Xun Liu, Lisong Li, Yuan Gao, Jungmoon Kim, Jiawei Zheng and Junmin Jiang of the Integrated Power Electronics Laboratory (IPEL); and Prof. Liang Wu, Prof. Rongxiang Wu, Dr. Li Sun, Alex Quan Pan, Robin Zhengxiong Hou, Yipeng Wang, Salahuddin Raju, and George Fengyu Che of the High-Speed Silicon Lab (HS2L); Dr. Bing Liu, Dr. Ruoyu Xu and Jing Guo of the MIXIC Lab; Haifeng Ma, Dawei Ye, Dr. Milad Darvishi, Saifullah Amir, Erik Olieman, Johan Withagen and Claudia Palattella of the ICD Group of UT. Special thanks go to Xiaocheng for everything. Special thanks go to Cheng Huang for teaching me photography, playing badminton with me, encouraging me on research. I am also grateful to Vincent Chan for leading me into the Marathon run.

I would also like to thank all the senior PhDs of IPEL, who had significantly contributed to IPEL and had setup an excellent standard for the younger students like me. They are Prof. Dongsheng Ma, Prof. Alex Leung, Prof. Hoi Lee, Dr. Hylas Lam, Dr. Scottie Man, Dr. Feng Su, Dr. Patrick Wu, Dr. Jun Yi, Dr. Chenchang Zhan, Dr. Edward Ho, Dr. Henry Kwong, Dr. Xiaocheng Jing, and Dr. Vincent Chan.

I'd like to thank my badminton friends at HKUST for the fun we had. They are Yuxuan Zhang, Dr. Yue Jia, Yuanyuan Wang, Dr. Jing Tang, and Dr. Ping Chen. The wins and losses of the matches released me from stress and tension in the university.

Last but not least, I would like to thank my parents for their endless love and unconditional supports.

# TABLE OF CONTENTS

| Authorization Page                                          | ii  |

|-------------------------------------------------------------|-----|

| Signature Page                                              | iii |

| Acknowledgements                                            | v   |

| Table of Contents                                           | vii |

| List of Figures                                             | x   |

| List of Tables                                              | xiv |

| Abstract                                                    | XV  |

| Chapter 1 Introduction                                      | 1   |

| 1.1 Research Background                                     | 1   |

| 1.2 System Requirements                                     | 3   |

| 1.3 Operation Frequency                                     | 4   |

| 1.4 Conclusion                                              | 6   |

| Chapter 2 Rectifier: From Passive to Active                 | 7   |

| 2.1 Passive Rectifier                                       | 7   |

| 2.2 Active Rectification for IMDs                           | 8   |

| 2.2.1 Operation Principle and Problems of Active Rectifiers | 9   |

| 2.2.2 Comparison of Comparator Delay Compensation Schemes   | 11  |

| 2.2.3 Delay Time of Active Diodes                           | 15  |

| 2.3 Conclusion                                              | 17  |

| Chapter 3 Active Rectifier Implementations                  | 18  |

| 3.1 Comparator with Switched-Offset                         | 18  |

| 3.2 Current Source Design                                   | 20  |

| 3.3 Power Transistor Sizing Optimization                    | 24  |

| 3.4 Minimum Operating Voltage                               | 25  |

| 3.5 Simulation and Measurement Results                      | 26  |

| 3.6 Conclusions                                             | 34  |

| Chapter 4 Reconfigurable Active Rectifier                   | 35  |

| 4.1 Voltage Doubler                                         | 37  |

| 4.2    | Bia | s Current                                                    | 38 |

|--------|-----|--------------------------------------------------------------|----|

| 4.3    | NN  | MOS and PMOS Active Diodes                                   | 39 |

| 4.4    | Sta | rt-Up of Reconfigurable Rectifier                            | 42 |

| 4.5    | Me  | easurement and Comparison                                    | 43 |

| 4.6    | Co  | nclusion                                                     | 47 |

| Chapte | r 5 | Switched-Capacitor Power Converter for IMDs                  | 48 |

| 5.1    | Inp | out Adaptive Dual-Output Charge Pump with Fractional-M       | 48 |

| 5.2    | Ciı | cuit Implementation                                          | 53 |

| 5.3    | Sir | nulation Results                                             | 56 |

| 5.4    | Co  | nclusion                                                     | 58 |

| Chapte | r 6 | Fully-Integrated LDO with DC-to-20GHz Power-Supply-Rejection | 59 |

| 6.1    | Fu  | ly Integration of LDO                                        | 59 |

| 6.2    | Do  | minant Pole Considerations                                   | 62 |

| 6.3    | Ciı | cuit Topologies                                              | 64 |

| 6.3    | 3.1 | Flipped Voltage Follower                                     | 64 |

| 6.3    | 3.2 | Buffer Impedance Attenuation                                 | 65 |

| 6.4    | Ciı | cuit Implementation and Analysis                             | 66 |

| 6.4    | 4.1 | Tri-Loop Architecture                                        | 66 |

| 6.4    | 4.2 | Stability Analyses                                           | 70 |

| 6.4    | 4.3 | Load Regulation                                              | 75 |

| 6.4    | 4.4 | Power Supply Rejection                                       | 75 |

| 6.5    | Me  | easurement Results                                           | 77 |

| 6.6    | Co  | nclusions                                                    | 82 |

| Chapte | r 7 | Voltage Reference and Regulators for IMDs                    | 83 |

| 7.1    | Sy  | mmetrically Matched Bandgap Reference                        | 83 |

| 7.2    | Vo  | ltage Regulators                                             | 84 |

| 7.3    | Sir | nulation and Measurement Results                             | 86 |

| 7.4    | Co  | nclusion                                                     | 88 |

| Chapte | r 8 | An NMOS-LDO Regulated Switched-Capacitor Power Converter     | 89 |

| 8.1    | DC  | C-DC Converter and LDO in Cascade                            | 89 |

| 8.2    | Co  | ntrol Loop for Fast Response                                 | 92 |

| 8.3    | Hn  | it Cell of the OP                                            | 93 |

| 8.4     | Measurement Results            | 95  |

|---------|--------------------------------|-----|

| 8.5     | Conclusions                    | 98  |

| Chapter | 9 Conclusions and Future Works | 100 |

| 9.1     | Thesis Conclusions             | 100 |

| 9.2     | Future Works                   | 102 |

| Referen | ces                            | 103 |

| Biograp | hy and Publications            | 110 |

# **List of Figures**

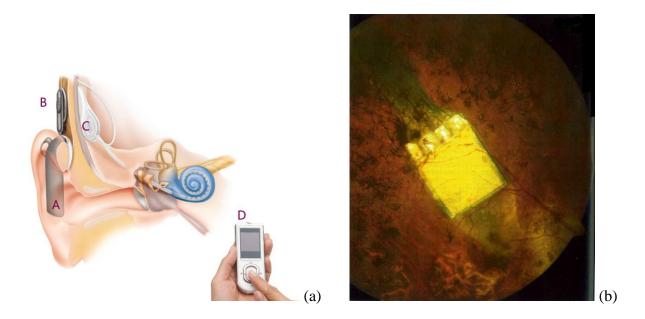

| Fig. 1.1 (a) Cochlear implant [2] and (b) retinal prostheses [4].                                         | 1         |

|-----------------------------------------------------------------------------------------------------------|-----------|

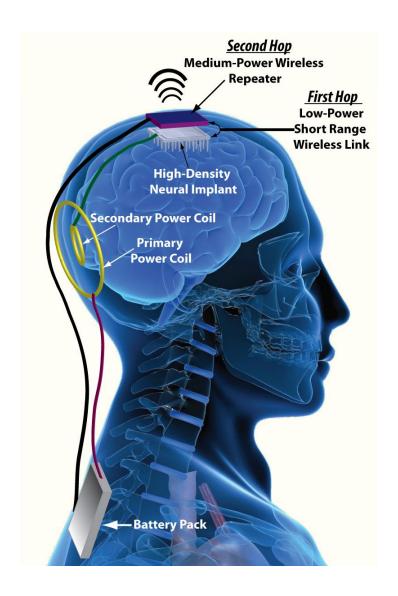

| Fig. 1.2 Diagrammatic sketch of the BMI.                                                                  | 2         |

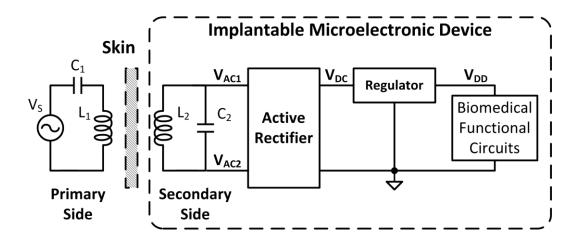

| Fig. 1.3 A generic transcutaneous inductive power link for implantable devices                            | 2         |

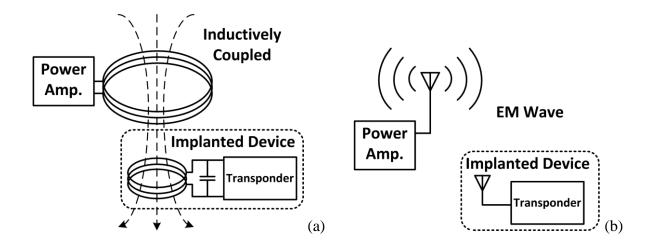

| Fig. 1.4 Wireless power transfer systems with (a) near-field or (b) far-field of                          | peration, |

| respectively                                                                                              | 5         |

| Fig. 1.5 Tradeoffs in selecting the operation frequency.                                                  | 6         |

| Fig. 2.1 (a) Half-wave rectifier, and (b) full-wave rectifier                                             | 7         |

| Fig. 2.2 (a) The passive full-wave rectifier, and (b) the active full-wave rectifier                      | 8         |

| Fig. 2.3 (a) The active full-wave rectifier, and (b) its simulated waveforms of reverse                   | current   |

| problem in active rectifier.                                                                              | 10        |

| Fig. 2.4 (a) Symbol of artificial switched-offset; (b) hysteretic comparator; and (c) cor                 | nparator  |

| schemes for reverse current control.                                                                      | 11        |

| Fig. 2.5 Conceptual waveforms of the input/output voltages, power NMOS gate voltages                      | tage and  |

| conducted currents for active rectifiers with different comparators                                       | 13        |

| Fig. 2.6 Simulated waveforms of multiple-pulsing problem associated with dynamic                          | ic offset |

| schemes.                                                                                                  | 14        |

| Fig. 2.7 Simplified schematic of active diode 1 with emphasis on supply voltage, input                    | ut signal |

| and load capacitor for delay calculations.                                                                | 16        |

| Fig. 2.8 Simulated active diode delay $t_{\rm d,AD}$ , comparator delay $t_{\rm d,C}$ and gate drive buff | er delay  |

|                                                                                                           | 16        |

| Fig. 3.1 The proposed delay time compensated comparator with switched-offset                              | scheme    |

| (Active Diode 1(2) in Fig. 2.3)                                                                           | 18        |

| Fig. 3.2 Bias circuits without start-up requirement.                                                      | 21        |

| Fig. 3.3 Schematic of (a) peaking current source for Rec1 and (b) the proposed QIPV                       | ' biasing |

| circuit for Rec2.                                                                                         | 21        |

| Fig. 3.4 Simulated and measured output current versus supply voltage of (a) peaking                       | g current |

| source for Rec1 and (b) the proposed QIPV biasing circuit for Rec2                                        | 22        |

| Fig. 3.5 Simulated start-up process of the proposed active rectifier (Rec2).                              | 25        |

| Fig. 3.6 Micrographs of Rec1 and Rec2.                                                                    | 26        |

| Fig. 3.7 Measurement setup for the proposed 13.56 MHz active rectifiers                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 3.8 Measured waveforms of AC inputs and DC output at $R_L = 500\Omega$ and $V_{AC} = 3$ V of (a)                                   |

| Rec1 and (b) Rec2; at $R_L$ = 500 $\Omega$ and $V_{AC}$ = 1.5 V of (c) Rec1 and (d) Rec2                                                |

| Fig. 3.9 Measured voltage conversion ratios of Rec1 and Rec2 with different loadings 29                                                 |

| Fig. 3.10 The PCB schematics for PCE measurements with (a) differential voltage probes or                                               |

| (b) single-end probes. 30                                                                                                               |

| Fig. 3.11 Measured waveforms of $V_{AC}$ , $I_{AC}$ and $V_{DC}$ for PCE calculation                                                    |

| Fig. 3.12 Measured and simulated PCEs of the proposed $Rec2$ operating at 13.56 MHz with (a)                                            |

| $R_{\rm L} = 500~\Omega$ and (b) $ V_{\rm AC}  = 3~{\rm V}$ ; and its frequency response with condition of $R_{\rm L} = 500~\Omega$ and |

| $ V_{AC}  = 3 \text{ V}.$ 32                                                                                                            |

| Fig. 4.1 Block diagram of an inductively powered biomedical implantable system-on-a-chip                                                |

| alongside the proposed fully integrated $1X/2X$ active rectifier with QIPV bias current 36                                              |

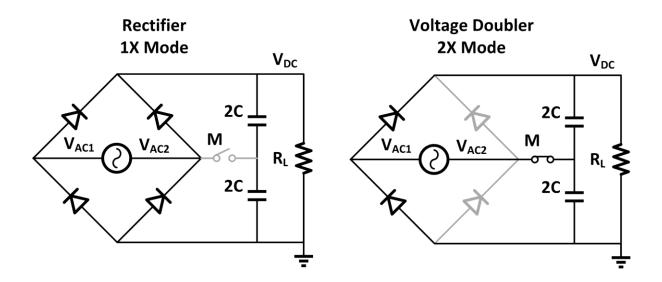

| Fig. 4.2 Schematic of the passive reconfigurable rectifier (universal rectifier) with 1X                                                |

| (rectifier) mode and 2X (voltage doubler) mode                                                                                          |

| Fig. 4.3 The conventional and the proposed arrangement of $C_{\rm L}$ , assuming that the total                                         |

| capacitance available is 4C for implementing $C_L$ . 37                                                                                 |

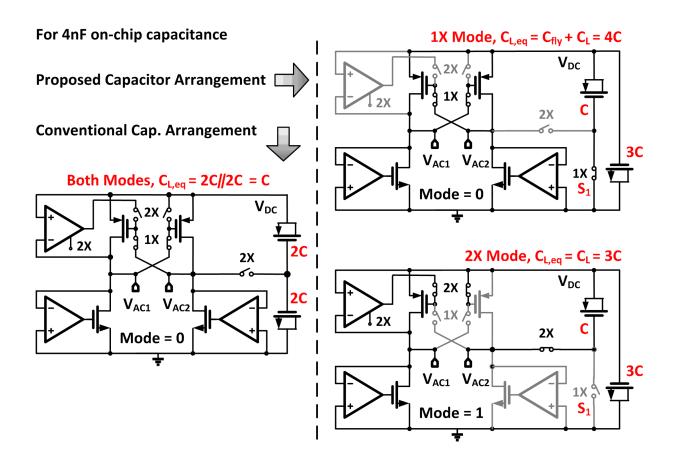

| Fig. 4.4 QIPV biasing with aspect ratios $M_{N1}:M_{N2}:M_{N3}=2:8:1.$ 39                                                               |

| Fig. 4.5 Schematics of the CMP1 (CMP2) with $M_{\rm N1}$ ( $M_{\rm N2}$ ), and the CMP3 with $M_{\rm P1}$ 40                            |

| Fig. 4.6 Simulated waveforms of the reconfigurable rectifier in 1X mode with $R_{\rm L}$ = 500 $\Omega$ ,                               |

| and $ V_{AC}  = 1.5$ and 3 V, respectively                                                                                              |

| Fig. 4.7 Simulated waveforms of the reconfigurable rectifier in 2X mode with $R_{\rm L}$ = 500 $\Omega$ ,                               |

| and $ V_{AC}  = 1.25$ and 1.8 V, respectively. 42                                                                                       |

| Fig. 4.8 Simulated start-up waveforms of the reconfigurable rectifier with mode selection pin                                           |

| "M" controlled by a hysteretic comparator. 43                                                                                           |

| Fig. 4.9 Chip micrograph and measurement setup of Rec3                                                                                  |

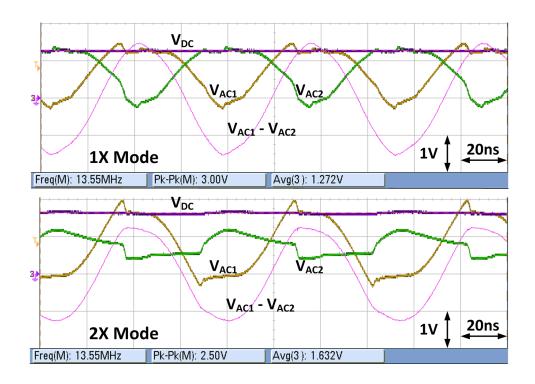

| Fig. 4.10 Measured AC input and DC output voltage waveforms in both modes with $R_{\rm L} = 500$                                        |

| $\Omega$ and $C_L = 4$ nF (on-chip) at their lowest $ V_{AC} $ points                                                                   |

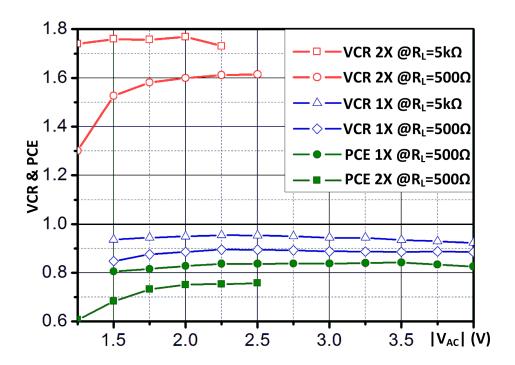

| Fig. 4.11 Measured voltage conversion ratios and power conversion efficiencies of the $1\mathrm{X}/2\mathrm{X}$                         |

| rectifier in both modes                                                                                                                 |

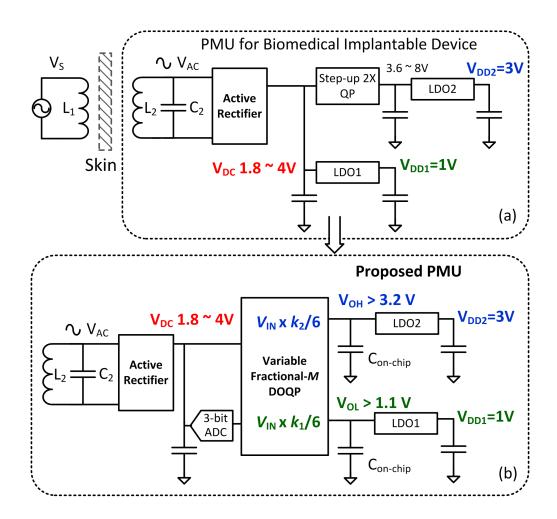

| Fig. 5.1 A PMU for biomedical implantable devices: (a) conventional implementation; and (b)                                             |

| proposed implementation                                                                                                                 |

| Fig. 5.2 Conventional methods of generating fractional-M step-down or step-up charge pump.                                              |

| 50                                                                                                                                      |

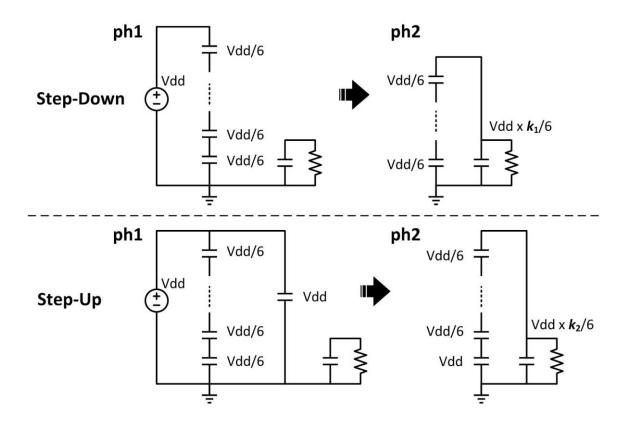

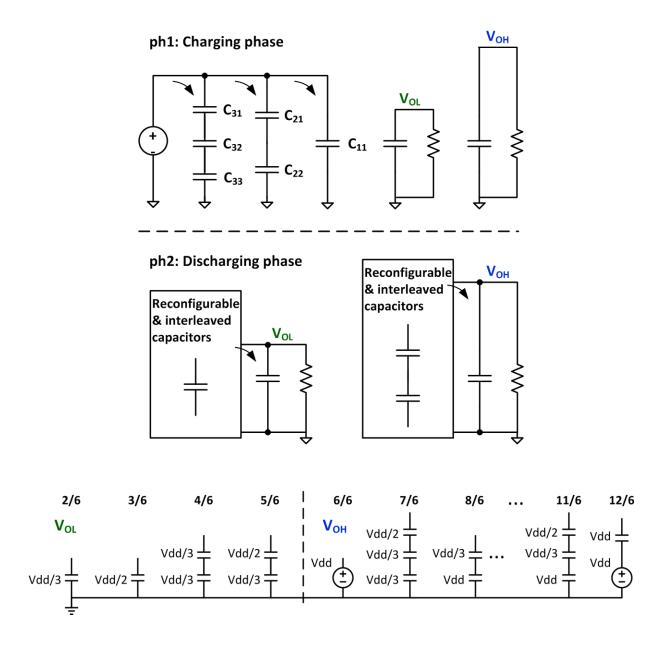

| Fig. 5.3 Charging and discharging phases of proposed conversion scheme                                                |

|-----------------------------------------------------------------------------------------------------------------------|

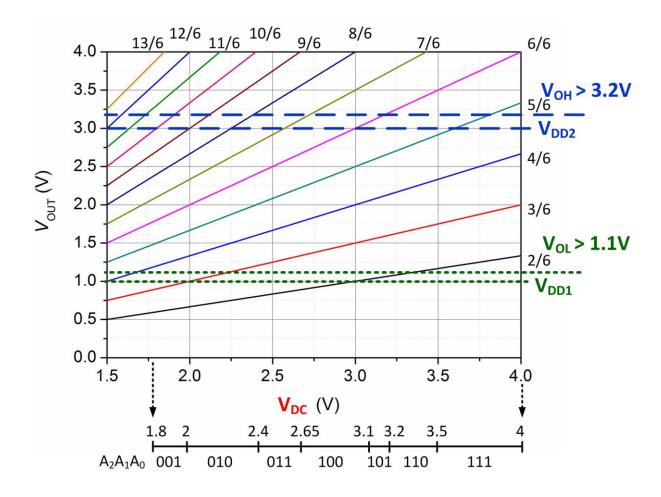

| Fig. 5.4 Possible conversion ratio combinations of the proposed DOQP scheme, and the 7                                |

| segments of $V_{\rm DC}$ defined for ADC                                                                              |

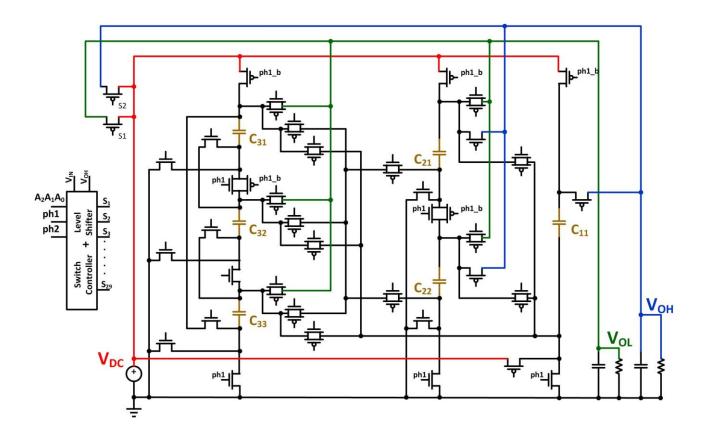

| Fig. 5.5 Top level schematic of the variable fractional- <i>M</i> DOQP                                                |

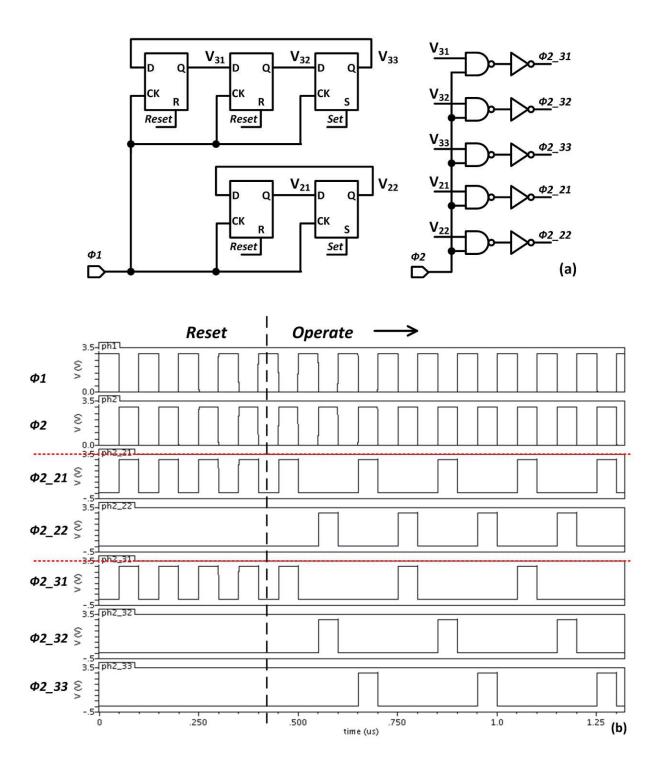

| Fig. 5.6 Phase generation circuit for the interleaving scheme (a), and its output waveforms (b).                      |

| 55                                                                                                                    |

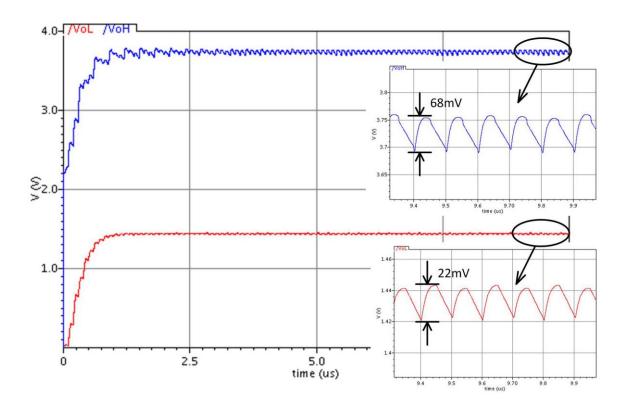

| Fig. 5.7 Output waveforms of the DOQP when $V_{\rm DC}$ is 3 V, $I_{\rm OH} = 500~\mu A$ and $I_{\rm OL} = 200~\mu A$ |

| respectively                                                                                                          |

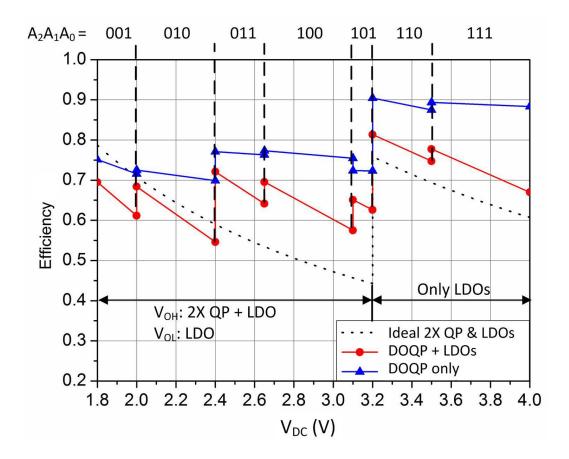

| Fig. 5.8 Efficiencies of the proposed PMU and the ideal conventional PMU57                                            |

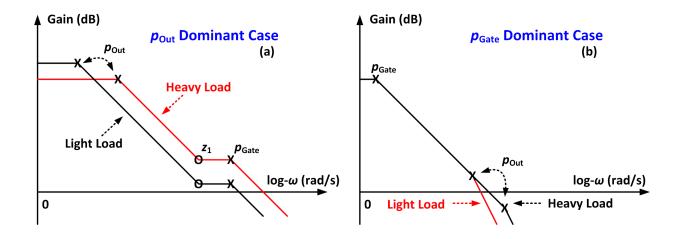

| Fig. 6.1 Magnitude plot of a generic LDO with two low frequency poles: (a) with $p_{\text{Out}}$ being                |

| its dominant pole; and (b) with $p_{\text{Gate}}$ being its dominant pole                                             |

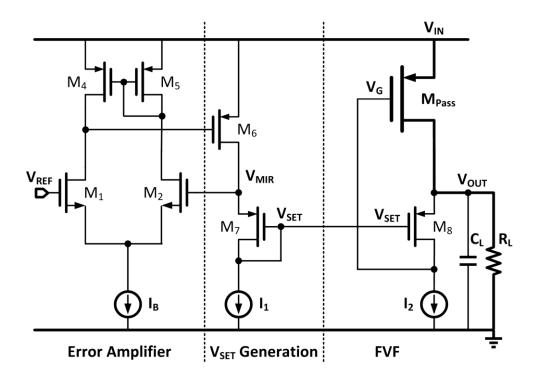

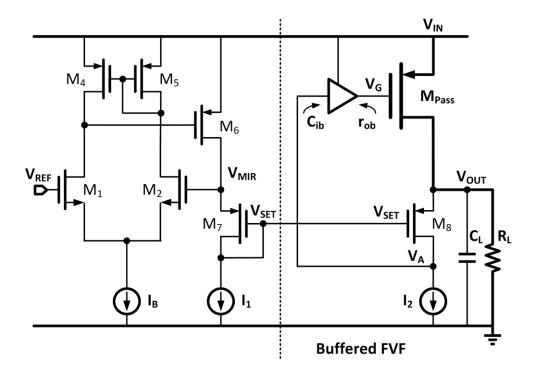

| Fig. 6.2 The single-transistor-control LDO regulator based on the FVF topology                                        |

| Fig. 6.3 The FVF based LDO regulator with inserted buffer                                                             |

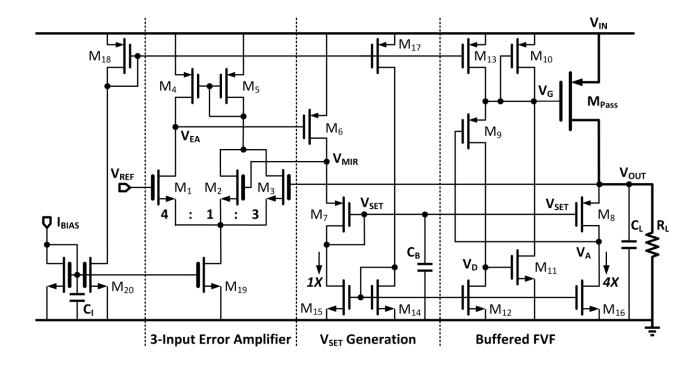

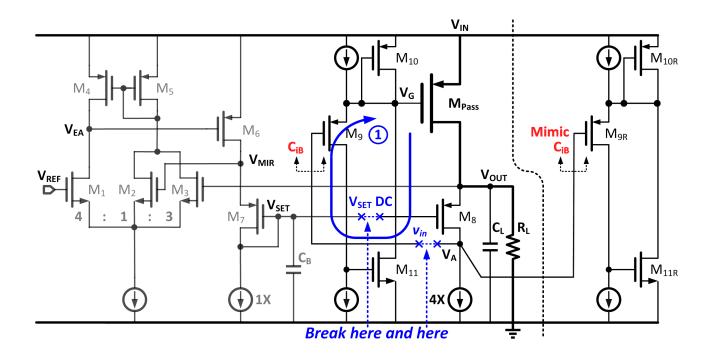

| Fig. 6.4 Transistor level schematic of the proposed fully integrated tri-loop LDO                                     |

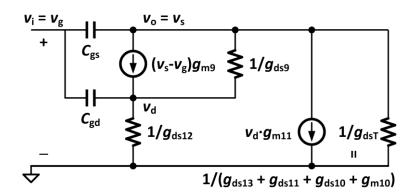

| Fig. 6.5 Small-signal model of the buffer for input/output impedance and gain calculation 68                          |

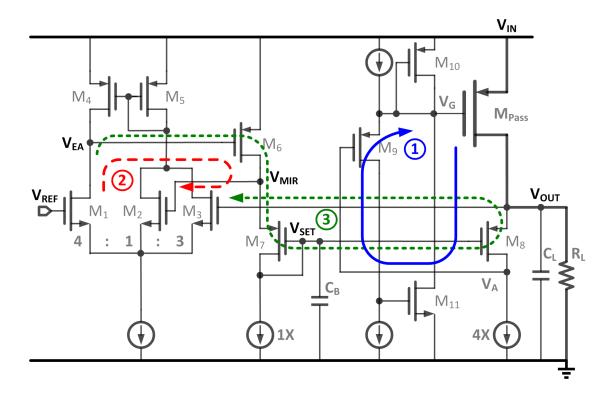

| Fig. 6.6 The simplified diagram of the three loops in the proposed LDO regulator70                                    |

| Fig. 6.7 Break the loop-1 with replica buffer to mimic its input capacitance71                                        |

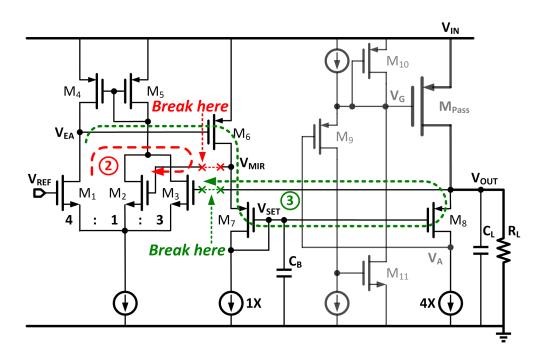

| Fig. 6.8 Break the loop-2 and -3 simultaneously for stability analysis71                                              |

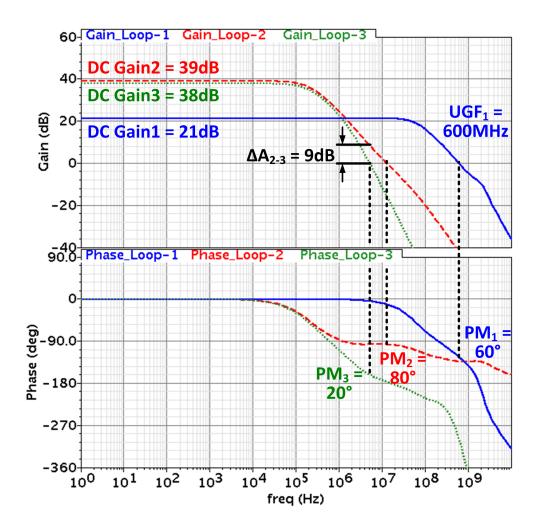

| Fig. 6.9 Simulated frequency response of the three loops of the proposed LDO regulator with                           |

| $V_{\rm IN} = 1.2 \text{ V}, V_{\rm OUT} = 1.0 \text{ V} \text{ and } R_{\rm L} = 100 \Omega.$                        |

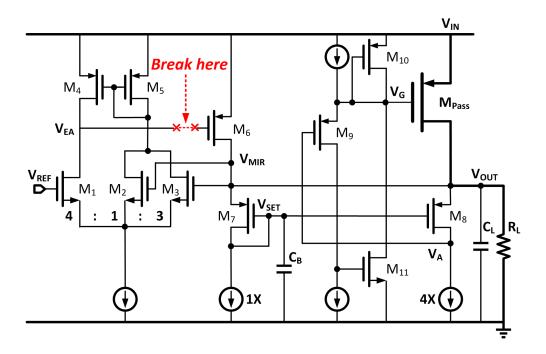

| Fig. 6.10 Break the loop at the EA output                                                                             |

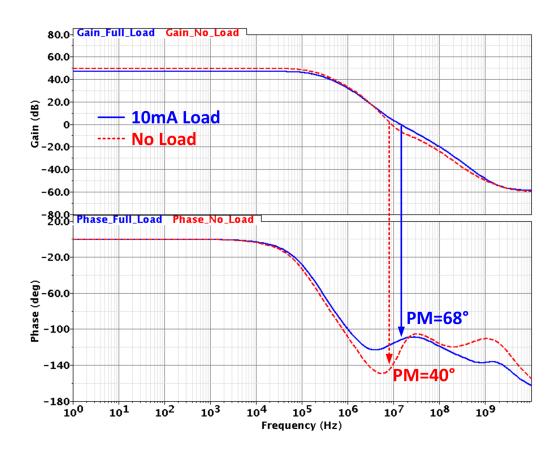

| Fig. 6.11 Simulated bode plot of the LDO with $V_{\rm IN}=1.2$ V, $V_{\rm OUT}=1.0$ V and $R_{\rm L}=100$ $\Omega$ 74 |

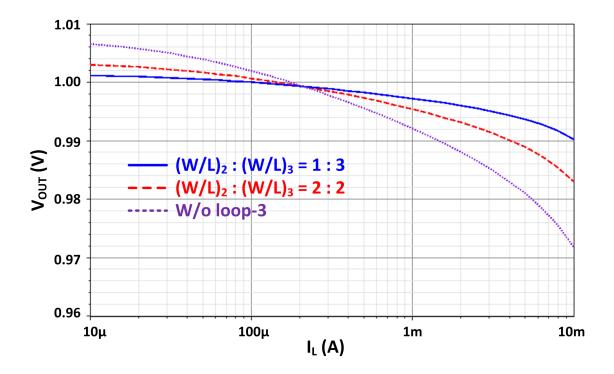

| Fig. 6.12 Simulated $V_{\text{OUT}}$ load regulation with $(W/L)_2$ : $(W/L)_3$ being set to 1:3 and 2:2,             |

| respectively; plus the case without loop-3                                                                            |

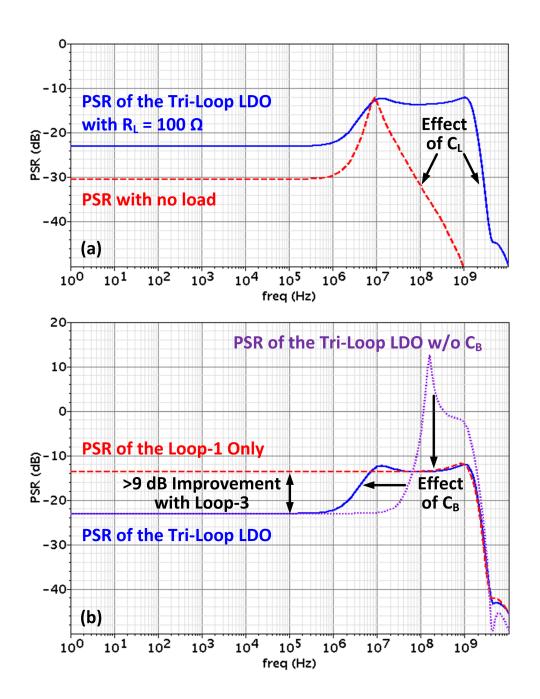

| Fig. 6.13 (a) Simulated PSR of the proposed LDO with or without $R_L = 100 \Omega$ , respectively;                    |

| and (b) PSR of loop-1 only and the tri-loop regulator with or without $C_{\rm B}$ , with $V_{\rm IN}=1.2~{ m V}$ ,    |

| $V_{\rm OUT} = 1.0 \; { m V} \; { m and} \; R_{\rm L} = 100 \; { m \Omega}.$                                          |

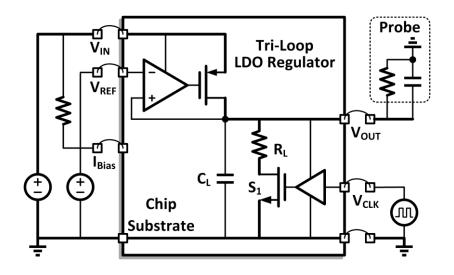

| Fig. 6.14 Testing setup of the regulator with on-chip load for measurement                                            |

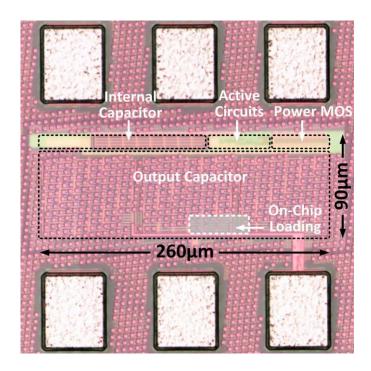

| Fig. 6.15 Micrograph of the proposed LDO with on-chip loading for characterization78                                  |

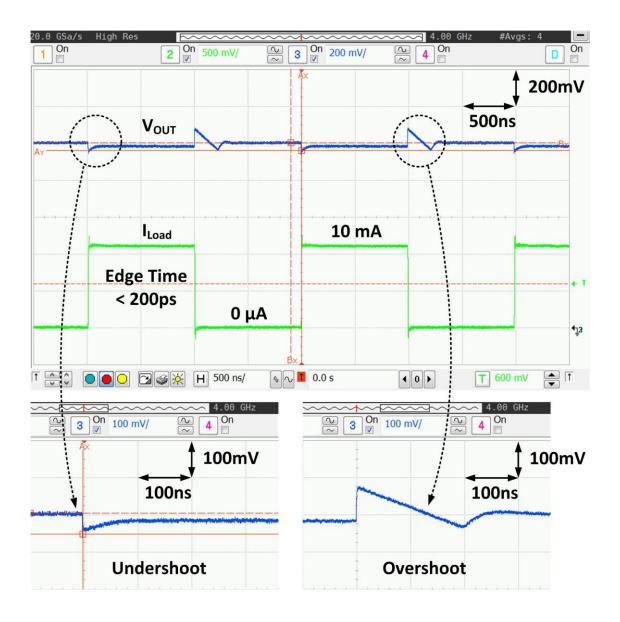

| Fig. 6.16 Measured transient response with $V_{\rm IN}=1.2$ V, $V_{\rm OUT}=1.0$ V, and on-chip load                  |

| current change from 0 μA to 10 mA within edge times of 200 ps                                                         |

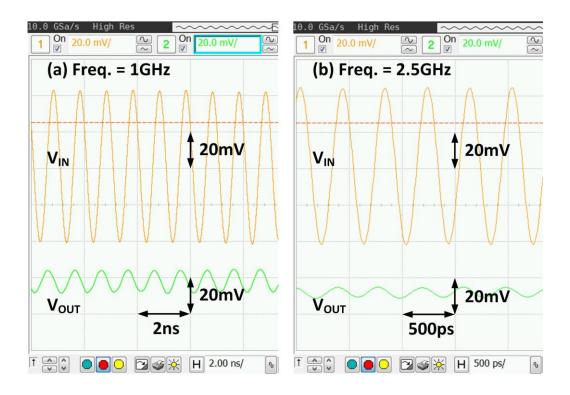

| Fig. 6.17 Measured transient waveforms for PSR calculation, with $V_{\rm IN} = 1.2$ V and 80 mV $V_{\rm PF}$          |

| input ripple at (a) 1 GHz and (b) 2.5 GHz, respectively                                                               |

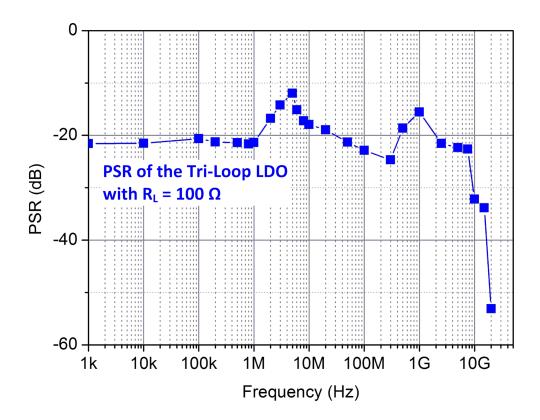

| Fig. 6.18 Measured PSR up to 20 GHz with $R_L = 100 \Omega$ .                                                       | 81      |

|---------------------------------------------------------------------------------------------------------------------|---------|

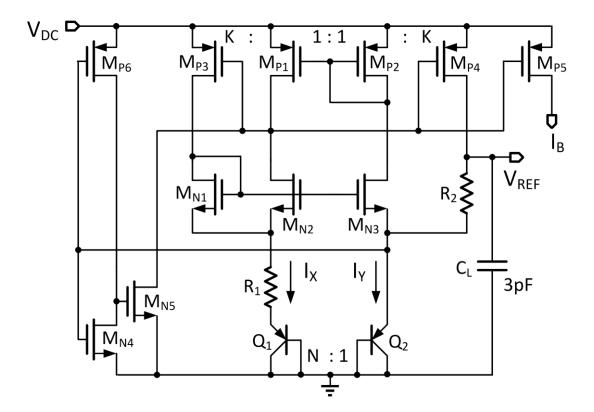

| Fig. 7.1 The two-branch self-biased symmetrically matched bandgap reference used i                                  | n this  |

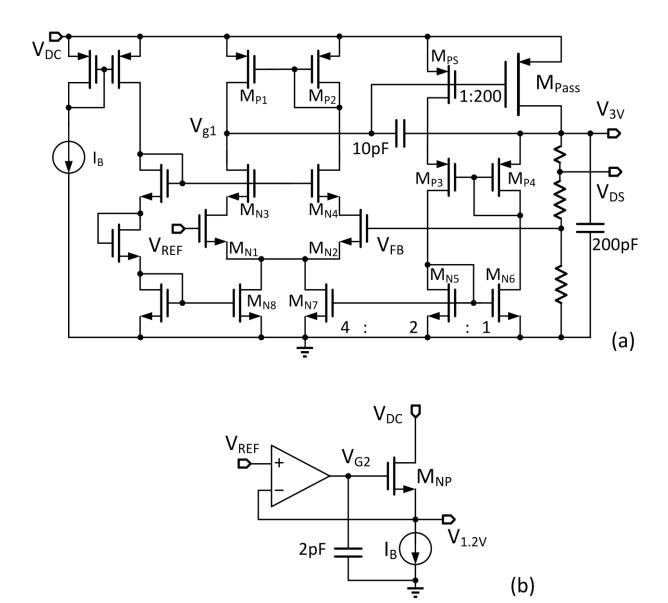

| design.                                                                                                             | 83      |

| Fig. 7.2 (a) The LDO that generates 3 V for ES generator; and (b) the linear regulator                              | or that |

| generates 1.2 V for digital blocks                                                                                  | 85      |

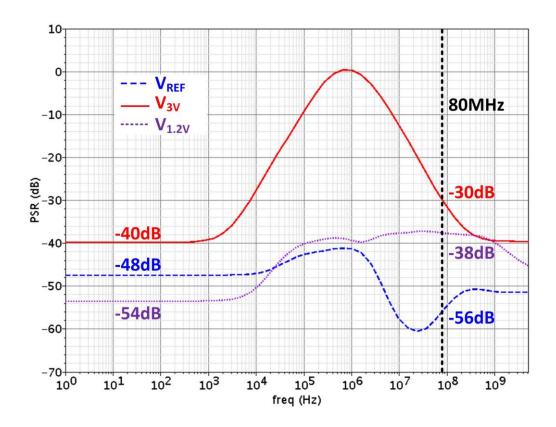

| Fig. 7.3 Simulated PSR of the bandgap reference and the voltage regulators at $V_{\rm DC}=3.2$                      | V. 87   |

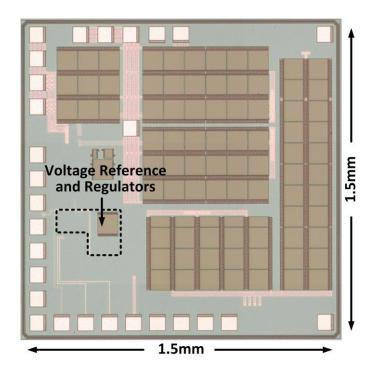

| Fig. 7.4 Chip Micrograph of the MENS implant.                                                                       | 87      |

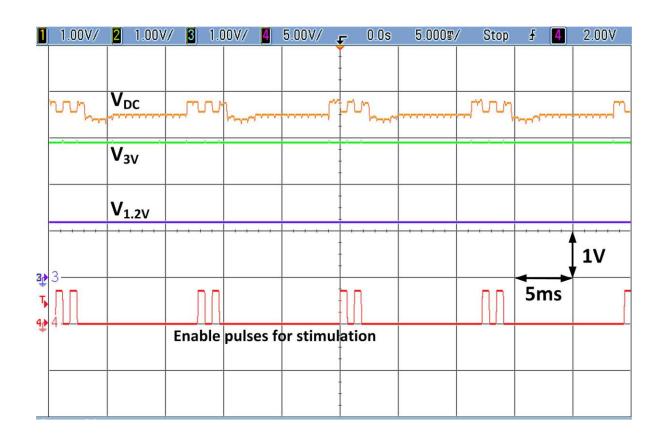

| Fig. 7.5 Measured voltage waveforms of the $V_{\rm DC}$ , $V_{\rm 3V}$ and $V_{\rm 1.2V}$                           | 88      |

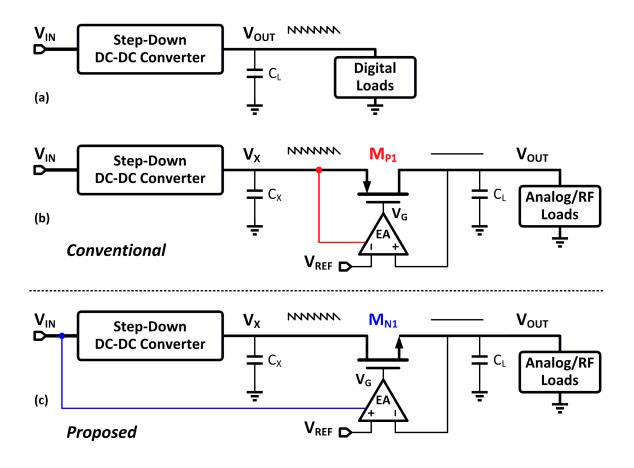

| Fig. 8.1 Conventional PMOS-LDO regulated and proposed NMOS-LDO reg                                                  | ulated  |

| architecture for connecting DC-DC converter and LDO in cascade.                                                     | 89      |

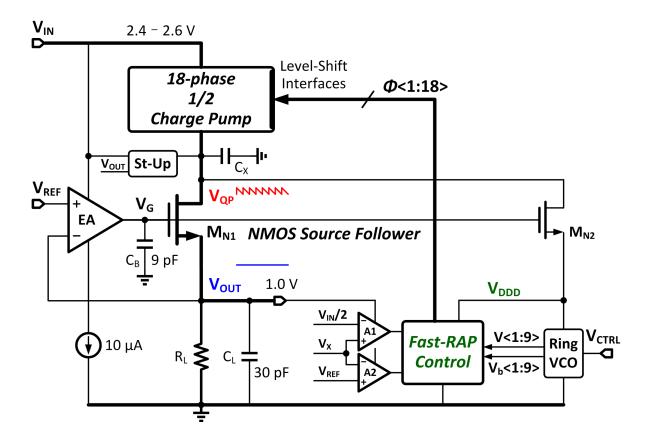

| Fig. 8.2 Block diagram of the fully-integrated NMOS-LDO regulated switched-capacito                                 | r DC-   |

| DC converter with fast-response adaptive-phase control.                                                             | 90      |

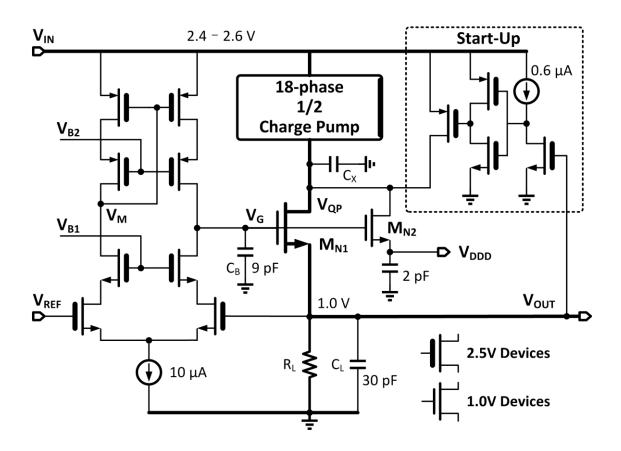

| Fig. 8.3 Schematic of the cascode error amplifier and the start-up circuit                                          | 91      |

| Fig. 8.4 The Fast-RAP control logic with clock frequency tripler (3xClk) and pulse d                                | livider |

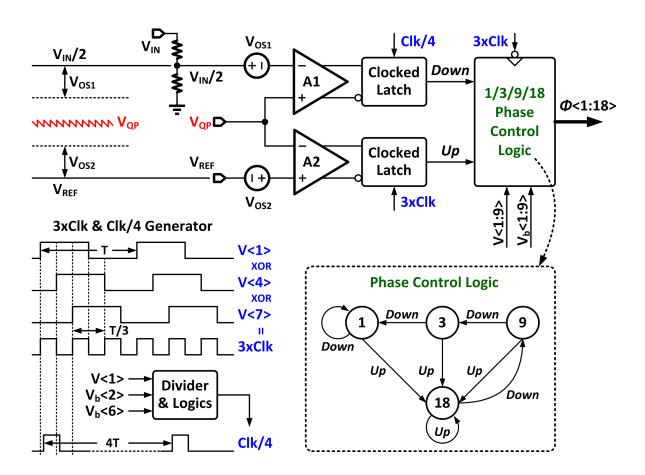

| (Clk/4) and Up/Down signal generated by comparing $V_{\mathrm{QP}}$ with $V_{\mathrm{REF}}$ and $V_{\mathrm{IN}}/2$ | 93      |

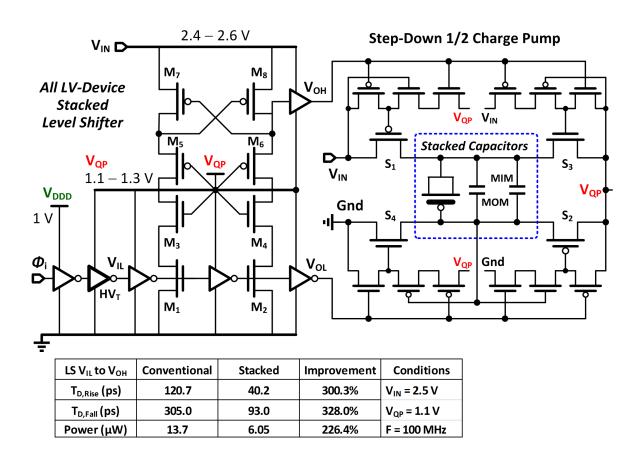

| Fig. 8.5 Unit cell of the 18-phase charge pump with all low-voltage (LV) device stacked                             | l level |

| shifter (LS) and a high- $V_{\rm T}$ inverter at $V_{\rm DDD}$ to $V_{\rm QP}$ interface.                           | 94      |

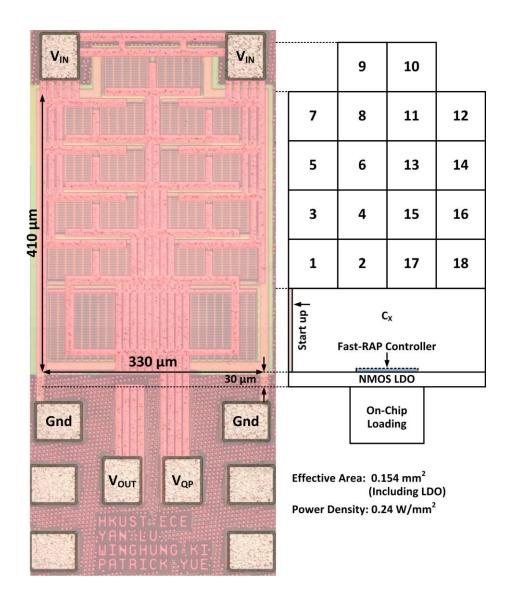

| Fig. 8.6 Chip micrograph of the NMOS-LDO regulated QP.                                                              | 95      |

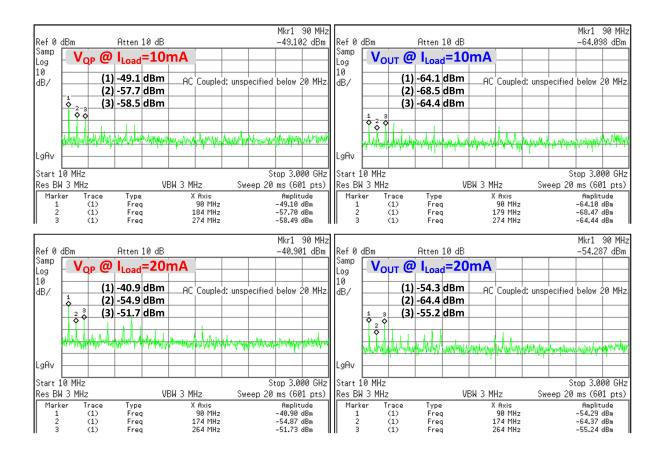

| Fig. 8.7 Measured output spectrums of $V_{QP}$ and $V_{OUT}$ with $I_{Load} = 10$ mA and $20$                       | ) mA,   |

| respectively, at $V_{\rm IN}$ = 2.5 V                                                                               | 96      |

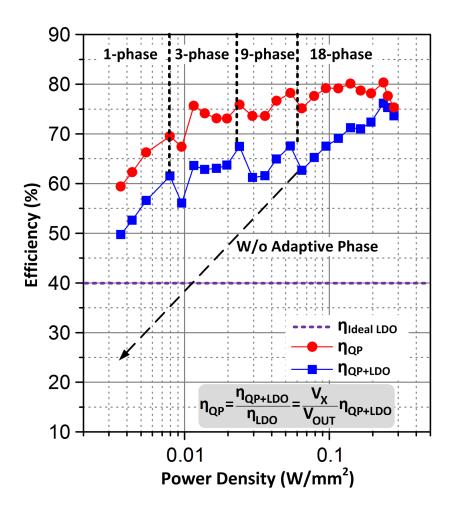

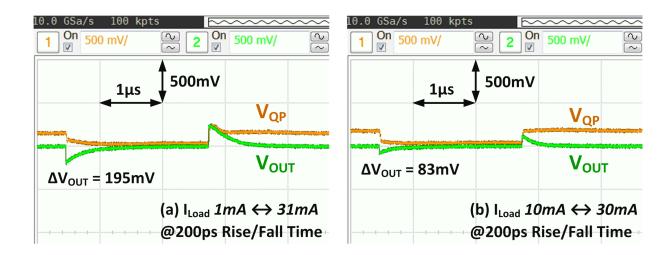

| Fig. 8.8 Measured total efficiency $\eta_{QP+LDO}$ and derived $\eta_{QP}$ at $f_{SW}$ = 90 MHz                     | 97      |

| Fig. 8.9 Measured transient response with on-chip loading                                                           | 97      |

# **List of Tables**

| Table 3.1 Comparison to the State-of-the-Art Rectifiers                      | 33 |

|------------------------------------------------------------------------------|----|

| Table 4.1 Comparison with State-of-the-Art Rectifiers                        | 46 |

| Table 5.1 REALIZATION OF EACH M                                              | 52 |

| Table 6.1 Comparison of LDOs with Output Capacitor                           | 60 |

| Table 6.2 Comparison of Fully-Integrated LDOs                                | 61 |

| Table 6.3 LDO CATEGORIZATION BY INTEGRATION LEVEL AND DOMINANT POLE LOCATION | 62 |

| Table 6.4 Comparison of State-of-the-Art LDOs                                | 82 |

| Table 8.1 Comparison with prior OP works and summary of the NMOS-LDO         | 98 |

# Wireless Power Acquisition and Regulation: Power Management Integrated Circuits for Biomedical Implantable Devices

by

#### Yan Lu

Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology

#### **ABSTRACT**

Implantable microelectronic devices (IMDs), specifically the retinal/cochlear prostheses and the brain-machine interfaces, have gained great breakthroughs in the past decade. Sensations are restored for vision/hearing-impaired or spinal-cord injured people by these IMDs accordingly. Such devices require miniaturized form factor, real-time and high-efficiency wireless power transfer in the range of 10 to 100 mW. In this thesis, power management integrated circuits (PMIC) designed for IMDs are introduced in two parts: (1) wireless power acquisition and (2) regulation.

Inductively coupled (near-field) wireless power transfer is commonly used to power up the IMDs, for the reasons of high efficiency and low human tissue specific absorption rate (SAR) comparing to far-field power transmission. Three high-efficiency active rectifiers (AC-to-DC power converters) are designed, fabricated with standard 0.35  $\mu$ m CMOS process, and measured with inductively coupled PCB air coils. The four diodes of a conventional passive rectifier are replaced by two cross-coupled PMOS transistors and two comparator-controlled NMOS switches to eliminate diode voltage drops such that high voltage conversion ratio could be achieved even at low AC input amplitude  $|V_{AC}|$ . The comparators are implemented with switched-offset biasing to compensate for the delays of active diodes and to eliminate multiple pulsing and reverse current. The first rectifier uses a CMOS peaking current source

to obtain a bias current that is insensitive to the change in  $|V_{AC}|$ . The second and improved rectifier uses a modified CMOS peaking current source with bias current that is quasi-inversely proportional to the supply voltage (QIPV) to better control the reverse current over a wide AC input range (1.5 to 4 V). The third rectifier also employs the novel QIPV bias circuit, and is equipped with reconfigurable 1X or 2X modes for extended-range wireless power transmission. The active rectifiers process the converted magnetic power efficiently to DC electrical power, and constitute the input part of the PMICs for implants.

Since the coupled  $|V_{AC}|$  may change by a couple of times due to relative movements (distance and/or orientation) between the primary and secondary coils, the rectifier DC output voltage would change substantially. Besides, different regulated supply voltages are needed for various functional blocks. For example, the microelectrode may need 2 to 10 V depending on the tissue impedance that is being stimulated; and 1 V is needed for digital and low-power circuits. To improve the overall efficiency, a novel dual-output charge pump (DOQP), consists of one step-down output and one step-up output with variable voltage conversion ratios, is inserted between the rectifier and the low-dropout (LDO) regulator. In addition to the charge pump, an ultra-fast response fully integrated LDO regulator with full spectrum power supply rejection is proposed to improve the performance of noise-sensitive building blocks, such as the RF receiver, the voltage and/or frequency references.

# **Chapter 1 Introduction**

#### 1.1 Research Background

Implantable microelectronic devices (IMDs) have gained great breakthroughs in the past decade. Wirelessly powered cochlear implants have helped hearing-impaired people to restore hearing [1], [2], and retinal prostheses have also succeeded in clinical trials with partial vision restoration [3]-[7]. A successful product of the cochlear implant and a prototype of retinal prostheses are shown in Fig. 1.1. Moreover, there are increasing interests in brain-machine interfaces (BMIs), the diagrammatic sketch of which is shown in Fig. 1.2, due to the recent success in data acquisition from cortical microelectrodes, providing hope for patients with epilepsy, spinal-cord injuries, or Parkinson's disease [8], [9]. Implanted devices with functions such as neural recording and/or stimulation usually need power in the milli-Watt range or higher [1]-[9]. Therefore, biomedical implants with a highly-efficient wireless power transfer scheme that could deliver real-time power in the range of 10 to 100 mW with a small form factor are in great demand.

Fig. 1.1 (a) Cochlear implant [2] and (b) retinal prostheses [4].

Fig. 1.2 Diagrammatic sketch of the BMI.

Fig. 1.3 A generic transcutaneous inductive power link for implantable devices.

Fig. 1.3 shows a generic transcutaneous inductively-coupled power transmission system for implants. Power is received from the secondary winding of the coupling coils, and the unregulated AC input voltage is converted by the rectifier to a DC voltage first, and then regulated to power up functional circuits such as neuron recording and/or stimulating channels as well as the RF transceiver. To achieve high overall system efficiency, every stage of the cascaded power management IC needs to be optimized, while the focus of this research is on the rectifier and the regulator.

#### 1.2 System Requirements

The received power is dependent on the coupling coefficient k between the primary (external) coil and the secondary (internal) coil. Unfortunately, k varies significantly with the distance and orientation between these two coils. As a result, the active rectifier in Fig. 1.3 should be designed to accommodate a wide range of AC input amplitude [10], [20]-[23].

Besides, different regulated supply voltages are needed for various functional blocks. For example, the microelectrode may need 2 to 10 V depending on the tissue impedance that is being stimulated; and sub-1 V is needed for digital and low-power circuits. To realize these output voltages, switched-capacitor power converters (SCPC, a.k.a. charge pump, QP, Q stands for charge) with step-up and/or step-down capabilities are more commonly used in the IMDs than inductive switching converters, because on-chip capacitors can be more easily integrated that take full advantages of advanced processes when compared to (off-chip) inductors.

Since there are many noise-sensitive building blocks (such as the RF receiver, analog-to-digital converter, digital-to-analog converter, and voltage/frequency references) in an IMD, well regulated power supplies are needed, and traditionally linear regulators are used. However, the efficiency of a linear regulator is poor if there is a large difference between the supply voltage and the output voltage. To accomplish high overall power efficiency, the dropout voltage of the linear regulator should be kept low. Therefore, a low dropout (LDO) regulator should be used, and a fully-integrated LDO that can only have limited filtering capacitance should still provide good power supply rejection (PSR), as well as fast load and line transient responses.

From the system point of view, with these fully-integrated PMICs that require a few or no discrete components, the volume of the IMDs could be considerably shrunk, such that the IMDs could be more reliable and more easily implanted.

From the circuit perspective, state-of-the-art performances should be accomplished for each individual circuit: by operating at 13.56 MHz, both the input tuning capacitors and the output filtering capacitors are expected to be integrated on-chip; the dual-output charge pump is expected to effectively convert the rectified voltage into two or more supply voltages for different functional blocks in the IMDs; and the on-chip LDO should provide a well-regulated voltage with full-spectrum PSR to supply power to noise-sensitive blocks, and response fast to the load transient current with limited load capacitance.

In a nutshell, this research is targeted as designing, implementing and measuring innovative, area-efficient and high efficiency power management integrated circuits, including AC-to-DC converter, switched-capacitor power converter and low dropout regulators for biomedical implantable devices.

#### **1.3 Operation Frequency**

Wireless power transfer systems can be divided into two categories according to transmission modes of near-field and far-field operations. As shown in Fig. 1.4, the near-field operation assumes that the transmission distance is much smaller than the wavelength, that is,  $d \ll \lambda$ ; while the far-field operation has the wavelength being much smaller than the transmission distance, that is,  $\lambda \ll d$ .

In selecting the frequency for the wireless power link operating in the near-field condition (also known as the inductively-coupled condition), that is, the distance between the coils is much smaller than the wavelength  $\lambda$ , suggestions of 1 to 3 MHz are common [3], [10] as power attenuation through human tissue increases at higher frequencies. However, switching at high frequency could reduce the volume of the resonance LC tank and the output filtering capacitor such that the whole implant could be integrated on-chip or on-package. Besides, smaller inductance with higher Q can be more easily achieved at higher frequencies within

limited space, and this is one of the key factors in improving the overall efficiency of the wireless power transfer system. An additional advantage is that the data coil could be eliminated by transmitting the uplink data through the power link using time interleaving if the wireless power transmission frequency is sufficiently high to achieve the required data rate. In this research, we choose 13.56 MHz in the readily available ISM band. Although 13.56 MHz is on the high side of the frequencies that have been conventionally adopted for inductively-coupled power transmission, the specific absorption rate (SAR) in the tissue is still quite low compared to the thermal power dissipation in the coils [11].

For far-field power transmission, the output power level is limited as the coil distance is larger (in other words, the coil diameter is smaller), making it more difficult for the EM wave to be focused and transmitted from the transmitting antenna to the receiving loop antenna efficiently. For example, the wireless power link in [12] uses 915 MHz that operates at the boundary of near-field and far-field transmission in delivering a few hundred micro-watt.

As a comparison, applications such as wireless mobile phone charger uses 6.78 MHz or 13.56 MHz for fast loop response to the load transient [13], [14]; and [15] operates at 6.78 and 13.56 MHz uses coils with magnetic core to increase the power transfer efficiency by 3 times; however, the magnetic core is heavy and not suitable for implantable devices; and ~150 kHz that is compliant with IEEE Qi standard [16] is used for higher power conversion efficiency [17]; and 900MHz is often used in long distance RFID applications [18].

Fig. 1.4 Wireless power transfer systems with (a) near-field or (b) far-field operation, respectively.

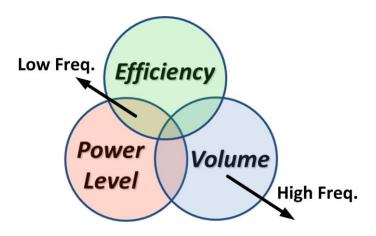

The selection of the operation frequency is a tradeoff between efficiency, device volume and power level as shown in Fig. 1.5. Our target output power is in the tens of mW range with air coils, and taking the above factors into consideration, we decided to use 13.56 MHz with near-field coupling.

Fig. 1.5 Tradeoffs in selecting the operation frequency.

#### 1.4 Conclusion

Wireless power transfer has many applications such as implantable medical devices (IMDs), RFIDs, and electric vehicle and mobile phone wireless chargers. In this research, wireless power transfer for the first application is investigated. This research faces many design challenges, especially a miniature size is required. The operation frequency is chosen to be 13.56 MHz with near-field operation for good tradeoffs among efficiency, device volume and power level in this specified case.

### **Chapter 2 RECTIFIER: FROM PASSIVE TO ACTIVE**

#### 2.1 Passive Rectifier

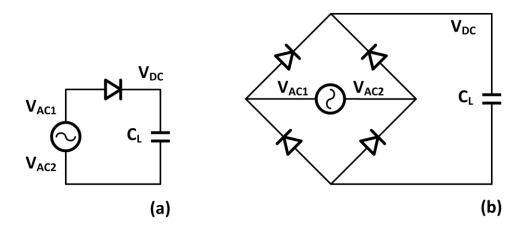

Diode, the simplest semiconductor device, can be easily used to convert AC voltage into DC voltage as shown in Fig. 2.1. The half-wave rectifier delivers current from the sinusoidal AC source to the DC output when the positive amplitude is higher than the DC output voltage; while the full-wave rectifier delivers current to the output at both positive and negative peak points. That means the time interval for charge transfer of a half-wave rectifier is only half of that of a full-wave rectifier. Thus, in delivering the same load current with the same output capacitor, the output ripple of the half-wave rectifier is basically two times higher than that of the full-wave rectifier.

In standard CMOS processes, the diodes can be replaced by diode-connected MOS transistors. This is a cost-effective way to implement the passive rectifier [10]. However, the transconductance  $g_m$  of the MOS transistors is smaller than the  $g_m$  of a real PN junction diode [19]. This requires a large  $V_{GS}$  for MOS transistors when driving a large current, which means that it is less efficient when compared to using diodes. If low-threshold voltage transistors are used to reduce the  $V_{GS}$ , reverse (sub-threshold) leakage current would increase accordingly.

Fig. 2.1 (a) Half-wave rectifier, and (b) full-wave rectifier

#### 2.2 Active Rectification for IMDs

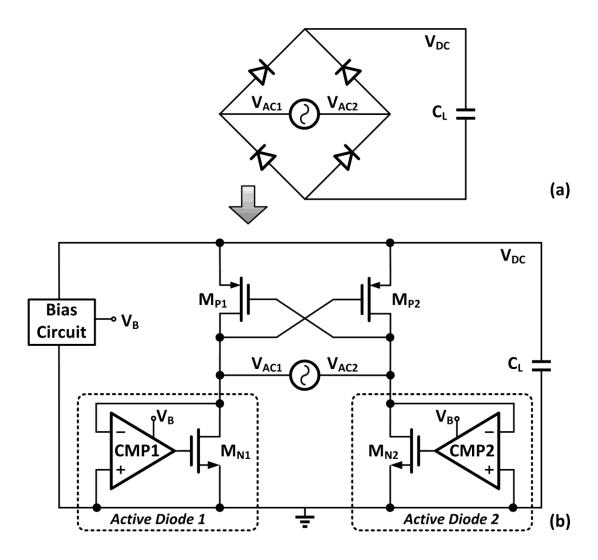

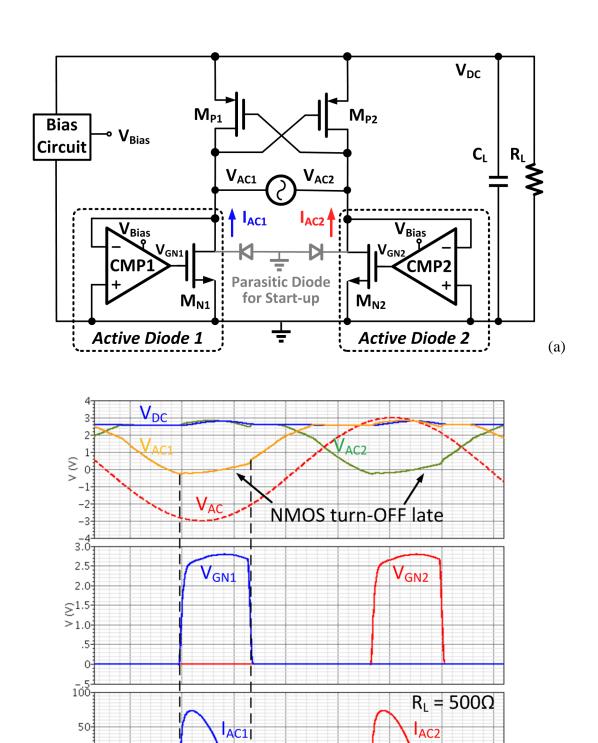

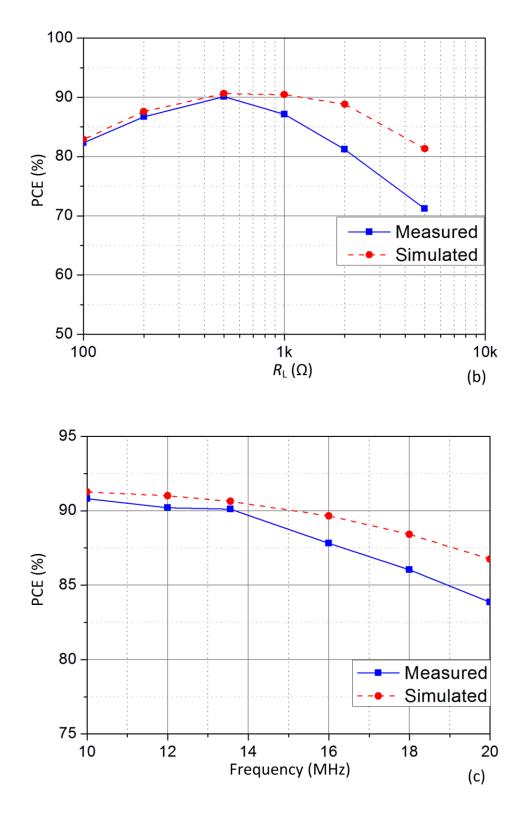

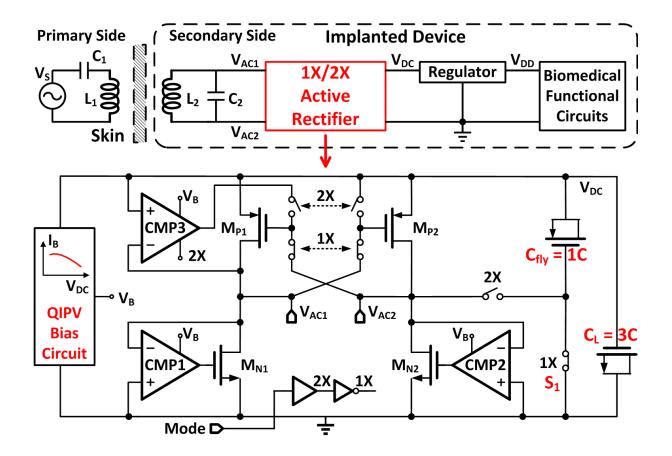

The diode voltage drop ( $V_{\rm diode} \approx 0.7 \text{ V}$ ) of a passive rectifier, as shown in Fig. 2.2(a), limits the voltage conversion ratio (M) and the power conversion efficiency (PCE). The full-wave active rectifier shown in Fig. 2.2(b), of which the upper diodes are replaced by two cross-coupled PMOS switches and the lower diodes by two comparator-controlled NMOS switches (active diodes), reduces the voltage drop from  $2V_{\rm diode}$  to  $2V_{\rm DS}$  ( $V_{\rm DS}$  is the turn-on voltage of the power switches). When operating at a high frequency such as 13.56 MHz, comparator delay and gate-drive buffer delay affect the efficiency of the rectifier, as reverse current will occur if large power switches are not turned off correctly. Many schemes were proposed to tackle the above problems [20]-[25].

Fig. 2.2 (a) The passive full-wave rectifier, and (b) the active full-wave rectifier.

#### 2.2.1 Operation Principle and Problems of Active Rectifiers

An important parameter in evaluating a full-wave rectifier is the voltage conversion ratio M, defined as

$$M = \frac{V_{\rm DC}}{|V_{\rm AC}|} \tag{2.1}$$

where  $|V_{AC}|$  is the amplitude of the input AC signal to the rectifier, and  $V_{DC}$  is the averaged rectified output DC voltage. By replacing the four diodes of a full-wave rectifier with power transistors, M is significantly increased even when the input amplitude is low. The generic active rectifier, shown in Fig. 2.2(b), consists of an LC tank, cross-coupled PMOS transistors, comparator controlled NMOS switches (active diodes), a bias current generator and an output filtering capacitor  $C_L$ . The operation principle is demonstrated by the simulated waveforms shown in Fig. 2.3, as follows. When  $V_{AC2} - V_{AC1} > |V_{tP}|$  (threshold voltage of  $M_{P1,2}$ ),  $M_{P2}$  is turned on; and when  $V_{AC1}$  swings below 0 V, the comparator CMP1 turns on the switch  $M_{N1}$ , charging up  $V_{DC}$  by  $V_{AC}$ . After  $V_{AC1}$  swings above zero,  $M_{N1}$  is then turned off by CMP1. During the next half of the AC input cycle, the other half of the rectification circuit will conduct in a similar fashion as described above.

With proper control of the power switches, a high voltage conversion ratio could be obtained. However, in reality, the delay time  $t_{\rm delay}$  of the comparator and the gate drive buffer will limit the dynamic performance. The propagation delay of the rising edge of the comparator  $t_{\rm pLH}$  will shorten the current conduction time  $\Delta t$ , limiting the highest operation frequency of the active rectifier. On the other hand,  $t_{\rm pHL}$  of the output falling edge forces the power NMOS transistors  $M_{\rm N1,2}$  to turn off late, and charge of the output capacitor will flow back to ground through  $M_{\rm N1,2}$ , resulting in reverse leakage current  $I_{\rm leak}$  as shown in Fig. 2.3. This is the main challenge of active rectifier designs [20], [21]. To eliminate  $I_{\rm leak}$ , power transistors  $M_{\rm N1,2}$  have to be turned off immediately when  $V_{\rm AC}$  goes below  $V_{\rm DC}$ . However,  $M_{\rm N1,2}$  have to be large to handle a large output current, increasing the response times of the active diodes. This problem is more pronounced when the operation frequency is required to be high and the input amplitude  $|V_{\rm AC}|$  is low (for example, below 1.5 V) because delay times of comparators and buffers are inversely proportional to the supply voltage.

Fig. 2.3 (a) The active full-wave rectifier, and (b) its simulated waveforms of reverse current problem in active rectifier.

1.99

time (us)

I<sub>Reverse</sub>

2.02

2.01

2.03

(b)

I (mA)

-50·

1.96

1.97

1.98

#### 2.2.2 Comparison of Comparator Delay Compensation Schemes

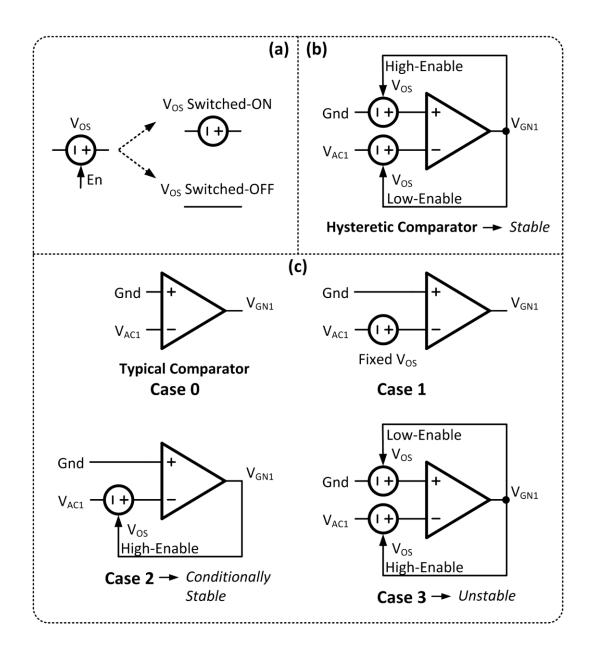

Fig. 2.4 (a) Symbol of artificial switched-offset; (b) hysteretic comparator; and (c) comparator schemes for reverse current control.

To achieve a higher voltage conversion ratio and PCE, the power transistors  $M_{\rm N1,2}$  should be turned off right before reverse current occurs [20]-[26]. Comparators with unbalanced bias currents or asymmetric differential input are used to set an artificial input offset voltage to compensate for the delay and to turn the power switches on and off properly. The symbol of artificial input offset with an enable pin is shown in Fig. 2.4(a). When the enable bit is high, a non-zero offset voltage is introduced to the comparator; and when the enable bit is low, the

offset voltage is zero (a wire). Prior reverse current control schemes fall into one of the cases sketched in Fig. 2.4(b). Case 0: the comparators have no artificial offset (reverse current occurs due to delays). Case 1: The comparators have fixed artificial offset such that the power switches are turned off earlier, but turned on later. Case 2: The comparators have dynamic artificial offset such that the power switches are only turned off earlier. Case 3: The comparators have dynamic artificial offset at both edges such that the power switches are turned on and off earlier.

To compare the performance of the above comparator schemes on especially low-voltage active rectifiers, the quantity Crest Factor (CF) used in evaluating electrical appliances is employed. CF is the ratio between the peak current delivered to the load and the corresponding RMS current

$$CF = \frac{I_{p}}{I_{RMS}}.$$

(2.2)

A higher CF means a higher peak current for the same load condition, and larger power transistors are thus needed to reduce the  $V_{\rm DS}$  for achieving high voltage conversion ratios. Routing metal needs to be wider for a higher CF as well.

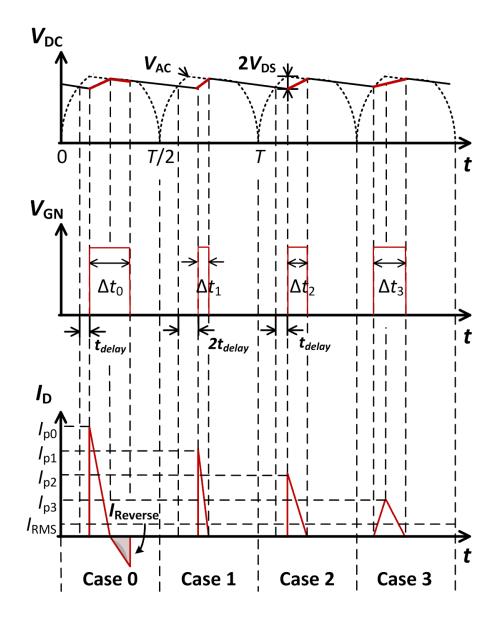

The scenarios of current conduction of Case 0 to Case 3 are sketched in Fig. 2.5 and discussed as follows. Case 1 is implemented in [21] and [25], with constant offset introduced to the comparators using unbalanced bias currents [21] or asymmetrical differential input transistors [25]. The power NMOS switches are turned off earlier by  $t_{\rm delay}$  to eliminate the reverse current; however, they are turned on later by  $2t_{\rm delay}$  than the ideal case, and the conduction time  $\Delta t_1$  is  $2t_{\rm delay}$  shorter. For the same load current, the peak current  $I_{\rm p1}$  has to be higher, limiting its operation at a higher frequency. The delays get worse when  $|V_{\rm AC}|$  is low. Moreover, the simple bias circuit that determines  $t_{\rm delay}$  is strongly affected by  $|V_{\rm AC}|$ .

Fig. 2.5 Conceptual waveforms of the input/output voltages, power NMOS gate voltage and conducted currents for active rectifiers with different comparators.

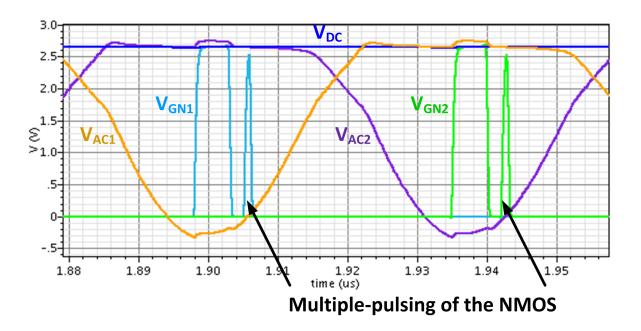

In [20], self-biased active diodes are employed, and to reduce or eliminate  $t_{\rm delay}$ , a reverse current control (RCC) scheme (Case 2) is introduced. However, both the bias current and the operation of the RCC transistor are highly affected by  $|V_{\rm AC}|$  and process variations, making the rectifier hard to be optimized over a wide input range. Moreover, as the reverse current control is realized by a time-varying offset, the artificial offset would disappear right after the power NMOS transistor is turned off. If the RCC transistor turns on prematurely (for example, due to process variations) and turns off the active diode while  $|V_{\rm AC}|$  is still higher than  $V_{\rm DC}$ , the comparator will go high again in the same cycle. Simulation waveforms of the described

scenario are shown in Fig. 2.6. The efficiency would deteriorate with this multiple pulsing problem, especially in light load condition when switching loss dominates.

Case 3 is realized in [23] and [24], where it uses self-biased active diodes similar to [20], with an offset-control function for the comparators to compensate for both turn-on and turn-off delays such that  $\Delta t_3$  could be maximized (lowest CF). It suffers from the same and even worse multiple-pulsing problem as [20], as the dynamic offset (+/- offset voltages) transition of the offset-control circuit is unstable: when the comparator outputs a 1(0), the dynamic offset flips the output to 0(1), and this positive feedback makes the comparator undergoes self-oscillation. This phenomenon is what a Schmitt trigger designed to avoid. To make the scheme work, [23] adds a delay cell in the offset-control path in addition to its calibration bits. If the delay time  $t_{\rm dp}$  is large enough (comparable to half period), the comparator could be stable, but then the power switch would be turned on for at least the duration of  $t_{\rm dp}$  that limits the minimum conduction time ( $\Delta t_{\rm min} > t_{\rm dp}$ ). This property makes its operation more like a constant-on time control at light load condition. As a result, its light load efficiency is degraded.

Fig. 2.6 Simulated waveforms of multiple-pulsing problem associated with dynamic offset schemes.

To summarize, Case 2 has larger  $\Delta t$  than Case 1, and in the ideal situation, Case 3 has the largest  $\Delta t$ . However, a comparator with both compensated turn-on and turn-off delays is

logically unstable: the hysteresis goes the opposite direction as a normal Schmitt trigger goes, and the robustness of the rectifier is degraded. In our proposed works ([22] and [26]), Case 2 is employed. It has a longer  $\Delta t$  compared to Case 1, and is more robust compared to Case 3.

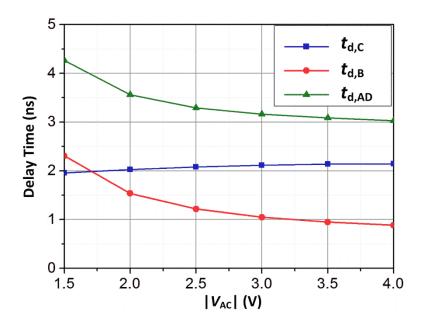

#### 2.2.3 Delay Time of Active Diodes

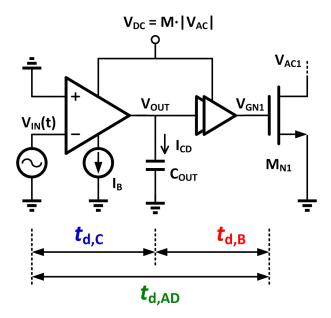

Before discussing the current source to be used to bias CMP1 and CMP2, the delay time of the active diode  $t_{\rm d,AD}$  should be investigated first. The parameter  $t_{\rm d,AD}$  consists of the comparator delay  $t_{\rm d,C}$  and the gate drive buffer delay  $t_{\rm d,B}$ . To simplify the calculation, as shown in Fig. 2.7, the supply voltage of a typical comparator and buffer is connected to  $V_{\rm DC}$  that is AC input dependent, and the input signal is assumed to be sinusoidal, that is,  $V_{\rm in}(t) = \alpha |V_{\rm AC}| \times \sin(2\pi t/T)$ , where  $\alpha$  is a scaling factor. Let the trigger point of the inverter buffer be the 50% point of  $V_{\rm DC}$ , that is,  $M|V_{\rm AC}|/2$  (M=0.9). Using the small-signal model, the output current  $I_{\rm CD}(t)$  that charge/discharge the output capacitor  $C_{\rm OUT}$  is

$$I_{CD}(t) = g_m V_{in}(t) = g_m \alpha |V_{AC}| \sin(2\pi t/T)$$

(2.3)

where  $g_m$  is the transconductance of the comparator input stage. The comparator delay  $t_{d,C}$  is the time that  $I_{CD}(t)$  charges the capacitor  $C_{OUT}$  by  $V_{DC}/2$ :

$$\int_{0}^{t_{\text{d,c}}} I_{\text{CD}}(t) dt = \int_{0}^{t_{\text{d,c}}} g_{m} \alpha |V_{\text{AC}}| \sin(2\pi t/T) dt$$

$$= C_{\text{OUT}} V_{\text{DC}} / 2 = C_{\text{OUT}} M |V_{\text{AC}}| / 2$$

(2.4)

For  $t \ll T$ ,  $\sin(2\pi t/T) \approx 2\pi t/T$ , and we have

$$\frac{1}{2} g_m \alpha |V_{AC}| 2\pi t_{d,C}^2 / T = C_{OUT} M |V_{AC}| / 2.$$

(2.5)

Therefore,

$$t_{\rm d,C} = \sqrt{\frac{MC_{\rm OUT}T}{2\pi\alpha g_m}} = \sqrt{\frac{MC_{\rm OUT}T}{2\pi\alpha\sqrt{2I_{\rm B}k_{\rm n}(W/L)}}}.$$

(2.6)

From (2.6) we have  $t_{\rm d,c} \propto \sqrt[4]{I/I_{\rm B}}$ . If  $I_{\rm B}$  is independent of  $V_{\rm DC}$ , then so does  $t_{\rm d,C}$ . The simulated  $t_{\rm d,C}$  of Fig. 2.7 is plotted in Fig. 2.8, which verified the above calculations that  $t_{\rm d,C}$  has a very weak relation with  $I_{\rm B}$ . However, all the previous bias current generation circuits would provide an  $I_{\rm B}$  that is more or less proportional to  $V_{\rm DC}$ , in such a case

Fig. 2.7 Simplified schematic of active diode 1 with emphasis on supply voltage, input signal and load capacitor for delay calculations.

Fig. 2.8 Simulated active diode delay  $t_{d,AD}$ , comparator delay  $t_{d,C}$  and gate drive buffer delay  $t_{d,B}$  with respect to  $|V_{AC}|$ .

$$t_{\rm d,C} \propto \sqrt[4]{I/I_{\rm B}} \propto \sqrt[4]{|V_{\rm AC}|}$$

(2.7)

On the other hand, the buffer delay  $t_{d,B}$  would change inversely proportional to the supply voltage, according to the calculated propagation delay (the time to reach the 50% point) of an inverter [27]:

$$t_{\rm p} = 0.69 \frac{3}{4} \frac{C_{\rm L} V_{\rm DC}}{I_{\rm DS}} \left( 1 - \frac{7}{9} \lambda V_{\rm DC} \right)$$

$$= 0.52 \frac{C_{\rm L} V_{\rm DC} (1 - \frac{7}{9} \lambda V_{\rm DC})}{k'(W/L) V_{\rm DSsat} (V_{\rm DC} - V_{\rm t} - V_{\rm DSsat} / 2)}$$

(2.8)

where  $I_{\rm DS}$  is the drain current,  $k' = \mu C_{\rm ox}$ , and  $\lambda$  is the channel-length modulation factor. Assuming that  $V_{\rm DC} - V_{\rm t} >> V_{\rm DSsat}/2$  and  $\lambda = 0$ , (2.8) can be written as

$$t_{\rm P} = t_{\rm d,B} = 0.52 \frac{C_{\rm L}}{k'(W/L)(V_{\rm DC} - V_{\rm t})}$$

(2.9)

From the above first-order approximation, we learn that  $t_{d,B}$  is approximately inversely proportional to the supply voltage. Consequently, to keep  $t_{d,B}$  approximately constant we need an adaptive current source that is approximately inversely proportional to  $V_{DC}$ .

#### 2.3 Conclusion

Active rectifiers are widely used in low-voltage AC-to-DC power conversion to achieve higher voltage conversion ratio and power conversion efficiency. However, active rectifiers also suffer from active-diode delay problem that would introduce reverse current and consequently degrade the efficiency. Delay times of active diodes are calculated and simulated in this research, and the total delay time shows an inverse relationship with the power supply. Different comparator delay compensation schemes were proposed to solve this problem, but each scheme has their pros and cons as discussed in this section. Circuit implementations of the comparator and the bias current designed to fix the above problems will be given in the following chapter.

# **Chapter 3 ACTIVE RECTIFIER IMPLEMENTATIONS**

Two full-wave active rectifiers (labeled as Rec1 and Rec2, respectively) are proposed, implemented and measured in a 0.35  $\mu$ m CMOS N-well process in this research. Both of them are using delay time compensated comparators with the proposed switched-offset scheme. The two designs used different bias current sources, with the second being an improved version over the first. The first one (Rec1) [22] used a peaking current source, while the second one (Rec2) [26] used a proposed quasi-inversely proportional to  $V_{DC}$  (QIPV) current source. Detailed analysis, optimization and measurement results will be presented in this chapter.

#### 3.1 Comparator with Switched-Offset

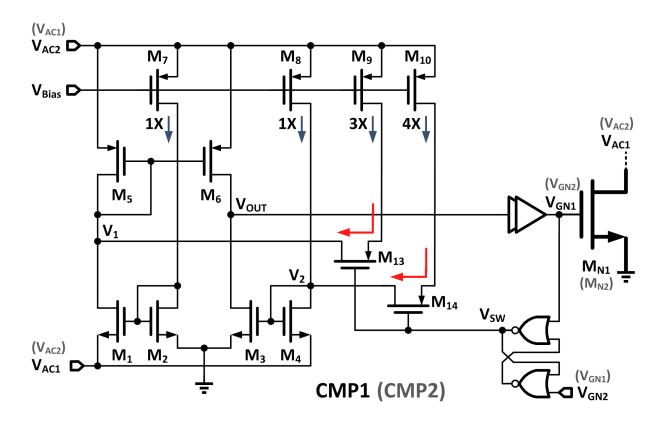

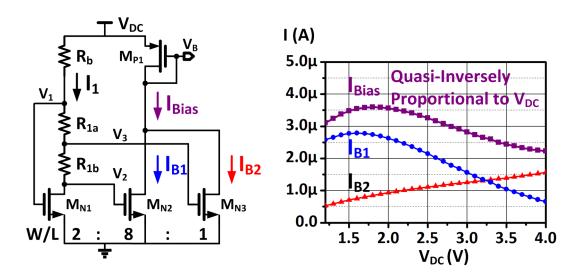

Fig. 3.1 The proposed delay time compensated comparator with switched-offset scheme (Active Diode 1(2) in Fig. 2.3).

In our proposed switched-offset scheme, delay time compensation is realized by comparators with time-varying offset voltages associated with a specially designed current source, as shown in Fig. 3.1. The two comparators CMP1 and CMP2 are push-pull differential commongate comparators, and the dynamic switched currents are also implemented in a push-pull fashion, for minimizing power consumption and also for reducing the comparator response time [21]. When  $V_{AC2} - V_{AC1} > |V_{IP}|$ ,  $M_{P2}$  is turned on. When  $V_{AC1}$  swings below 0 V,  $M_1$  of CMP1 sinks a larger current than  $M_2$ , causing  $M_6$  to source a larger current than  $M_3$  can sink, thus driving  $V_{OUT}$  as well as  $V_{GN1}$  high and turns on the active diode switch  $M_{N1}$ . As a result, the rectifier filtering capacitor  $C_L$  is charged up by  $V_{AC}$ . Note that in the previous phase,  $V_{GN2}$  has been high, causing  $V_{SW}$  of CMP1 to be high, and the switches  $M_{11}$  and  $M_{12}$  are turned off. In the present phase,  $V_{GN1}$  drives  $V_{SW}$  low and turns on  $M_{11}$  and  $M_{12}$ , allowing auxiliary bias currents from  $M_9$  and  $M_{10}$  to introduce the designed DC offset. This offset voltage of the differential pairs with unbalanced bias currents is

$$V_{\text{OS}} = \sqrt{\frac{2I_{+}}{k_{\text{n}}(W/L)}} - \sqrt{\frac{2I_{-}}{k_{\text{n}}(W/L)}}$$

$$= (\sqrt{n} - 1)\sqrt{\frac{2I_{-}}{k_{\text{n}}(W/L)}} = (\sqrt{n} - 1)V_{\text{OV-}},$$

(3.1)

where  $k_n = \mu_n C_{ox}$ ,  $I_+$  and  $I_-$  are the unbalanced bias currents, n is the ratio of  $I_+$  and  $I_-$ , and  $V_{OV-}$  is the gate overdrive voltage of  $M_1$  through  $M_4$  when they are operating with balanced bias current (1X). The sizes of the common-gate input pairs  $M_1$  through  $M_4$  are the same, with  $V_{OV-}$  lower than 100 mV. The bodies of  $M_1$  through  $M_4$  are all connected to the on-chip ground, such that the threshold voltage  $V_{tN}$  of  $M_1$  and  $M_4$  would be smaller than  $V_{tN}$  of  $M_2$  and  $M_3$  when  $V_{AC1} < 0$  due to the body effect. The bias currents of  $M_7$  through  $M_{10}$  are 1X, 1X, 3X and 4X respectively. The current of  $M_{10}$  should be 3X (same as  $M_9$ ); however, taking the body effect of  $M_4$  into consideration, it is set as 4X instead to make  $V_2$  even higher. The current ratio n is equal to four in our case, and the value of the dynamic artificial offset (around 100 mV) is set by the current ratios of  $M_7$  through  $M_{10}$ . The auxiliary bias currents also serve as slew-rate enhancement currents that charge up  $V_1$  and  $V_2$ , starving  $M_6$  and feeding  $M_1$ . Hence,  $V_{OUT}$  is pulled low, turning off the power switch  $M_{N1}$  right before  $V_{AC1} > 0$  to prevent the occurrence of reverse current. A NOR SR-latch is added at each output of the

comparators to avoid the aforementioned multiple-pulsing problem that is caused by the dynamic offset scheme. Due to the NOR implementation of the SR-latch,  $V_{SW}$  stays low even when  $V_{GN1}$  goes low, such that  $M_1$  and  $M_4$  are saturated by the auxiliary bias currents, and prevent  $M_{N1}$  from turning on again in the same phase even if  $V_{AC1}$  is still lower than 0 V, thus eliminating multiple-pulsing.

To save static power, the power supplies of the comparators CMP1 and CMP2 are connected to (the distorted sinusoidal waveforms)  $V_{\rm AC2}$  and  $V_{\rm AC1}$ , respectively, such that only one comparator is biased to work in every phase [20]. In addition, the  $V_{\rm OUT}$  node of the comparators is coupled to ground in the layout, to make sure that this high-impedance node would not jump when the supply ( $V_{\rm AC2}$  or  $V_{\rm AC1}$ ) is low. However, to eliminate multiple pulsing, the power supply of the gate drive buffers and the latches should be connected to the DC output  $V_{\rm DC}$ . All N-wells are connected to  $V_{\rm DC}$ . Some PN junctions (P+ active area to N-well) are slightly forward biased by  $V_{\rm AC2} - V_{\rm DC}$  (or  $V_{\rm AC1} - V_{\rm DC}$ , equal to  $V_{\rm DS}$  of the power PMOS that is approximately 70 mV), the associated leakage current is negligible. When  $V_{\rm AC2}$  or  $V_{\rm AC1}$  is slightly higher than  $V_{\rm DC}$  during the conduction time, the matched currents of  $M_7$  through  $M_{10}$  would be larger than the designed bias current with larger  $V_{\rm GS}$ . This arrangement is good for the comparators to have more instantaneous current and faster response.

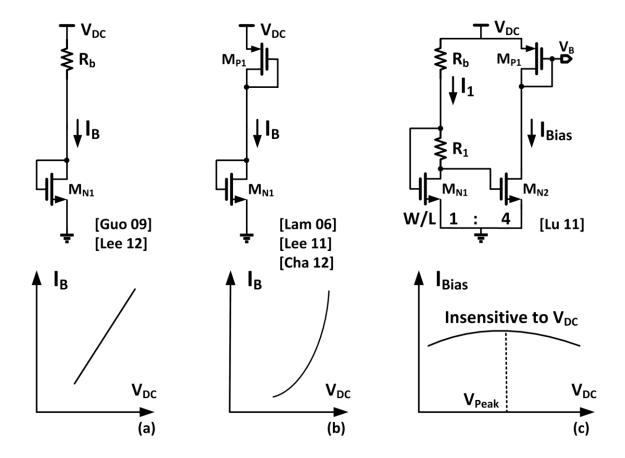

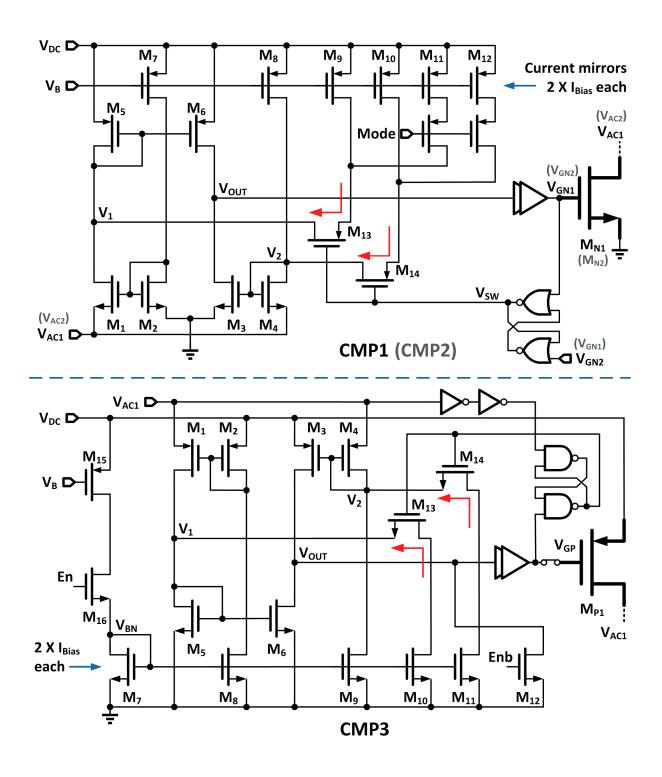

#### 3.2 Current Source Design

For a robust design, the bias circuit of the active rectifier should not require a startup circuit, as this is the frond-end of the wireless power receiver. As shown in Fig. 3.2, in [21], [24], a simple current source with a diode-connected MOS transistor driving a resistor is used; and in [20], [23] and [25], self-biased current sources are used. The above schemes give the bias current approximately proportional to the input voltage amplitude  $|V_{AC}|$ . In [22], a peaking current source (PCS) with all transistors operating in the saturation region [28] is used to bias the comparators so that the bias current would stay approximately constant when  $|V_{AC}|$  changes. However, for a constant  $t_{d,AD}$ , the bias current should be approximately inversely proportional to  $|V_{AC}|$ . In the proposed design [26], to further improve the performance at low  $|V_{AC}|$ , the bias current is set quasi-inversely proportional to  $|V_{AC}|$  ( $\approx V_{DC}$ ), labeled as QIPV biasing and shown in Fig. 3.3(b), such that the comparator offset could be well controlled over the whole AC input range.

Fig. 3.2 Bias circuits without start-up requirement.

Fig. 3.3 Schematic of (a) peaking current source for Rec1 and (b) the proposed QIPV biasing circuit for Rec2.

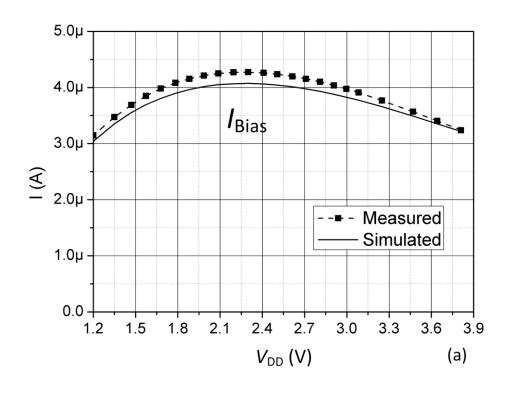

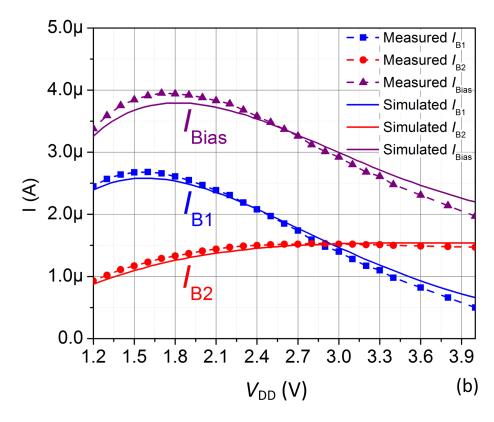

Fig. 3.4 Simulated and measured output current versus supply voltage of (a) peaking current source for Rec1 and (b) the proposed QIPV biasing circuit for Rec2.

The bipolar peaking current source was discussed in [29], and CMOS peaking current source was discussed in [30] and studied in [28]. With reference to Fig. 3.3(a), the relationship of  $I_1$  and  $I_{\text{Bias}}$  are given by

$$I_{1} = \frac{V_{\text{DD}} - V_{\text{GS1}}}{R_{\text{b}}} = \frac{1}{2} k_{\text{n}} \left( \frac{W}{L} \right)_{1} \left( V_{\text{GS1}} - V_{\text{tN}} \right)^{2}$$

(3.2)

$$I_{\text{Bias}} = \frac{1}{2} k_{\text{n}} \left( \frac{W}{L} \right)_{2} \left( V_{\text{GS1}} - V_{\text{tN}} - I_{1} R_{1} \right)^{2}.$$

(3.3)

For  $I_{\text{Bias}}$  to be insensitive to the change of  $I_1$ , we set  $dI_{\text{Bias}}/dI_1$  to zero, and using (3.2) and (3.3), the condition for locating the maxima is

$$I_{1}R_{1} = \frac{1}{2} (V_{GS1} - V_{tN}), \tag{3.4}$$

and the bias current peaks at the nominal  $V_{DC}$  that we use to calculate  $I_1$ , that is,  $I_1 = (V_{DC,nom} - V_{GS1})/R_b$ .

A simple assignment is to set  $(W/L)_2 = 4(W/L)_1$  to give  $I_{Bias} = I_1$ . As shown in Fig. 3.4(a), measurement results match well with simulation results [22]. The peak current is designed to be around 4.1  $\mu$ A when the supply voltage is 2.3 V, and the minimum bias current is 3.2  $\mu$ A when  $V_{DC} = 3.8$  V. Note that when  $V_{DC}$  changes from 1.2 to 3.8 V,  $I_1$  changes by over  $\pm 50\%$ , but the bias current changes by only  $\pm 12.3\%$ .

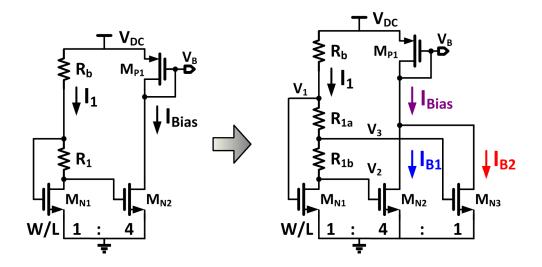

To realize a bias current that is inversely proportional to  $V_{\rm DC}$ , one may set the peak current point to be the lowest  $V_{\rm DC}$  in the application (1.2 V in our case). However, due to the quadratic relation, the bias current will drop too much at the highest  $V_{\rm DC}$  (3.8 V). Our proposed QIPV biasing circuit is shown in Fig. 3.3(b). The resistor  $R_1$  in Fig. 3.3(a) is split into two, and no additional current branch is needed. Two output currents ( $I_{\rm B1}$  and  $I_{\rm B2}$ ) can then be obtained with different peak current points. The peak current point of  $I_{\rm B1}$  ( $V_{\rm DC,P1}$ ) is set to be near the lowest  $V_{\rm DC}$ , while the peak current point of  $I_{\rm B2}$  ( $V_{\rm DC,P2}$ ) is set to be near the higher end of the  $V_{\rm DC}$  range.  $I_{\rm B2}$  is used to compensate  $I_{\rm B1}$  at the high end of the  $V_{\rm DC}$  range when it drops significantly. The peak currents of  $I_{\rm B1}$  and  $I_{\rm B2}$  are

$$I_{\text{B1,peak}} = \frac{1}{2} k_{\text{n}} \left( \frac{W}{L} \right)_{2} \left[ \sqrt{\frac{2I_{11}}{k_{\text{n}} (W/L)_{1}}} - I_{11} (R_{1a} + R_{1b}) \right]^{2}$$

(3.5)

$$I_{\text{B2,peak}} = \frac{1}{2} k_{\text{n}} \left( \frac{W}{L} \right)_{3} \left[ \sqrt{\frac{2I_{12}}{k_{\text{n}} (W/L)_{1}}} - I_{12} R_{1a} \right]^{2}.$$

(3.6)

where  $I_{11}$  is the value of  $I_1$  at  $V_{\text{DC,P1}}$ , and  $I_{12}$  is the value of  $I_1$  at  $V_{\text{DC,P2}}$ . Note that the size of  $M_{\text{N3}}$  is the same as  $M_{\text{N1}}$ , while  $(W/L)_2$  is still four times of  $(W/L)_1$ , because  $I_1$  at  $V_{\text{DC,P2}}$  is roughly two times higher than  $I_1$  at  $V_{\text{DC,P1}}$ . With this assignment,  $I_{\text{B2,peak}}$  is about half of  $I_{\text{B1,peak}}$ . The combined bias current  $I_{\text{Bias}} = I_{\text{B1}} + I_{\text{B2}}$  then resembles a QIPV output current.

Simulated and measured results of the proposed QIPV biasing circuit are shown in Fig. 3.4(b). The measured  $I_{B1}$  peaks at around 1.6 V with a current of 2.68  $\mu$ A, and drops to 0.5  $\mu$ A at  $V_{DC} = 4$  V. The measured  $I_{B2}$  peaks at around 2.9 V with a current of 1.53  $\mu$ A. Meanwhile,  $I_{Bias}$  peaks at around 1.7 V with 3.95  $\mu$ A, and drops to 1.97  $\mu$ A at  $V_{DC} = 4$  V. The proposed QIPV circuit can be easily modified to bias an amplifier designed to have a constant (or adaptive) bandwidth, for example, to compensate for the negative effects with decreasing supply voltage.

#### 3.3 Power Transistor Sizing Optimization

NMOS transistors are chosen to implement the active diodes and PMOS transistors the cross-coupled pair for two reasons. First, by using PMOS transistors for the cross-coupled pair, they are driven by the AC input, not the comparator, and their parasitic gate capacitors do not affect the speed and the switching loss of the rectifier, as they are part of the LC resonant tuning capacitor  $C_2$  that do not dissipate power, and the energy is just transferred between the resonant capacitors and the secondary coil  $L_2$ .

Second, the mobility of NMOS transistors is higher, and results in smaller W/L ratios that reduce switching loss. For the trade-off between switching loss and conduction loss,  $W_N$  is set to be 600  $\mu$ m with minimum channel length; on the other hand, W/L of the power PMOS could be large to achieve a small turn-on voltage drop ( $W_P = 4000 \mu$ m). In this design, the turn-on voltage drop of power NMOS  $V_{DSN}$  and PMOS  $|V_{DSP}|$  are set to be ~250 mV and ~70

mV respectively at  $|V_{AC}| = 1.5$  V and  $R_L = 500 \Omega$ . The total voltage drop is only ~320 mV in the worst case, which is much smaller than using passive diodes.

# 3.4 Minimum Operating Voltage

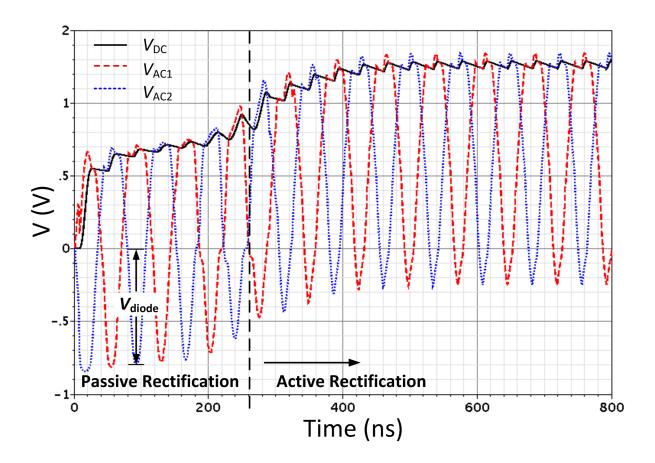

Fig. 3.5 Simulated start-up process of the proposed active rectifier (Rec2).

The lowest input amplitude  $V_{AC,min}$  for our proposed rectifiers to work is determined by the minimum supply voltage of the comparators. The rectified DC voltage should be higher than  $V_{GS} + V_{DSsat}$  for the comparators to work, so  $V_{AC,min}$  is given by

$$V_{\text{AC,min}} = V_{\text{DC,min}} + V_{\text{Drop}} = V_{\text{GS}} + V_{\text{DSsat}} + V_{\text{DSN}} + \left| V_{\text{DSP}} \right|, \tag{3.7}$$

where  $V_{\rm DSN}$  and  $|V_{\rm DSP}|$  are the drain-to-source voltages of the power transistors. However, the lowest input amplitude for start-up is the same as that of using passive diodes, because when the active rectifier is relaxed, the DC output voltage  $V_{\rm DC}$  is 0 and is unable to turn on the power NMOS switches. Instead, as illustrated in Fig. 3.5, parasitic diodes of the power

NMOS switches will be forward-biased when  $V_{\rm AC} > V_{\rm DC}$  during start-up. After the output capacitor is charged up to higher than the minimum supply voltage required by the comparators that are biased by the QIPV current source, the power NMOS switches are then activated, and the active rectifier could then function as designed. Latch-up problem could be avoided by careful layout.

#### 3.5 Simulation and Measurement Results

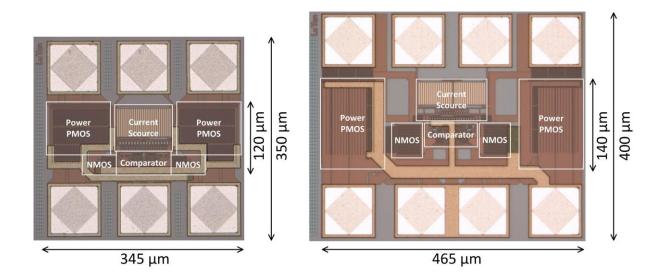

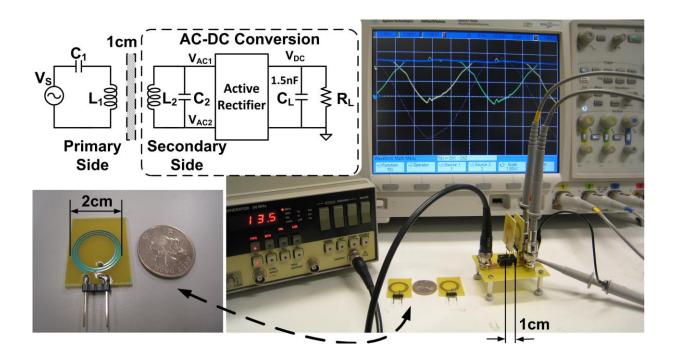

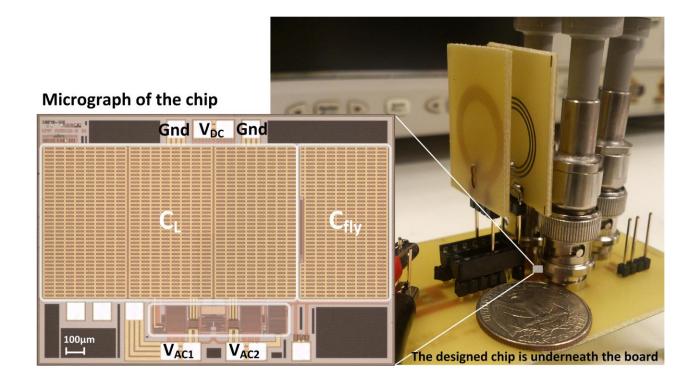

The proposed active rectifiers were designed and fabricated in a 0.35  $\mu m$  CMOS N-well process. Micrographs of the rectifiers are shown in Fig. 3.6. The sizes of these two rectifiers, including the pads, are 0.12 mm<sup>2</sup> and 0.19 mm<sup>2</sup>, respectively; and the active areas are 0.041 mm<sup>2</sup> and 0.065 mm<sup>2</sup>, respectively. The measurement setup is shown in Fig. 3.7, including the identical coupling coils that are etched on single-side printed circuit boards (PCBs). The primary and secondary coils each have 3 turns with inner and outer radii of 0.75 cm and 1 cm respectively, and were separated by 1 cm during measurements. The measured inductance of the coils is 310.4 nH, and the series resistance is 480 m $\Omega$  at 13.56 MHz and 190 m $\Omega$  at DC. The DC output of the rectifier drives a 1.5 nF off-chip filtering capacitor.

Fig. 3.6 Micrographs of Rec1 and Rec2.

Fig. 3.7 Measurement setup for the proposed 13.56 MHz active rectifiers.

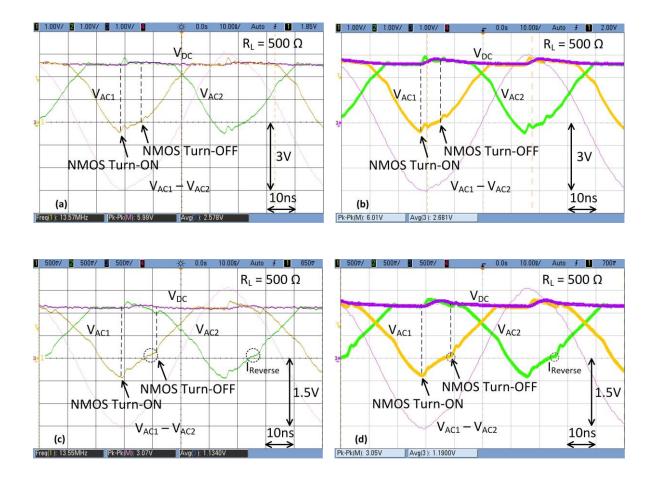

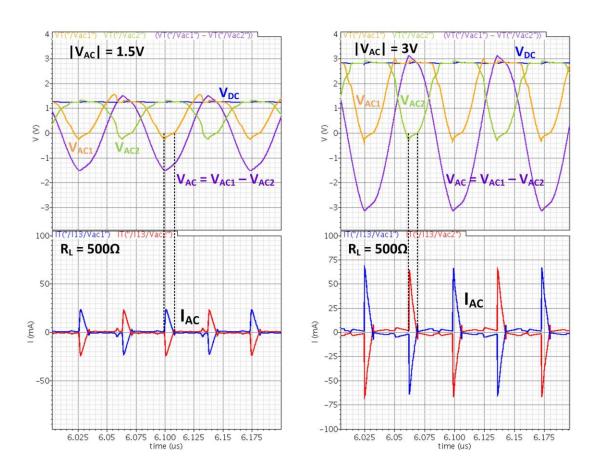

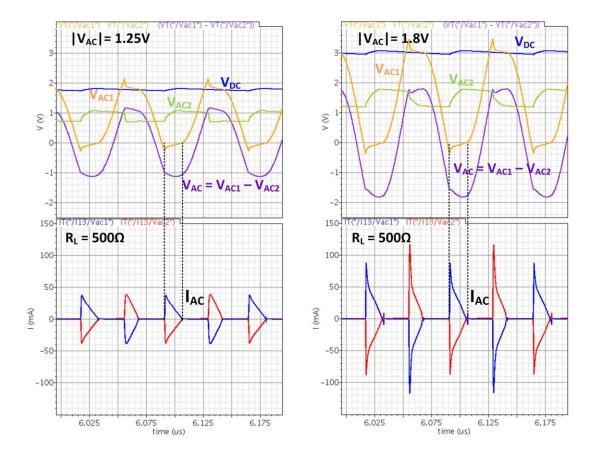

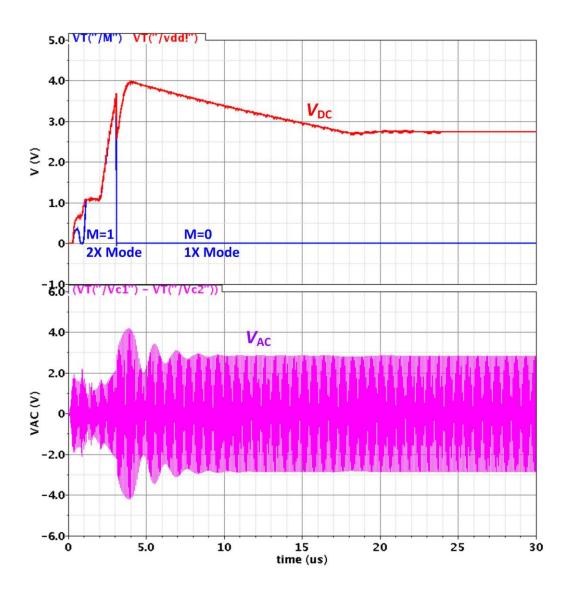

Since the peripheral circuits for measuring the voltage conversion ratio M and the power conversion efficiency PCE are different, two separate PCBs are made and measured accordingly. Fig. 3.8 shows the measured AC input and DC output waveforms of the proposed active rectifiers Rec1 and Rec2, respectively. The peak of  $I_{B1}$  is eventually designed to locate at 1.6 V instead of 1.2 V to reserve adequate margin for keeping the PCE high in the middle and higher range of  $V_{AC}$ . The optimized case is when the input amplitude  $V_{AC}$  is 3 V and  $R_L$  is 500  $\Omega$ . The input voltage ripples across  $V_{AC1}$  and  $V_{AC2}$  are due to large change in load current when turning on and off the power NMOS switches. As can be observed from Fig. 3.8(a) and Fig. 3.8(b), reverse current is well eliminated, which means that the NMOS switch is turned off when its drain voltage is higher than the ground voltage. The worst operating condition for the rectifier is at heavy load and low input amplitude, as shown in Fig. 3.8(c) and Fig. 3.8(d). In this case, a small amount of reverse current is observed due to slower response time of the rectifier at lower supply voltages. Conduction loss of the power transistors increases at heavy load and when the gate overdrive voltage is small at low  $V_{\rm AC}$ . The performance could further be improved if the bias current of the comparator is slightly increased to have a larger offset for faster response.

Fig. 3.8 Measured waveforms of AC inputs and DC output at  $R_L = 500\Omega$  and  $V_{AC} = 3$  V of (a) Rec1 and (b) Rec2; at  $R_L = 500\Omega$  and  $V_{AC} = 1.5$  V of (c) Rec1 and (d) Rec2.

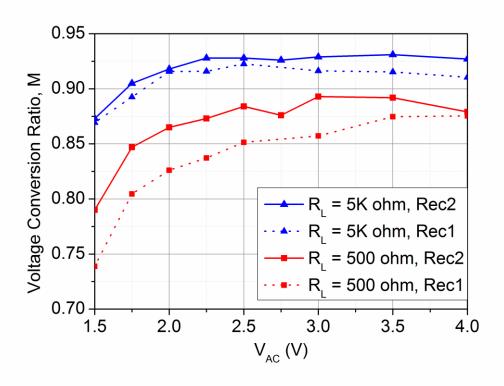

Fig. 3.9 summarized the measured voltage conversion ratios of the rectifiers versus  $V_{\rm AC}$  under different loading conditions ( $R_{\rm L}=500~\Omega$ , and 5 k $\Omega$ ). The peak voltage conversion ratios of Rec1 and Rec2 are 92.3% and 93.1%, respectively, when  $R_{\rm L}=5~{\rm k}\Omega$ . The minimum M of Rec1 and Rec2 are 74% and 79%, respectively, when  $R_{\rm L}=500~\Omega$ .

Fig. 3.9 Measured voltage conversion ratios of Rec1 and Rec2 with different loadings.

The power conversion efficiency PCE of an AC to DC converter is defined as

$$PCE = \frac{P_{\text{OUT}}}{P_{\text{IN}}} = \frac{V_{\text{DD}}^{2} / R_{\text{L}}}{\frac{1}{N \cdot T} \int_{t_{0}}^{t_{0} + N \cdot T} V_{\text{AC}}(t) \cdot I_{\text{AC}}(t) dt},$$

(3.8)

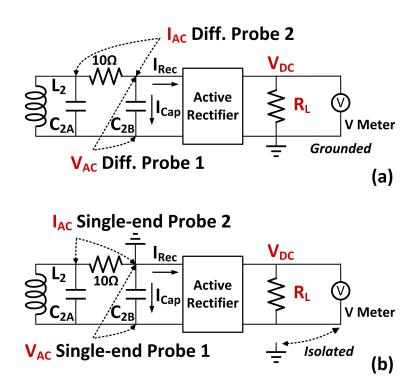

where T is the period of the input sinusoidal wave, and N is the number of cycles that are integrated for  $P_{\rm IN}$  calculation. The main losses are conduction loss, switching loss and comparator static power. For PCE measurement, as shown in Fig. 3.10, a 10  $\Omega$  resistor is inserted in the input path to measure the AC input current  $I_{\rm AC}$ .  $C_{\rm 2B}$  is used to filter the distorted  $V_{\rm AC}$  waveforms caused by the 10  $\Omega$  resistor during large  $\Delta I/\Delta t$  transients. The data of  $V_{\rm AC}$  and  $I_{\rm AC}$  can be collected by two identical differential probes with the setup shown in Fig. 3.10(a); or by two identical single-ended probes as shown in Fig. 3.10(b). In addition, a voltage meter with floating terminals not connected to the ground is needed for the measurement with single-ended probes. Note that according to (3.8), the PCE is not necessarily lower than the voltage conversion ratio at the same loading condition [31], as the highest PCE usually is designed to be at heavy load, while the highest M is always obtained at light load.

Fig. 3.10 The PCB schematics for PCE measurements with (a) differential voltage probes or (b) single-end probes.

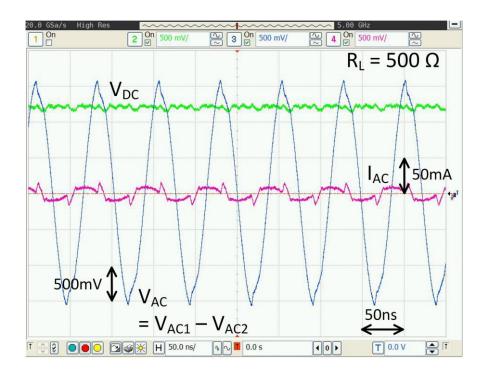

Fig. 3.11 Measured waveforms of  $V_{AC}$ ,  $I_{AC}$  and  $V_{DC}$  for PCE calculation.

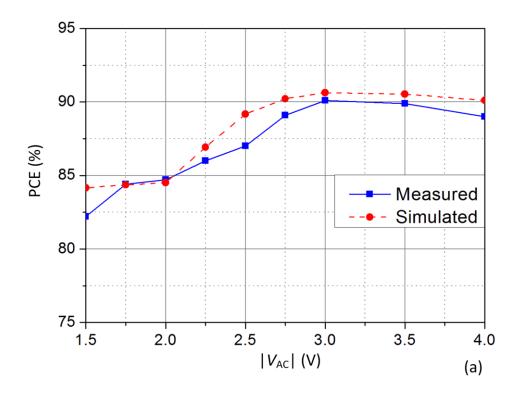

In our experiments, two identical probes with >1 GHz bandwidth are used to measure  $V_{\rm AC}$  and  $I_{\rm AC}$ . About 10,000 points of  $V_{\rm AC}$  and  $I_{\rm AC}$  (6 cycles) were integrated and averaged for  $P_{\rm IN}$  in each PCE calculation. The secondary coil  $L_2$  resonates with  $C_{2A} + C_{2B}$  at 13.56 MHz, with  $C_{2B}/C_{2A} = 0.15$ . As shown in Fig. 3.11, the measured  $I_{AC}$  is the sum of  $I_{Cap}$  that goes through  $C_{2B}$  and  $I_{Rec}$  that goes into the rectifier. To obtain accurate PCE results,  $C_{2B}/C_{2A}$  cannot be large, otherwise, the large  $I_{\text{Cap}}$  of  $C_{2\text{B}}$  that does not dissipate power will affect the accuracy of the relatively small rectifier input current  $I_{Rec}$  that dissipates power. Note also that the scales of the two identical probes should be kept the same to guarantee accuracy. As summarized in Fig. 3.12(a), with  $R_L = 500 \Omega$ , the PCEs of Rec2 were measured to be 82.2% to 90.1% with  $|V_{AC}|$  that varied from 1.5 to 4 V; while in Fig. 3.12(b) the PCEs of 82.3% and 71.2% were measured at  $|V_{AC}| = 3$  V with  $R_L = 100 \Omega$  and 5 k $\Omega$ , respectively. Simulated PCEs are also included for reference: 84.2% to 90.7% were obtained with a load resistor of 500  $\Omega$ , and 82.9% to 81.3% were obtained at  $|V_{AC}| = 3$  V with  $R_L = 100 \Omega$  and 5 k $\Omega$ , respectively. All the above results were measured and simulated at an input frequency of 13.56 MHz. In Fig. 3.12(c), measured and simulated PCEs of Rec2 that operated at the transmission frequencies from 10 to 20 MHz are shown, with  $R_L = 500 \Omega$  and  $|V_{AC}| = 3 \text{ V}$ . The measured PCEs matched quite well with the simulated PCEs at heavy load, and started to deviate from the simulated PCEs at light load of 1 k $\Omega$  since  $I_{Rec}$  became too low to be measured accurately.

Fig. 3.12 Measured and simulated PCEs of the proposed Rec2 operating at 13.56 MHz with (a)  $R_{\rm L} = 500~\Omega$  and (b)  $|V_{\rm AC}| = 3~\rm V$ ; and its frequency response with condition of  $R_{\rm L} = 500~\Omega$  and  $|V_{\rm AC}| = 3~\rm V$ .

Table 3.1 Comparison to the State-of-the-Art Rectifiers

|                         | TCAS-II 06                      | JSSC 09                           | TCAS-I 11                | TCAS-II 12                        | TBCAS 12                          | JSSC 12             | This Work                                  | This Work                       |

|-------------------------|---------------------------------|-----------------------------------|--------------------------|-----------------------------------|-----------------------------------|---------------------|--------------------------------------------|---------------------------------|

|                         | [20]                            | [21]                              | [23]                     | [25]                              | [31]                              | [15]                | Rec1 [22]                                  | Rec2 [26]                       |

| Technology              | 0.35 μm                         | 0.35 μm                           | 0.5 μm                   | 0.18 µm                           | 0.18 μm                           | 0.18 μm             | 0.35 µm                                    | 0.35 µm                         |

| Chip Area               | 0.107 mm <sup>2</sup>           | 1.03 mm <sup>2</sup>              | $0.263 \text{ mm}^2$     | 0.009 mm <sup>2</sup>             | 0.608 mm <sup>2</sup>             | $0.34 \text{ mm}^2$ | 0.12 mm <sup>2</sup>                       | 0.19 mm <sup>2</sup>            |

| Frequency               | 13.56 MHz                       | 1.5 MHz                           | 13.56 MHz                | 13.56 MHz                         | 10 MHz                            | 13.56 MHz           | 13.56 MHz                                  | 13.56 MHz                       |

| Input Amp.              | 1.5 ~ 3.5 V                     | 1.2 ~ 2.4 V                       | 3.3 ~ 5 V                | 0.9 ~ 2 V                         | 0.8 ~ 2.7 V                       | N/A                 | 1.5 ~ 4 V                                  | 1.5 ~ 4 V                       |

| Load Cap.               | 200 pF                          | 1 μF                              | 10 μF                    | 10 μF                             | 200 pF                            | 5.8 μF              | 1.5 nF                                     | 1.5 nF                          |

|                         |                                 | 1.13 ~ 2.28 V                     |                          |                                   |                                   |                     | 1.28V ~ 3.65V                              | 1.28V ~ 3.56V                   |