## Device Technology and Integration for GaN-based Sensors and High-frequency Power Electronics

by

### Xing LU

A Thesis Submitted to

The Hong Kong University of Science and Technology

in Partial Fulfillment of the Requirements for

the Degree of Doctor of Philosophy

in the Department of Electronic and Computer Engineering

January 2015

## **Authorization**

I hereby declare that I am the sole author of the thesis.

I authorize the Hong Kong University of Science and Technology to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize the Hong Kong University of Science and Technology to reproduce the thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Xing LU

January 2015

# Device Technology and Integration for GaN-based Sensors and High-frequency Power Electronics

#### by Xing LU

This is to certify that I have examined the above PhD thesis and have found that it is complete and satisfactory in all respects, and that any and all revisions required by the thesis examination committee have been made.

Prof. Cameron CAMPBELL, Division of SOSC

Thesis Examination Committee Member (Chairman)

Prof. Kei May LAU, Department of ECE

Thesis Examination Committee Member (Thesis Supervisor)

Prof. Patrick C. YUE, Department of ECE

Thesis Examination Committee Member (Thesis Co-supervisor)

Prof. Kevin J. CHEN, Department of ECE

Thesis Examination Committee Member

Prof. Johnny K. O. SIN, Department of ECE

Thesis Examination Committee Member

Prof. Jiannong WANG, Department of PHYS

Thesis Examination Committee Member

Prof. Ross D. MURCH, Department of ECE

Head of Department of Electronic and Computer Engineering

Department of Electronic and Computer Engineering

The Hong Kong University of Science and Technology

January 2015

## Acknowledgements

My PhD study at the Hong Kong University of Science and Technology (HKUST) was certainly one of the most fruitful experiences in my life. I am grateful to many people for their support and help, in one way or another, during the completion of this thesis.

First and foremost, I would like to express my deepest gratitude to my advisor, Prof. Kei May Lau, for her continuous and generous support, guidance and encouragement throughout my whole journey toward a PhD. It would not have been possible for me to complete the research presented in this thesis without her. I greatly appreciate her help in every stage of my PhD study. Moreover, Prof. Lau has provided me a lot of opportunities to attend international conferences and have conversations with the top researchers from all over the world. I believe that I will benefit from what I have learnt from her all through my life, especially her attitude towards research and the way of dealing with people and affairs. Special thanks also go to Prof. Patrick C. Yue, my co-advisor. During the past four years, Prof. Yue has been offering me patient guidance and help, and sharing his insightful comments and suggestions on my research. His profound knowledge on semiconductor devices and circuits, rich experience in industry as well as the great enthusiasm on research and teaching have always inspired me deeply. In addition, I would like to thank Prof. Cameron Campbell, Prof. Kevin J. Chen, Prof. Johnny K. O. Sin, Prof. Jiannong Wang, and Prof. Wai Tung Ng for serving as my thesis examination committee members, and providing invaluable insights for my research and constructive comments for this thesis.

It was my great honor to work with the members of the Photonics Technology Center (PTC) at HKUST. Most of the samples I used in this work were grown by Mr. Jun Ma, my long-term research cooperator who I am indebted to. Jun and I have worked closely for more than three years and we made a great team in developing an *in-situ* SiN<sub>x</sub> gate dielectric. I really enjoyed the time when we did the experiments together and discussed our research. I am especially grateful to Mr. Chi Ming Lee. He guided me in the first fabrication process and characterization of acoustic wave devices. I would also like to thank Dr. Ming Li and Dr.

Haiou Li, who introduced me into the field of HEMTs. Without their help, I could not have learned quickly to start my research. Sincere thanks also go to all the other members of our PTC family: Dr. Zhaojun Liu, Dr. Zhenyu Zhong, Dr. Xinbo Zou, Dr. Xiuju Zhou, Dr. Tongde Huang, Dr. Qiang Li, Dr. Xueliang Zhu, Dr. Kar Wei Ng, Dr. Dongmei Deng, Mr. Chak Wah Tang, Dr. Qian Luo, Miss. Yan Gao, Mr. Ka Ming Wong, Mr. Wing Cheung Chong, Mr. Yunyan Zhang, Miss. Yueyin Zhang, Dr. Peiqiang Xu, Mr. Huaxin Jiang, Mr. Chao Liu, Mrs. Yating Wan, Mr. Yuefei Cai, Mr. Bei Shi, Mr. Tsz Him MAK, Mr. Ka Ho Tam, Mr. Wai Ching Cho, Mr. Yu Han and Mr. Pak San YIP. They were all good friends and very kind in giving a hand when I encountered troubles.

I would like to express my thanks to the staff in the Nanoelectronics Fabrication Facility (NFF) and Materials Characterization and Preparation Facility (MCPF) at HKUST, for keeping the laboratories in good condition and providing training for the equipment. The enormous technical support and valuable discussions from Mr. Yiu Cheong Pun, Mr. Hon Chiu Kwok, Mr. Chun Keung Wong, Mr. Ho Li, Mr. Kwok Chuen Li, Mr. Chun Fai Yeung, Mr. Tze Kin Cheung, Dr. Lutao Weng, Mr. Nick Ho and Mr. Roy Ho are much appreciated. Special thanks are also extended to Mr. Kwok Wai Chan and Mr. Allen F. L. NG, the technical staff in the Wireless Communication Laboratory (WCL) and Device Characterization Laboratory (DCL). They always guided me to set up measurement instruments and provided excellent help in device characterization.

During my study at HKUST, I have been very lucky to make lots of friends from a wide variety of fields, especially Mr. Wei Zhang, Mr. Yu Zhang, Mr. He Li, Dr. Ruoyu Xu, Dr. Wei Zheng, Dr. Yan Zeng, Dr. Sichao Sun, Dr. Shuyun Zhao, Dr. Lining Zhang, Dr. Jing Guo, Dr. Zhiliang Qian, Mr. Bo Wang, Mr. Qihong Chen, Mr. Diandian Li and Mr. Yiyong Feng. For some of them, we had overlaps in research, while for the others we shared common interests and had fun together. Sincere thanks are extended to them for their company, and I will always cherish my friendship with them.

Last but not least, I would like to express my heartfelt gratefulness to my wife, Mrs. Xuelian Wang, my father, Mr. Cunhou Lu, my mother, Mrs. Xuelian Wang, my brother, Mr.

Lei Lu, and other family members. Their endless love and unconditional support are the driving force for me to keep going and pursuing my dream. It is to honor their love that I dedicate this dissertation to them.

## TABLE OF CONTENTS

| TITLE PAGE                                                                                                       | I    |

|------------------------------------------------------------------------------------------------------------------|------|

| AUTHORIZATION PAGE                                                                                               | II   |

| SIGNATURE PAGE                                                                                                   |      |

| ACKNOWLEDGEMENTS                                                                                                 | IV   |

| Table of Contents                                                                                                | VII  |

| LIST OF FIGURES                                                                                                  | IX   |

| LIST OF TABLES                                                                                                   | XIV  |

| Abstract                                                                                                         | XV   |

| CHAPTER 1 INTRODUCTION                                                                                           | 1    |

| 1.1 Background of GaN Technology                                                                                 | 1    |

| 1.2 Fundamentals of GaN-based Acoustic Wave Devices and Al <sub>x</sub> Ga <sub>1-x</sub> N/GaN HEM <sup>3</sup> | Гs 4 |

| 1.2.1 Piezoelectric effects and spontaneous polarization of III-nitrides                                         | 4    |

| 1.2.2 GaN-based acoustic wave devices                                                                            | 5    |

| 1.2.3 Al <sub>x</sub> Ga <sub>1-x</sub> N/GaN-based HEMTs                                                        | 9    |

| 1.3 Contributions and Organization of Thesis                                                                     | 14   |

| CHAPTER 2 LAMB-WAVE SENSORS AND MONOLITHIC INTEGRATED ACOUSTIC OSCILLATORS USING GAN-ON-SI                       |      |

| 2.1 Introduction                                                                                                 | 17   |

| 2.2 Two generations of GaN-based Lamb-wave sensors                                                               | 18   |

| 2.3 Monolithic integrated acoustic wave oscillators                                                              | 24   |

| 2.3.1 Integration consideration                                                                                  | 24   |

| 2.3.2 Delay line oscillator design and fabrication                                                               | 25   |

| 2.3.3 Device characterization and discussion                                                                     | 28   |

| 2.4 Summary                                                                                                      | 36   |

| CHAPTER 3 GATE-LAST SELF-ALIGNED TECHNOLOGY FOR ALGAN/GAN HEMTS                                                  | 37   |

| 3.1 Introduction                                                                                                 | 37   |

| 3.2                          | Device structure and fabrication process                                                                                     | 40           |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------|

| 3.3                          | Device characterization and discussion                                                                                       | 44           |

| 3.4                          | Summary                                                                                                                      | 48           |

| СНАРТ                        | TER 4 MOCVD-GROWN IN-SITU SIN <sub>x</sub> GATE DIELECTRIC FOR ALN/GAN MISHEM                                                | Ts <b>50</b> |

| 4.1                          | Introduction                                                                                                                 | 50           |

| 4.2<br>hete                  | Growth and characterization of <i>in-situ</i> SiN <sub>x</sub> thin film grown on A rostructures                             | -            |

| 4.3<br>struc                 | Investigation of the interfacial trapping effects in in-situ SiN <sub>x</sub> /AIN/Ga<br>ctures grown on sapphire substrates |              |

| 4.4                          | Summary                                                                                                                      | 74           |

| CHAPT<br>SIN <sub>x</sub> /A | TER 5 FABRICATION AND CHARACTERIZATION OF GATE-LAST SELF-ALIGNED LN/GAN MISHEMTS                                             |              |

| 5.1                          | Introduction                                                                                                                 | 76           |

| 5.2                          | Fabrication of the gate-last self-aligned in-situ SiN <sub>x</sub> /AlN/GaN MISHEMTs                                         | 77           |

| 5.3                          | DC and RF characterization at RT                                                                                             | 79           |

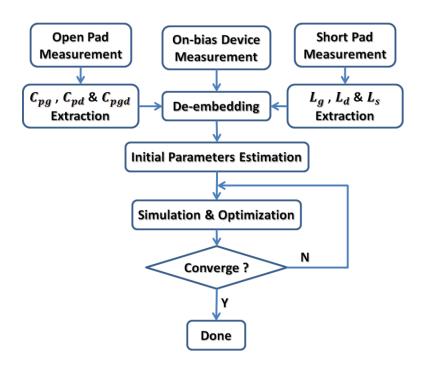

| 5.4                          | Small signal equivalent circuit modeling                                                                                     | 84           |

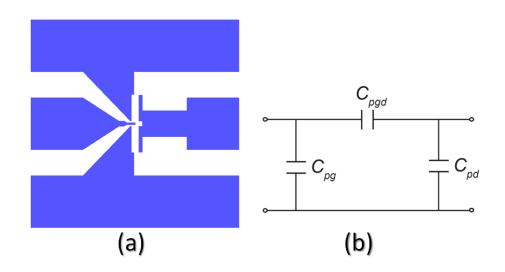

| 5.4                          | 4.1 Extrinsic Parameters Extraction                                                                                          | 86           |

| 5.4                          | 4.2 Intrinsic Parameters Estimation                                                                                          | 89           |

| 5.5                          | Thermal evolution of the device DC and RF performance                                                                        | 91           |

| 5.6                          | Summary                                                                                                                      | 93           |

| СНАРТ                        | TER 6 SUMMARY AND SUGGESTED FUTURE WORK                                                                                      | 94           |

| 6.1                          | Summary of the dissertation                                                                                                  | 94           |

| 6.2                          | Suggestions for future work                                                                                                  | 95           |

| REFERE                       | NCES                                                                                                                         | 97           |

| APPEND                       | DIX                                                                                                                          | 109          |

| A. Pr                        | rocess flow of Gate-last Slef-aligned in-situ SiN <sub>x</sub> /AlN/GaN MISHEMTs                                             | 109          |

| D Du                         | ublication list                                                                                                              | 115          |

## LIST OF FIGURES

| Figure 1.1.1 The applications of GaN-based technology                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.1.2 The material limitations on the <i>JFoM</i> for GaN, InP and Si                                                                                                                                                                                                                                                                                 |

| Figure 1.1.3 The temperature dependence of intrinsic carrier concentration profiles for GaN 6H SiC, GaAs and Si                                                                                                                                                                                                                                              |

| Figure 1.2.1 Crystal structures of Ga-faced and N-faced wurtzite GaN. [1]                                                                                                                                                                                                                                                                                    |

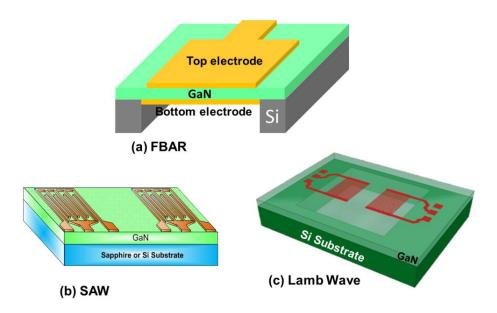

| Figure 1.2.2 GaN-based acoustic wave devices: FBAR (a), SAW (b), FPW (c).                                                                                                                                                                                                                                                                                    |

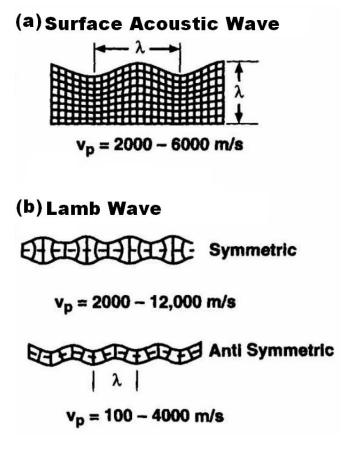

| Figure 1.2.3 Pictoral representations of elastic waves in solids. Motions of groups of atoms ar depicted in these cross-sectional views of plane elastic waves propagating to the right. Vertical and horizontal displacements are exaggerated for clarity. Typical wave speeds, v <sub>p</sub> , are shown below each sketch. (a) SAW. (b) Lamb waves [19]. |

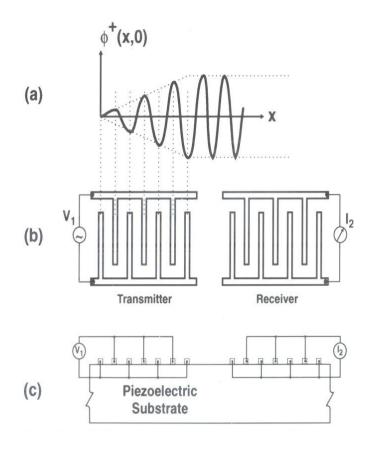

| Figure 1.2.4 IDTs, formed by patterning electrodes on the surface of a piezoelectric substrate of membrane for exciting acoustic waves: (a) wave electrical potential, (b) top view, (c) side view [41].                                                                                                                                                     |

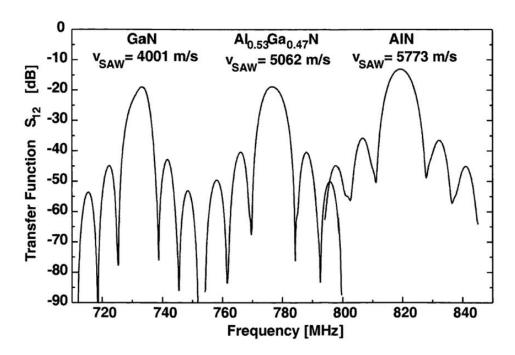

| Figure 1.2.5 The typical transfer function $S_{12}$ -Parameter of SAW devices using $Al_xGa_{1-x}N$ or sapphire substrates (x = 0, x = 0.53 and x = 1). [1]                                                                                                                                                                                                  |

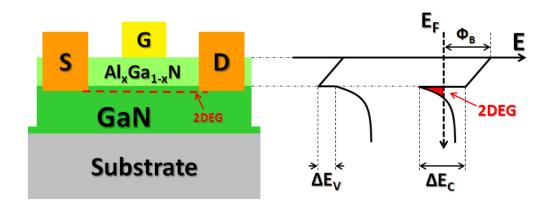

| Figure 1.2.6 The cross-sectional schematic and the energy-band profile of a typica Al <sub>x</sub> Ga <sub>1-x</sub> N/GaN HEMT10                                                                                                                                                                                                                            |

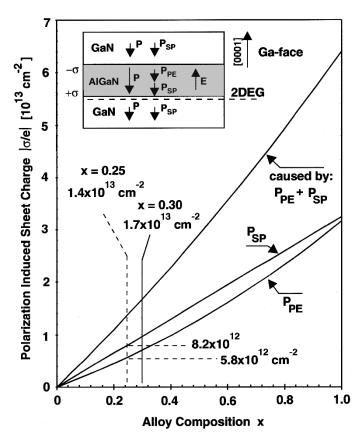

| Figure 1.2.7 The calculated charge density at the Al <sub>x</sub> Ga <sub>1-x</sub> N/GaN interface plotted versus th alloy composition [15]                                                                                                                                                                                                                 |

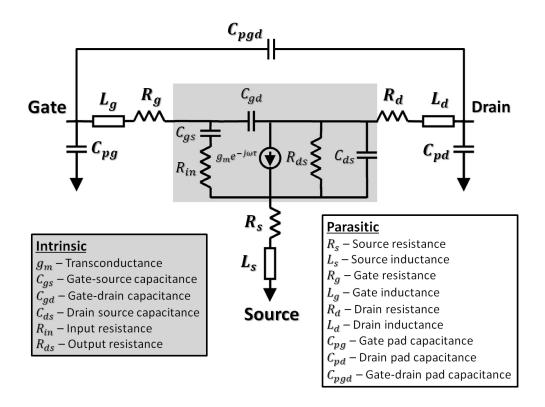

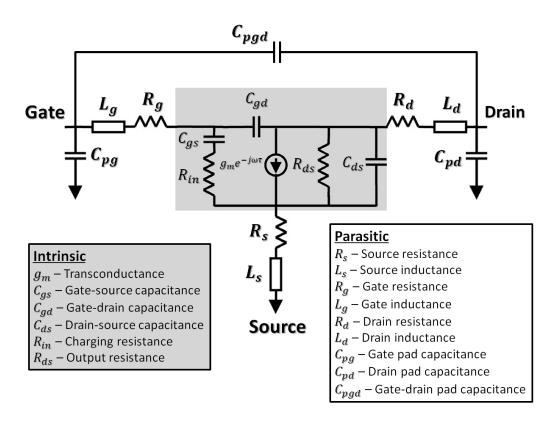

| Figure 1.2.8 The 15-element small signal equivalent circuit model for a HEMT [43]                                                                                                                                                                                                                                                                            |

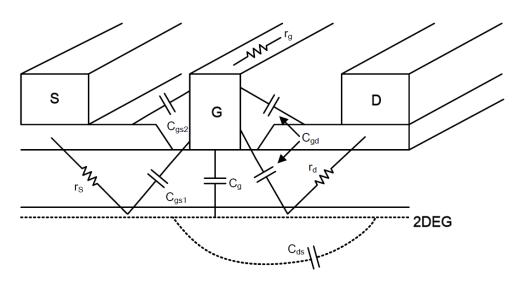

| Figure 1.2.9 The physical origins of the elements in an equivalent circuit model [44]                                                                                                                                                                                                                                                                        |

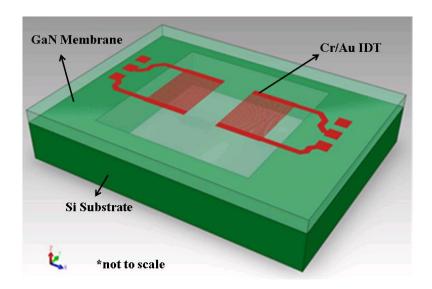

| Figure 2.2.1 The schematic of the Lamb-wave sensor using a GaN-on-Si structure                                                                                                                                                                                                                                                                               |

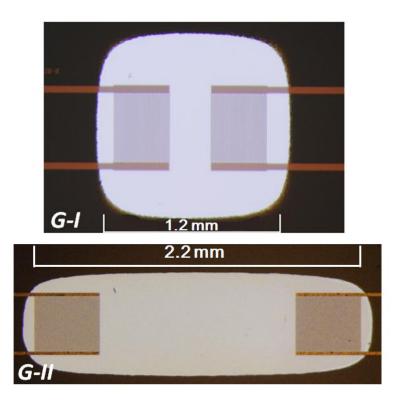

| Figure 2.2.2 The optical micrographs of the fabricated <i>G-I</i> and <i>G-II</i> sensors                                                                                                                                                                                                                                                                    |

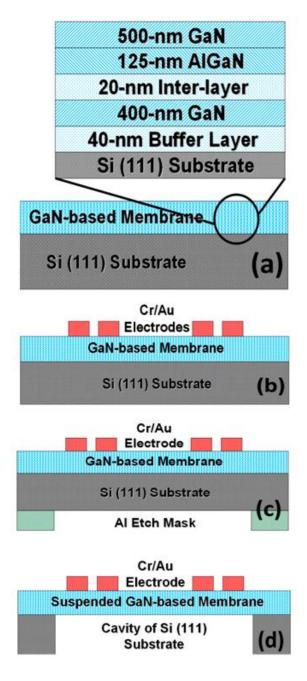

| Figure 2.2.3 The fabrication process of the Lamb-wave sensors                                                                                                                                                                                                                                                                                                |

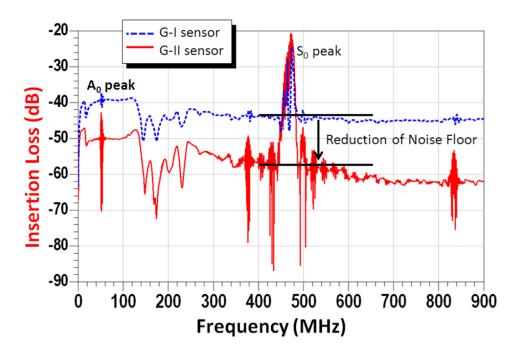

| Figure 2.2.4 The magnitude of the $S_{21}$ Parameter of the unloaded $G$ - $I$ and $G$ - $II$ sensors 2.                                                                                                                                                                                                                                                     |

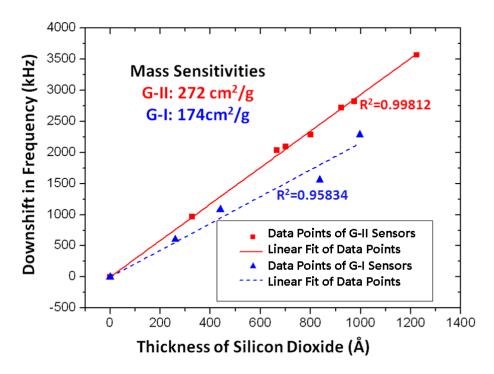

| Figure 2.2.5 The linear relationships of the frequency versus the thicknesses of deposited SiO for the <i>G-I</i> and <i>G-II</i> sensors.                                                                                                                                                                                                                   |

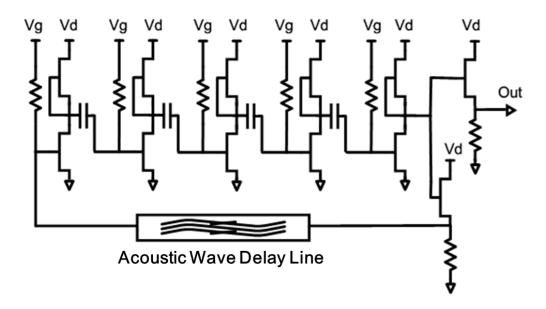

| Figure 2.3.1 The schematic of the integrated oscillator circuit.                                                                                                                                                                                                                                                                                             |

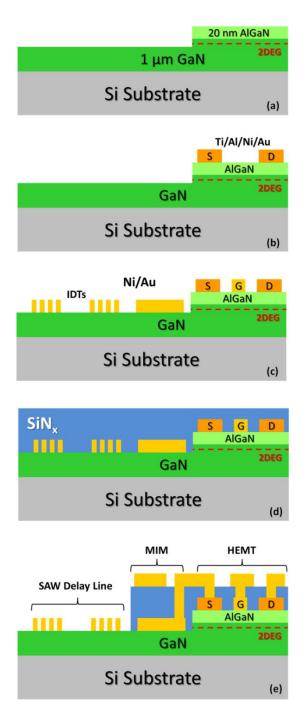

| Figure 2.3.2 The fabrication process of the integrated SAW oscillator                                                                                                                                                                                                                                                                                        |

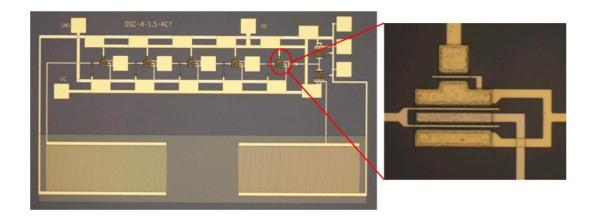

| Figure 2.3.3 The optical micrograph of a fabricated SAW oscillator                                                                                                                                                                                                                                                                                           |

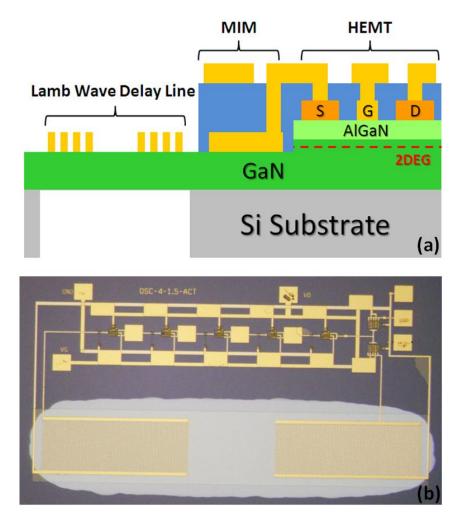

| Figure 2.3.4 The cross-sectional schematic (a) and the optical micrograph (b) camb-wave oscillator.                                                                                                |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.3.5 The magnitude of the $S_{21}$ Parameter of the SAW delay line device                                                                                                                  | 29 |

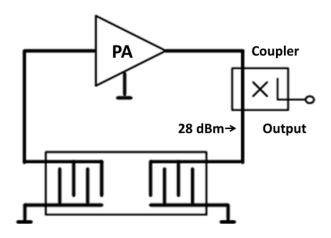

| Figure 2.3.6 The schematic showing the power handling test setup.                                                                                                                                  | 30 |

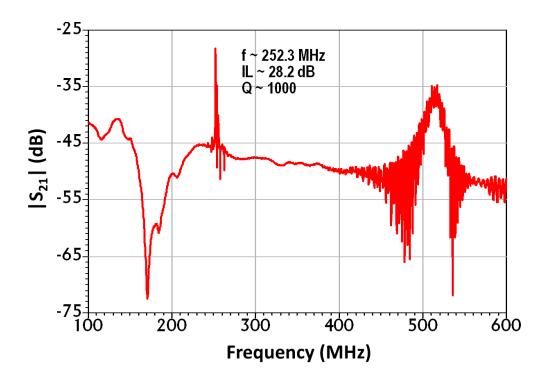

| Figure 2.3.7 The magnitude of the S <sub>21</sub> Parameter of a Lamb-wave delay line device                                                                                                       | 30 |

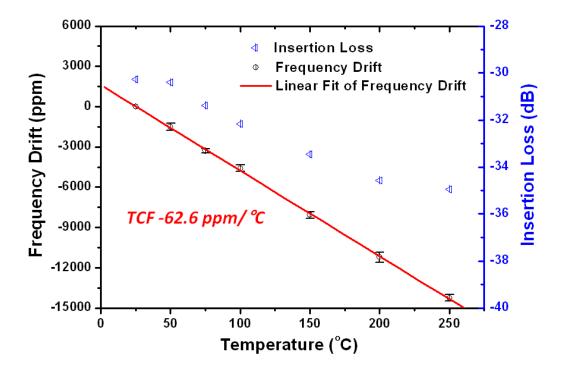

| Figure 2.3.8 The temperature dependence of the $A_0$ wave peak frequency and insertion the peak frequency.                                                                                         |    |

| Figure 2.3.9 The DC characteristics of a fabricated AlGaN/GaN HEMT                                                                                                                                 | 32 |

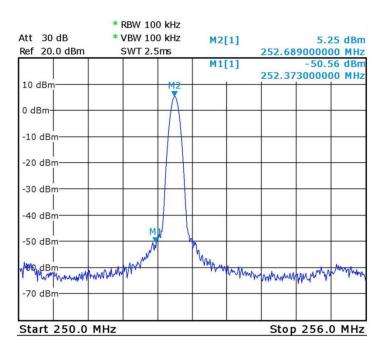

| Figure 2.3.10 The measured frequency spectrum of the integrated SAW oscillator opera                                                                                                               | •  |

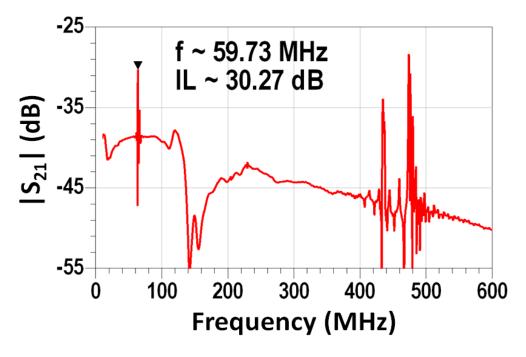

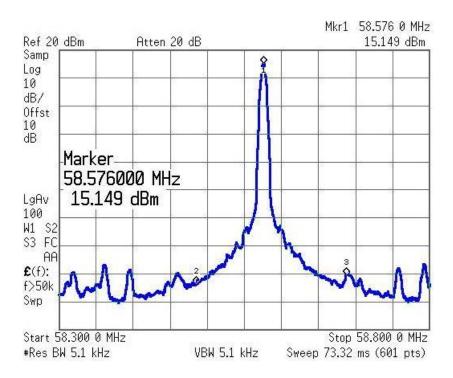

| Figure 2.3.11 The measured frequency spectrum of the integrated Lamb-wave oscoperating at RT.                                                                                                      |    |

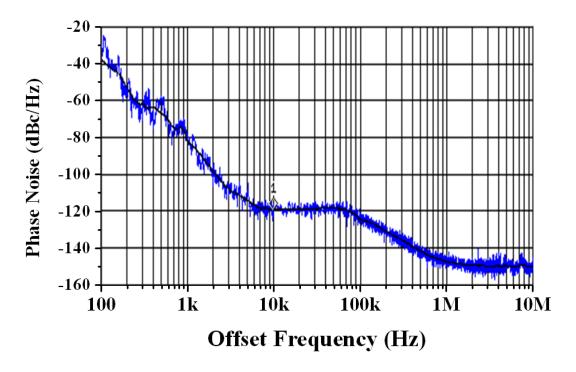

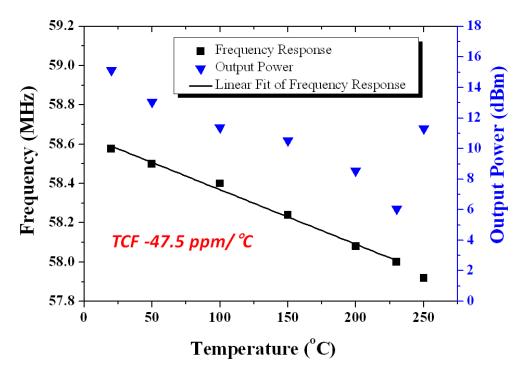

| Figure 2.3.12 The measured phase noise of the integrated Lamb-wave oscillator operating                                                                                                            |    |

| Figure 2.3.13 The temperature dependence of the oscillation frequency and output power Lamb-wave oscillator.                                                                                       |    |

| Figure 3.1.1 The cross-sectional schematic of the S/D regrowth structure                                                                                                                           | 38 |

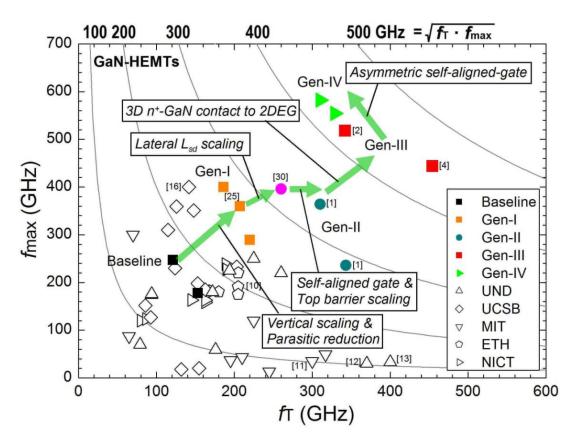

| Figure 3.1.2 Summary of the RF performances for stat-of-the-art GaN HEMTs in the lite [64].                                                                                                        |    |

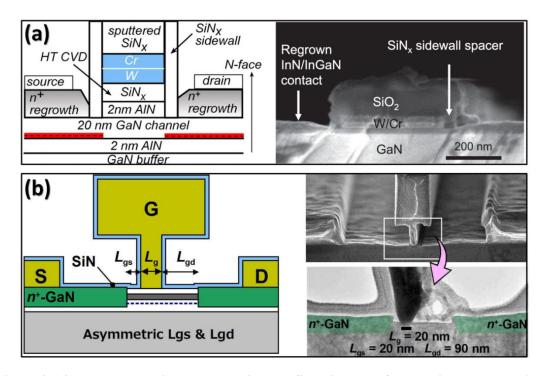

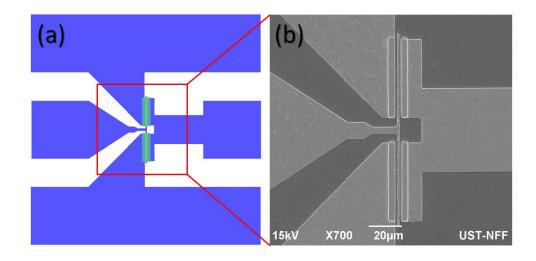

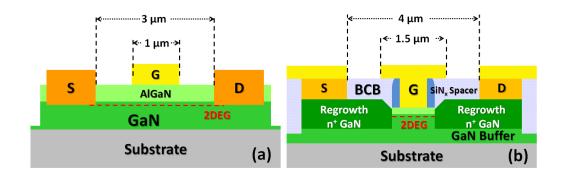

| Figure 3.1.3 The cross-sectional schematics and SEM images of the device structures literature: gate-first self-aligned process (a) [70] and T-gate process (b) [64]                               |    |

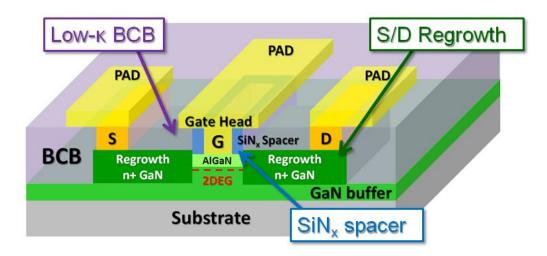

| Figure 3.2.1 The self-aligned gate-last AlGaN/GaN HEMT architecture                                                                                                                                | 40 |

| Figure 3.2.2 The fabrication process of the gate-last self-aligned AlGaN/GaN HEMTs                                                                                                                 | 42 |

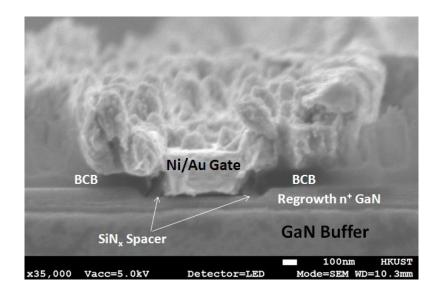

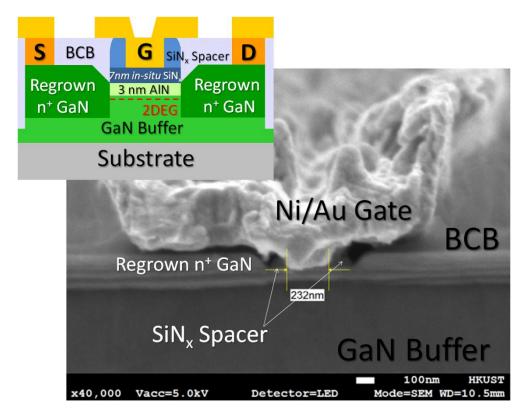

| Figure 3.2.3 The cross-sectional SEM image of a fabricated device.                                                                                                                                 | 43 |

| Figure 3.2.4 The device layout (a) and a top-view SEM image of the gate region (b)                                                                                                                 | 43 |

| Figure 3.2.5 The cross-sectional schematics of the conventional HEMT (a) and gaself-aligned HEMT (b).                                                                                              |    |

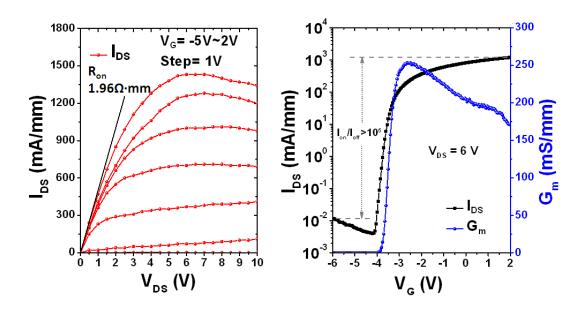

| Figure 3.3.1 The DC output and transfer characteristics of the gate-last self-aligned HEM $L_G = 0.35~\mu m$ and $W_G = 2 \times 50~\mu m$ .                                                       |    |

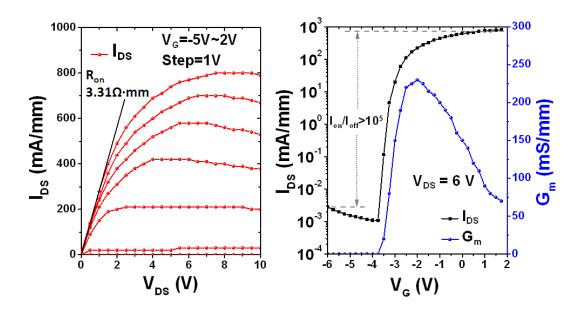

| Figure 3.3.2 The DC output and transfer characteristics of the conventional HEMT with $\mu m$ and $W_G = 2 \times 50 \mu m$ .                                                                      |    |

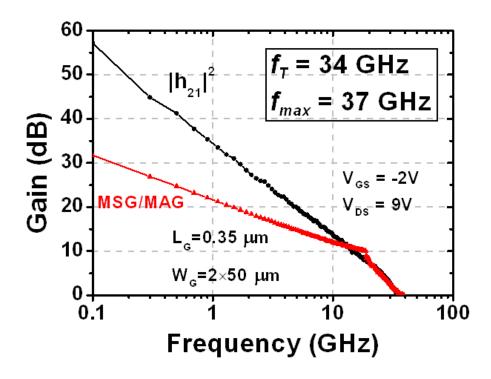

| Figure 3.3.3 The Small signal RF characteristics of the gate-last self-aligned HEMT wit 0.35 $\mu$ m and $W_G = 2 \times 50 \mu$ m showing peak $f_T$ and $f_{max}$ of 34 and 37 GHz, respectively | _  |

|                                                                                                                                                                                                    |    |

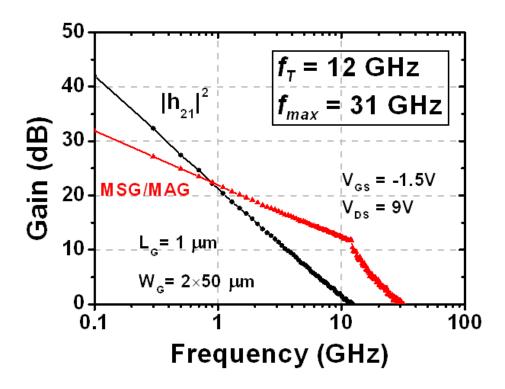

| Figure 3.3.4 The Small signal RF characteristics of the conventional HEMT with $L_G = 1 \mu m$ and $W_G = 2 \times 50 \mu m$ showing peak $f_T$ and $f_{max}$ of 12 and 31 GHz, respectively                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

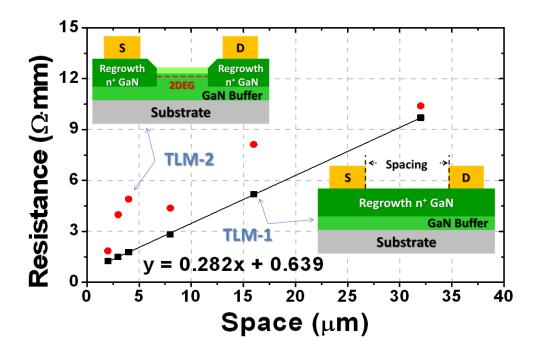

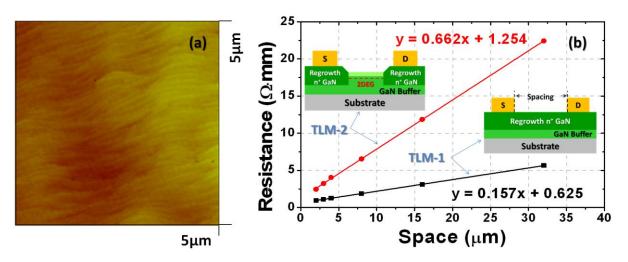

| Figure 3.3.5 The results of the two TLM patterns                                                                                                                                                                                                                                                                      |

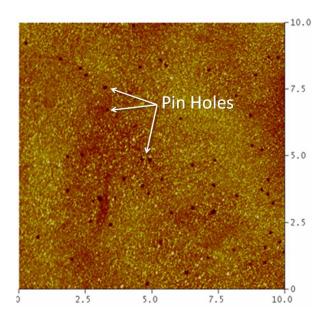

| Figure 3.3.6 AFM image of the regrown $n^{\text{+}}\text{-}GaN$ across a scanned area of 10 $\mu m \times$ 10 $\mu m \ldots$ 48                                                                                                                                                                                       |

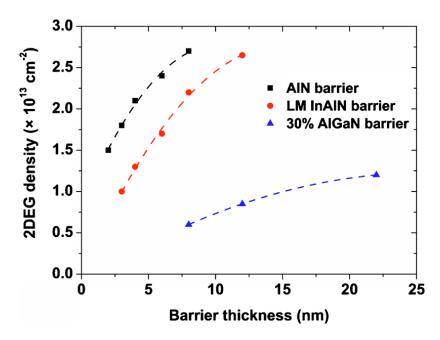

| Figure 4.1.1 The 2DEG carrier densities of $SiN_x/AlN/GaN$ , lattice matched $In_{0.17}Al_{0.83}N/GaN$ , and $Al_{0.3}Ga_{0.7}N/GaN$ heterostructures as a function of the barrier layer thickness [83]                                                                                                               |

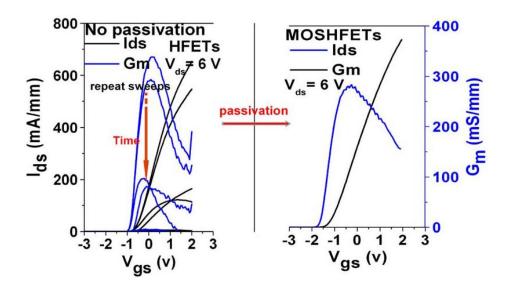

| Figure 4.1.2 The drain current degradation phenomenon of an unpassivated AlN/GaN HEMTs [85].                                                                                                                                                                                                                          |

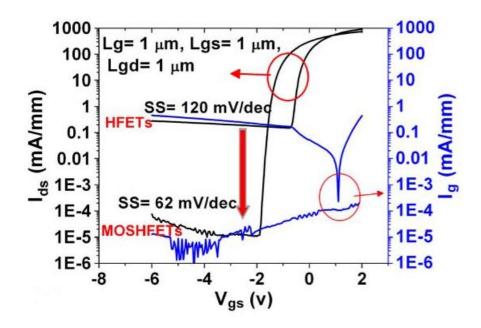

| Figure 4.1.3 The gate leakage currents of the AlN/GaN HEMT and MOSHEMT with a barrier thickness of 3 nm [85]                                                                                                                                                                                                          |

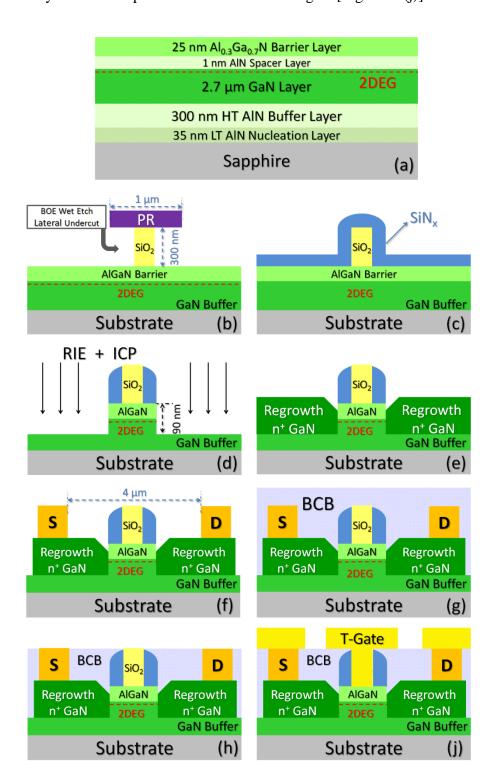

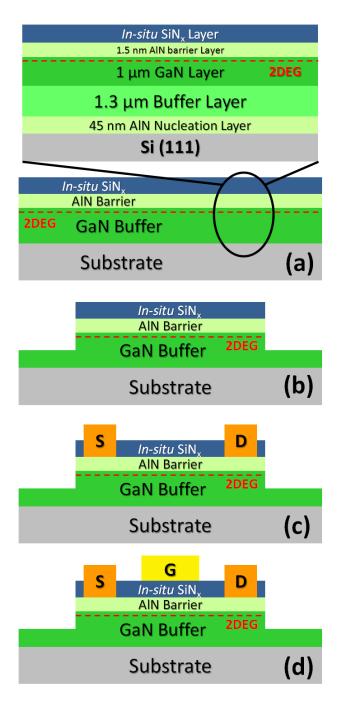

| Figure 4.2.1 The fabrication process of the <i>in-situ</i> SiN <sub>x</sub> /AlN/GaN MISHEMTs55                                                                                                                                                                                                                       |

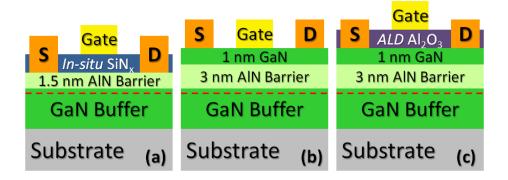

| Figure 4.2.2 The cross-sectional schematics of the $in\text{-}situ$ SiN <sub>x</sub> /AlN/GaN MISHEMT (a), the GaN/AlN/GaN HEMT (b), and the Al <sub>2</sub> O <sub>3</sub> /GaN/AlN/GaN MOSHEMT (c)                                                                                                                  |

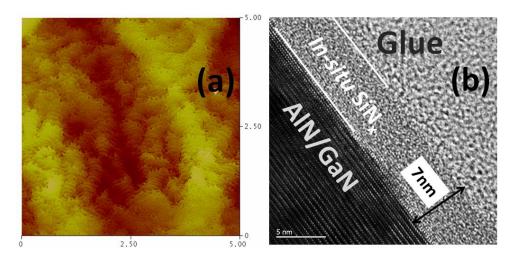

| Figure 4.2.3 The AFM (a) and TEM (b) images of the 7 nm <i>in-situ</i> SiN <sub>x</sub> film deposited on an AlN/GaN heterostructure by MOCVD.                                                                                                                                                                        |

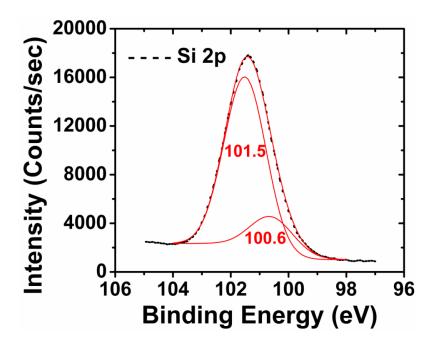

| Figure 4.2.4 The XPS results of Si2p core-level spectra of the <i>in situ</i> SiN <sub>x</sub> thin film deposited by MOCVD.                                                                                                                                                                                          |

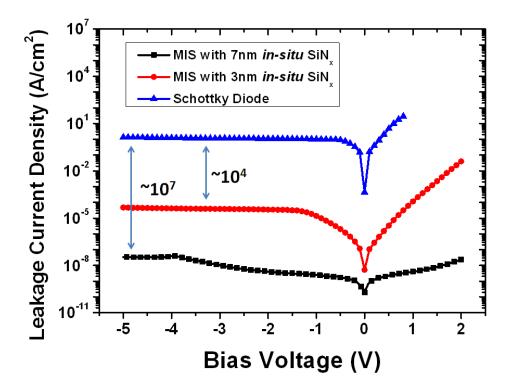

| Figure 4.2.5 The leakage currents of a GaN/AlN/GaN Schottky diode with a 3 nm AlN barrier and two 1.5-nm-barrier MIS diodes with 3 nm and 7 nm $in$ - $situ$ SiN <sub>x</sub>                                                                                                                                         |

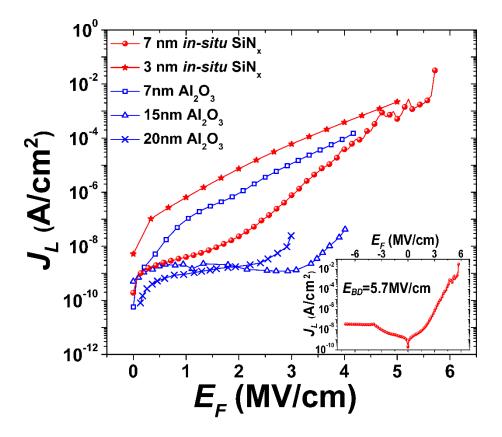

| Figure 4.2.6 The leakage current density $(J_L)$ versus electric field $(E_F)$ plots for the <i>in-situ</i> SiN <sub>x</sub> MIS diodes and the Al <sub>2</sub> O <sub>3</sub> MOS diodes biased in the accumulation region. The inset shows the breakdown field $(E_{BD})$ of 7 nm <i>in-situ</i> SiN <sub>x</sub> . |

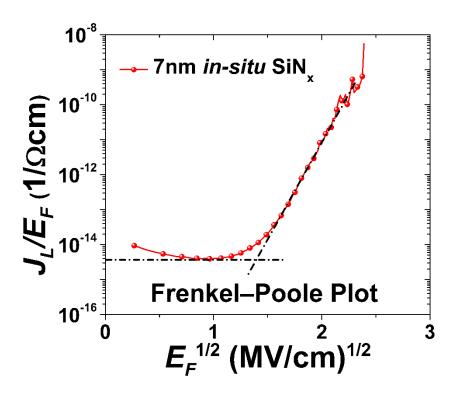

| Figure 4.2.7 The Frenkel-Poole plot for the MIS diodes with 7 nm <i>in-situ</i> SiN <sub>x</sub>                                                                                                                                                                                                                      |

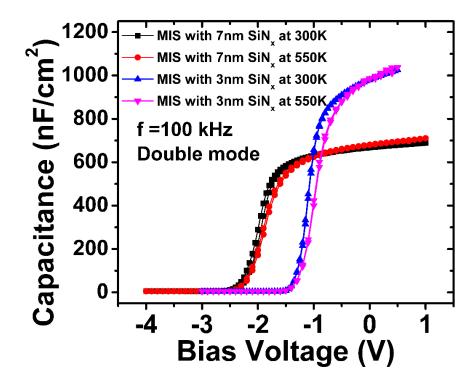

| Figure 4.2.8 The double mode <i>C-V</i> characteristics of the <i>in-situ</i> SiN <sub>x</sub> /AlN/GaN MIS diodes at two different temperatures                                                                                                                                                                      |

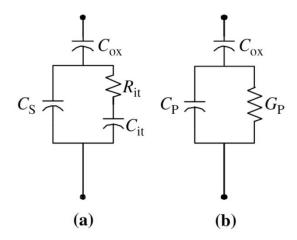

| Figure 4.2.9 Equivalent circuits for conductance measurements: (a) MIS capacitor with an interface trap time constant $\tau_T = C_{it} \cdot R_{it}$ , (b) simplified circuit of (a) [113]61                                                                                                                          |

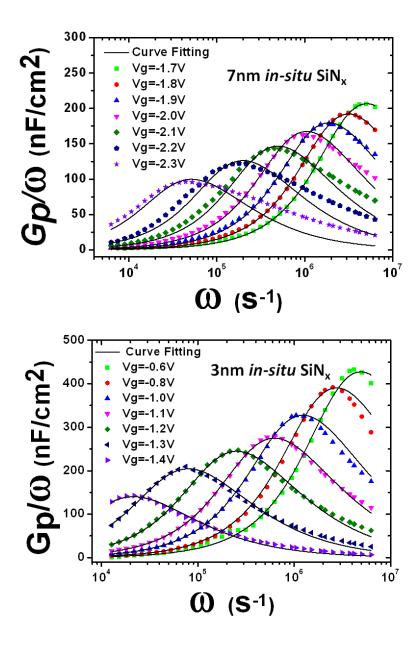

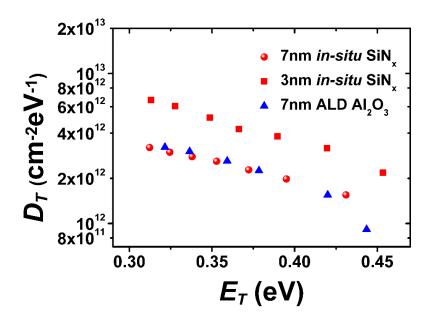

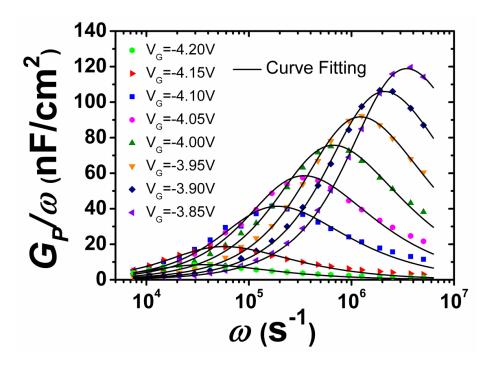

| Figure 4.2.10 The frequency dependent parallel conductance as a function of radial frequency for the MIS diodes with 7 nm and 3 nm $in  situ  SiN_x$ biased with selected gate voltages near $V_{th}$                                                                                                                 |

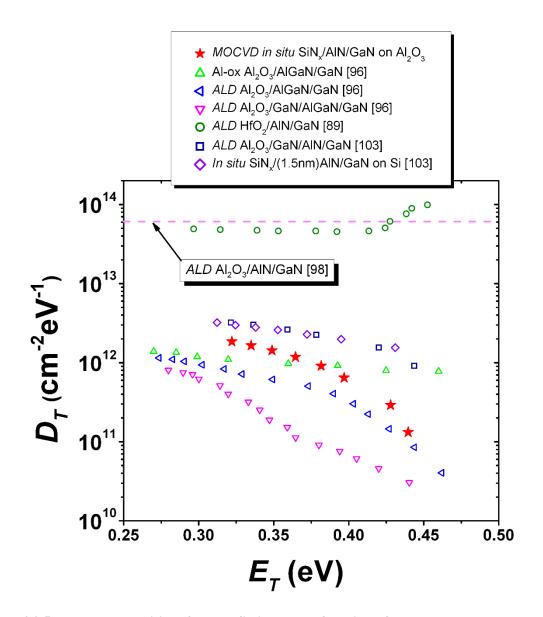

| Figure 4.2.11 The trap state density as a function of their energy level depth below the conduction band for the MIS and MOS diodes                                                                                                                                                                                   |

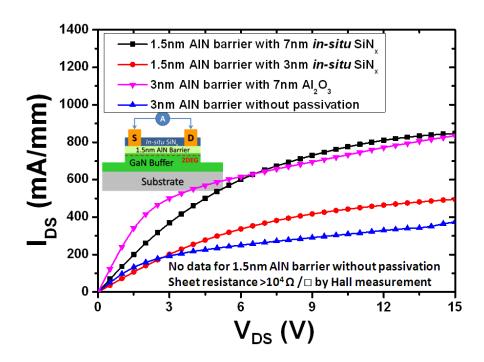

| Figure 4.2.12 The <i>I–V</i> characteristics between the source and drain terminals. The inset shows the measured schematic with 3 um source-drain spacing                                                                                                                                                            |

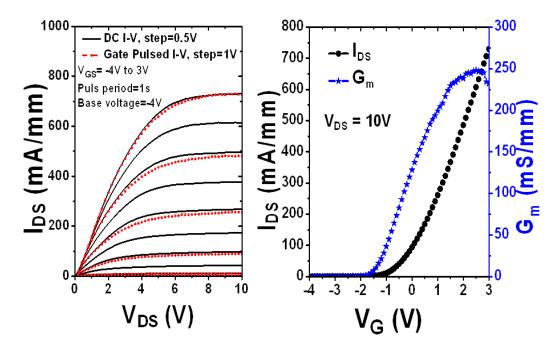

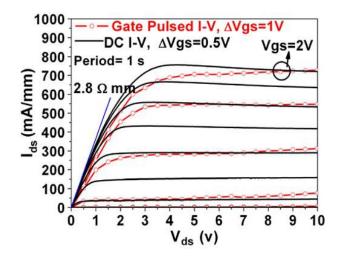

| Figure 4.2.13 The gate-pulsed/DC output (left) and transfer (right) characteristics of a 7 nm in-situ SiN <sub>x</sub> /AlN/GaN MISHEMT with $L_G = L_{GS} = L_{GD} = 1$ µm             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.2.14 The gate-pulsed/DC output characteristics of a Al <sub>2</sub> O <sub>3</sub> (7 nm)/GaN(1 nm)/AlN (3 nm)/GaN MOSHEMT with $L_G = L_{GS} = L_{GD} = 1$ µm [85]            |

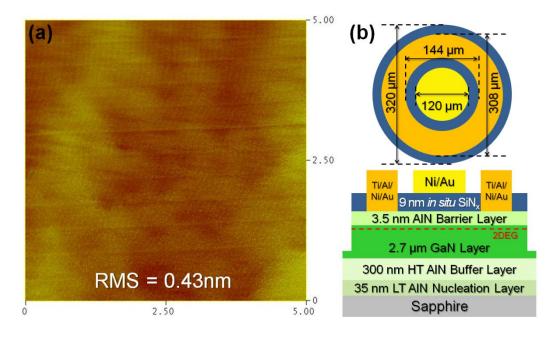

| Figure 4.3.1 (a) The AFM image of the as-grown $in\text{-}situ$ SiN <sub>x</sub> /AlN/GaN MISHEMT sample. (b) The architecture of the MIS diode                                         |

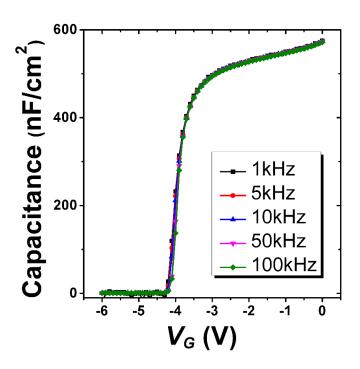

| Figure 4.3.2 The multiple frequency $C-V$ characteristics of the $in\text{-}situ$ SiN <sub>x</sub> /AlN/GaN MIS diode                                                                   |

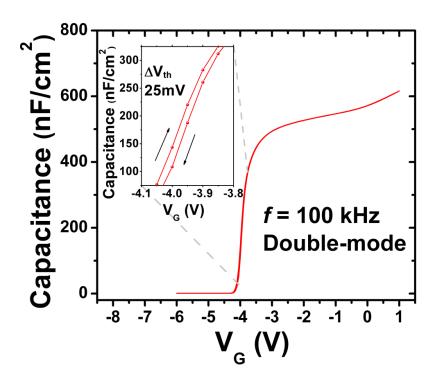

| Figure 4.3.3 Double mode $C$ - $V$ characteristics of the $in$ - $situ$ SiN <sub>x</sub> /AlN/GaN MIS diode. The inset gives the enlarged plot showing the hysteresis                   |

| Figure 4.3.4 Frequency dependent parallel conductance as a function of radial frequency for the MIS diode biased at selected gate voltages near $V_{th}$                                |

| Figure 4.3.5 Trap state densities of the MIS diodes as a function of the energy level depth below the conduction band                                                                   |

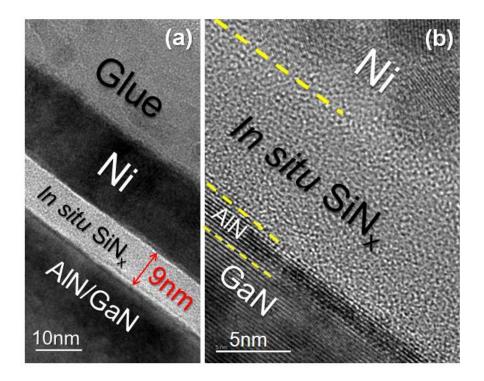

| Figure 4.3.6 Cross-sectional TEM images of the gate stack showing the $in\text{-}situ\ SiN_x/AlN/GaN$ architecture.                                                                     |

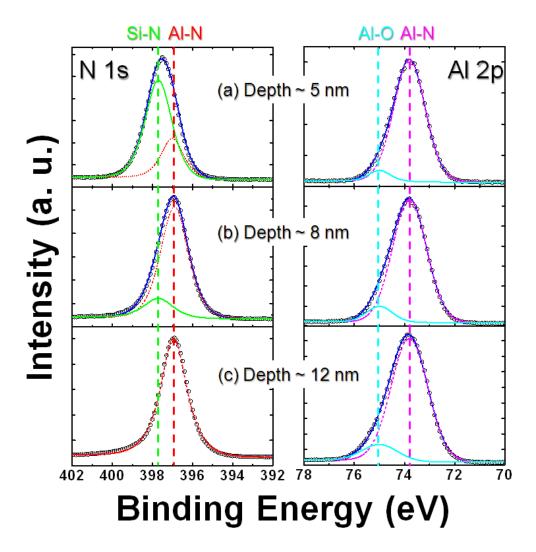

| Figure 4.3.7 The N 1s and Al 2p core-level XPS spectra at three different depths from the surface                                                                                       |

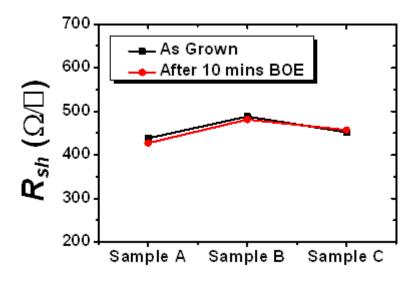

| Figure 5.2.1 The $R_{sh}$ of three $in\text{-}situ\ SiN_x/AlN/GaN\ MISHEMT}$ samples before and after 10 minutes BOE immersion                                                          |

| Figure 5.2.2 The cross-sectional SEM image of the gate region for a 0.23 µm gated MISHEMT. The inset shows the device architecture                                                      |

| Figure 5.2.3 The AFM image (a) and TLM results (b) of the regrown n <sup>+</sup> -GaN S/D79                                                                                             |

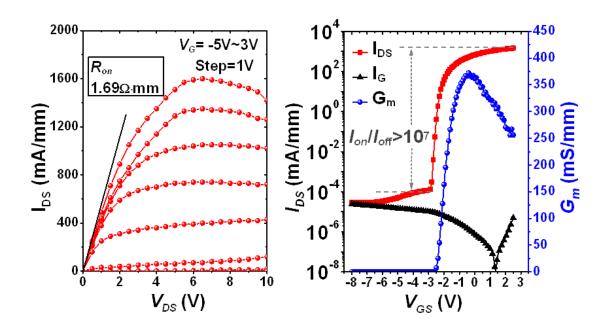

| Figure 5.3.1 DC output and transfer characteristics of the MISHEMT with $L_G = 0.23~\mu m$ and $W_G = 2 \times 50~\mu m$ .                                                              |

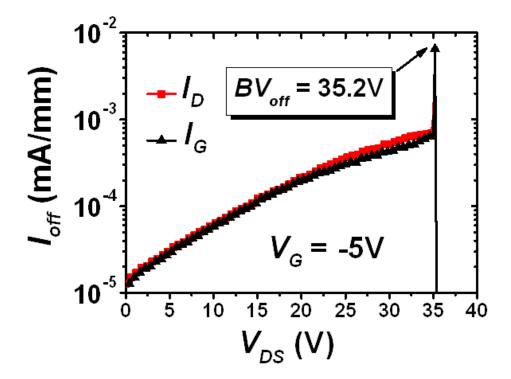

| Figure 5.3.2 The three-terminal off-state breakdown characteristics of a gate-last self-aligned MISHEMT at $V_{GS} = -5 \text{ V}$                                                      |

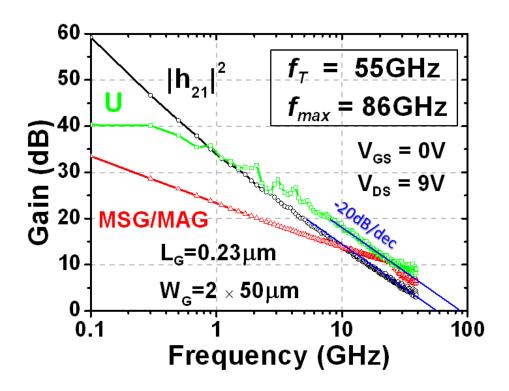

| Figure 5.3.3 Small signal RF characteristics of the MISHEMT with $L_G$ = 0.23 $\mu$ m and $W_G$ = 2 $\times$ 50 $\mu$ m showing peak $f_T$ and $f_{max}$ of 55 and 86 GHz, respectively |

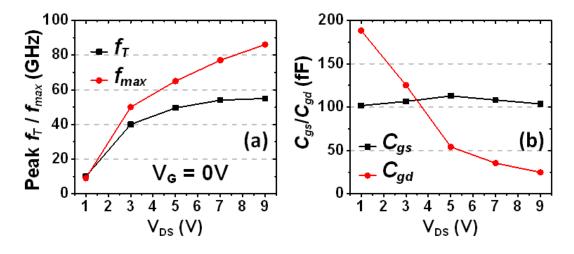

| Figure 5.3.4 The peak $f_T$ , $f_{max}$ (a) and $C_{gs}$ , $C_{gd}$ (b) as a function of $V_{DS}$ for the MISHEMT with $L_G$ = 0.23 $\mu$ m and $W_G$ = 2 $\times$ 50 $\mu$ m.          |

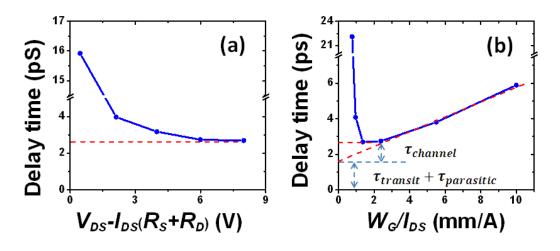

| Figure 5.3.5 The delay time as a function of voltage across the channel (a) and the delay time as a function of reciprocal drain current density (b)                                    |

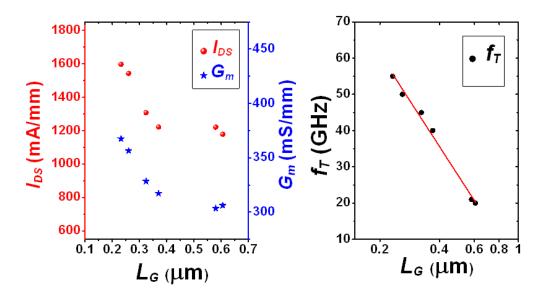

| Figure 5.3.6 Scaling behavior of $I_{DS}$ , $G_m$ and $f_T$ with respect to $L_G$ for the gate-last self-aligned                                                                        |

| MISHEMTs                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.4.1 The 15-element small signal equivalent circuit model                                                                                                                                                   |

| Figure 5.4.2 The flowchart shows the approach of small signal equivalent circuit modeling. 85                                                                                                                       |

| Figure 5.4.3 (a) Open pad structure and (b) its $\pi$ -network equivalent circuit                                                                                                                                   |

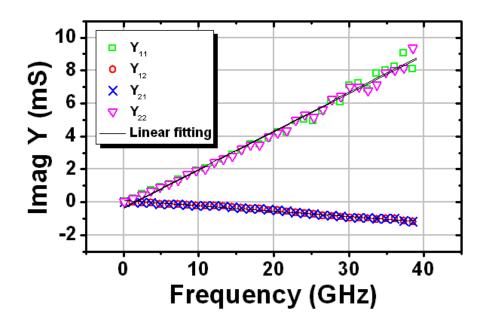

| Figure 5.4.4 Imaginary part of the measured Y-parameter data of the open pad structure 87                                                                                                                           |

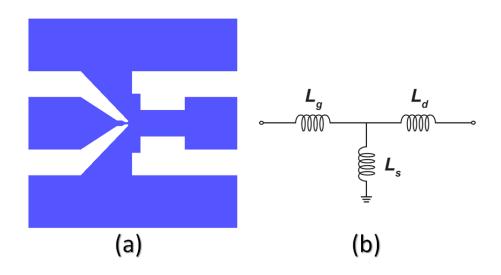

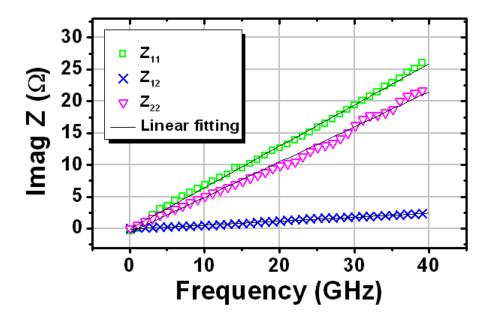

| Figure 5.4.5 Short pad structure and (b) its T-network equivalent circuit                                                                                                                                           |

| Figure 5.4.6 Imaginary part of the measured Z-parameter data of the short pad structure 88                                                                                                                          |

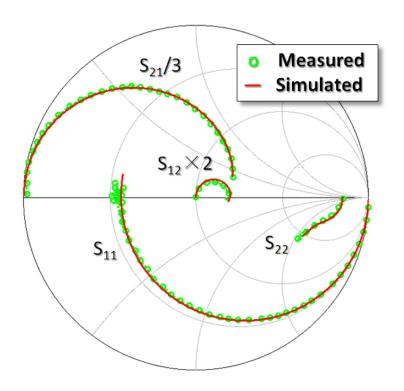

| Figure 5.4.7 Smith chart shows the simulated and measured S-parameters of the 0.23 µm gated in-situ SiN <sub>x</sub> /AlN/GaN MISHEMT                                                                               |

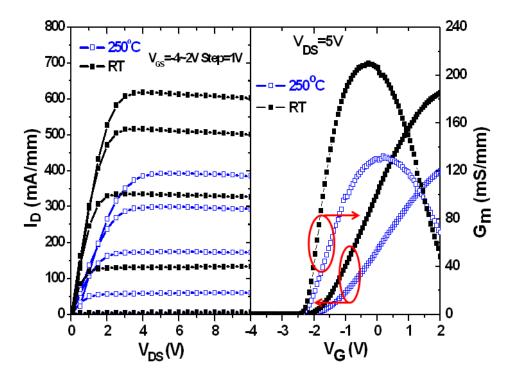

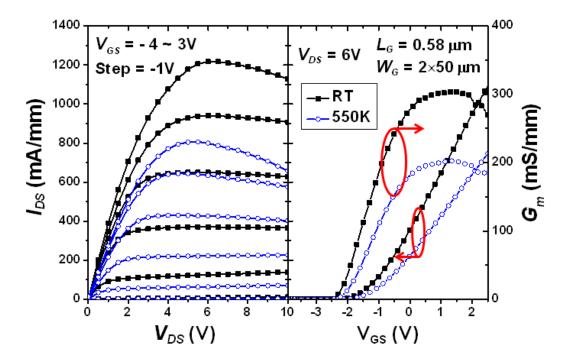

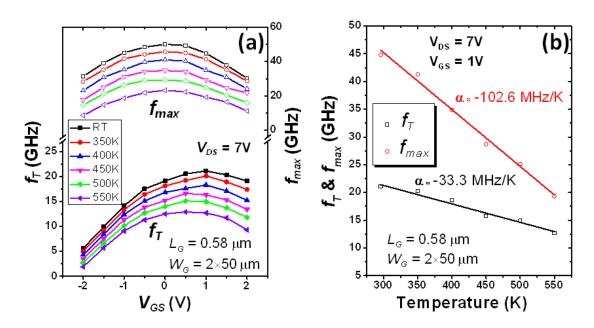

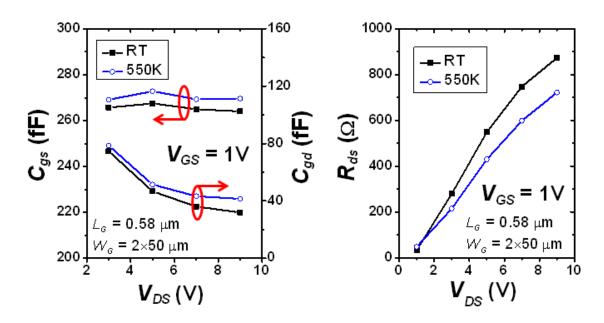

| Figure 5.5.1 DC output and transfer characteristics of the MISHEMT with $L_G = 0.58$ µm and $W_G = 2 \times 50$ µm at RT and 550 K                                                                                  |

| Figure 5.5.2 (a) The thermal evolution of $f_T$ and $f_{max}$ as a function of $V_{GS}$ at $V_{DS} = 7$ V. (b) The dependence of $f_T$ and $f_{max}$ on the ambient temperature at $V_{GS} = 1$ V at $V_{DS} = 7$ V |

| Figure 5.5.3 The thermal dependence of $C_{gs}$ , $C_{gd}$ and $R_{ds}$ as a function of $V_{DS}$                                                                                                                   |

## LIST OF TABLES

| Table 1-1 Properties of four competing materials in semiconductor platforms                                                     | 2    |

|---------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2-1 The design parameters of <i>G-II</i> and <i>G-II</i> sensors.                                                         | 19   |

| Table 5-1 The small signal equivalent circuit model elements of the in-situ SiN <sub>x</sub> /AlN/                              | 'GaN |

| MISHEMT ( $L_G = 0.23 \mu \text{m}$ and $W_G = 2 \times 50 \mu \text{m}$ ) at $V_{GS} = 0 \text{ V}$ and $V_{DS} = 9 \text{ V}$ | 90   |

## Device Technology and Integration for GaN-based Sensors and High-frequency Power Electronics

#### by Xing LU

Department of Electronic and Computer Engineering The Hong Kong University of Science and Technology

#### **Abstract**

Wide bandgap gallium nitride (GaN) and related compounds possess superior material properties, including high electron saturation velocity, large breakdown electric field, and sustainability at high operating temperatures. Because of strong spontaneous and piezoelectric polarization effects, GaN-based heterostructures forming a two-dimensional electron gas (2DEG) channel with large sheet carrier concentration and high electron mobility are ideal for high-frequency power electronics. In addition to other characteristics such as high acoustic velocity, high mechanical and thermal stability and inherent chemical inertness, GaN has also been considered as an attractive thin film piezoelectric material for fabrication of on-chip acoustic wave devices. This dissertation aims at the exploration of GaN-based device technologies and their integration for applications in novel sensors and high-frequency power electronics.

In this thesis, monolithic integration technology of acoustic wave devices with high electron mobility transistors (HEMTs) on AlGaN/GaN heterostructures has been demonstrated. High performance Lamb-wave sensors were designed and fabricated using a GaN-on-Si platform. Then two on-chip oscillators were implemented by monolithically integrating a Lamb-wave or a surface acoustic wave (SAW) delay line device with AlGaN/GaN HEMT circuitries. The monolithic oscillators in this work, which are suitable for sensor systems operating at high ambient temperature, could potentially be extended to high-frequency power applications.

A scalable gate-last self-aligned technology was developed for fabrication of GaN-based metal-insulator-semiconductor high electron mobility transistors (MISHEMTs). Source/drain (S/D) regrowth and low-k benzocyclobutene (BCB) planarization techniques were employed to reduce the access resistance and parasitic capacitance, minimizing the RC-related delay. Thin AlN barriers and *in-situ* grown SiN<sub>x</sub> gate dielectrics by metal-organic chemical vapor deposition (MOCVD) were incorporated to facilitate the device scaling, with increased gate control capabilities, maintaining high channel conductivity and suppressing the gate leakage. The fabricated gate-last self-aligned *in-situ* SiN<sub>x</sub>/AlN/GaN MISHEMTs exhibited high performance, demonstrating great potential for the next-generation RF/microwave power applications.

#### CHAPTER 1 Introduction

#### 1.1 Background of GaN Technology

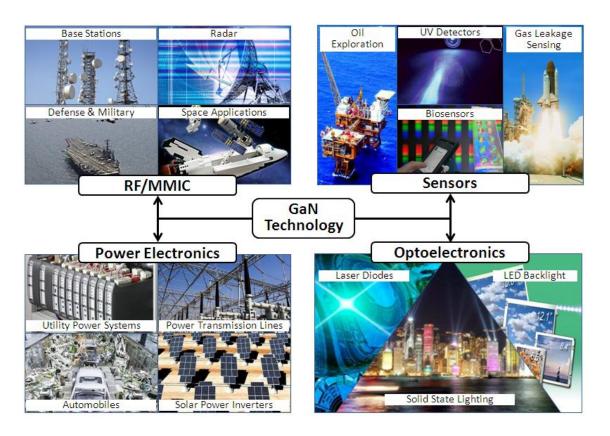

Gallium Nitride (GaN) and its alloy compounds have been considered as a promising material system for semiconductor device applications since the 1960s, from the initial breakthroughs with blue/ultraviolet (UV) light emitting diodes (LEDs) to laser diodes (LDs), UV detectors to radio frequency (RF)/microwave power electronics and then to sensors [1]. Fig 1.1.1 illustrates the wide scope of applications where GaN-based technology can be applied.

Figure 1.1.1 The applications of GaN-based technology

GaN-based LEDs and LDs have already been commercialized for a variety of lighting, display and data storage applications, which benefit from the direct and wide bandgap nature of III-nitrides, as well as the achievement of p-type conduction in GaN [2]. Featuring superior material properties, such as wide bandgap, high electron saturation velocity, and high critical

breakdown field, GaN attracts lots of attention in high speed and high power electronics intended for radar, satellite, wireless base stations, automobiles and utility grid applications. In addition, GaN-based semiconductors offer other advantageous properties, including high mechanical and thermal stability, inherent chemical inertness, strong piezoelectric effect and high acoustic velocity, making them good candidates for acoustoelectronic devices, especially sensors operating in harsh environments such as for gas leakage detection at high ambient temperature.

Table 1-1 lists the material properties of GaN and other competing materials [3-9]. Compared to conventional compounds and silicon semiconductors, GaN exhibits much better figures for most of the specifications, including a wide bandgap of 3.4 eV, a large critical breakdown field of 3.3 MV/cm, a high electron saturation velocity of  $2.5 \times 10^7$  cm/s, a good thermal conductivity up to 1.5 W/ cm K and a relatively strong piezoelectric property. All these excellent and unique properties enable GaN-based devices to be a potential game changer for many key applications, especially high frequency, high power and high temperature electronics.

Table 1-1 Properties of four competing materials in semiconductor platforms.

| Properties                                 | Si   | GaAs | SiC  | GaN                        |

|--------------------------------------------|------|------|------|----------------------------|

| Bandgap<br>(eV)                            | 1.1  | 1.4  | 3.2  | 3.4                        |

| Electron Mobility (cm²/V s)                | 1350 | 8500 | 700  | 1200 (bulk)<br>2000 (2DEG) |

| Saturation Velocity (10 <sup>7</sup> cm/s) | 1.0  | 1.3  | 2.0  | 2.5                        |

| Breakdown Field<br>(MV/cm)                 | 0.3  | 0.4  | 3.0  | 3.3                        |

| Thermal Conductivity (W/cm K)              | 1.5  | 0.5  | 4.5  | 1.5                        |

| Piezoelectric Property                     |      | Weak | Weak | Strong                     |

High-quality single crystalline GaN-based heterostructures have been successfully grown on sapphire, SiC and Si substrates to fabricate high electron mobility transistors (HEMTs)

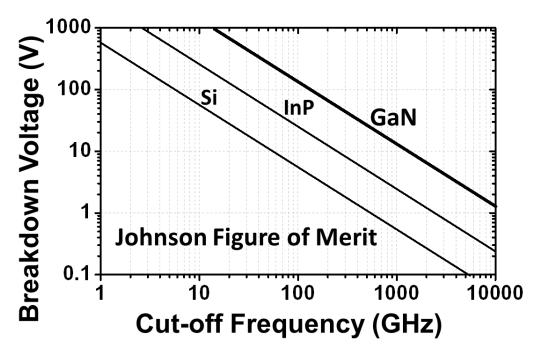

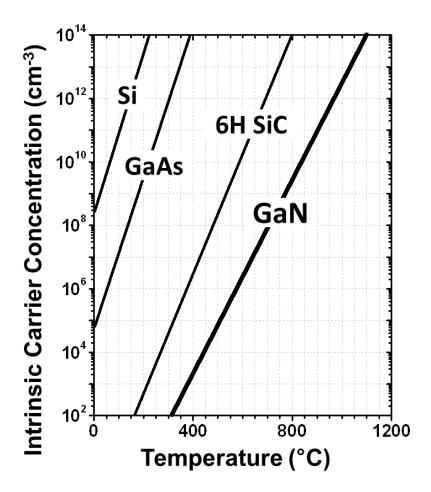

since 1993, when the first AlGaN/GaN HEMT was demonstrated [10]. During the past two decades, intensive research has been done and significant progress has been made to boost GaN HEMTs' performance, in terms of the device operation speed and the current and voltage drive capabilities [11, 12]. Fig 1.1.2 compares the material limitations on the Johnson Figure of Merit (JFoM) for Si, InP and GaN [13]. The JFoM, a common benchmarking for high-frequency high-power transistors, is determined by the product of the cut-off frequency ( $f_T$ ) and off-state breakdown voltage ( $BV_{off}$ ). With much higher electron saturation velocity and a larger breakdown field, GaN produces about a 4 times and 20 times higher JFoM than InP and Si, respectively, indicating the great potential of GaN-based HEMTs for RF/microwave power applications. High temperature operation is also important for electronics because it can reduce the burden of thermal management. Fig 1.1.3 compares the intrinsic carrier density as a function of temperature between Si, GaAs, SiC and GaN [14]. GaN-based devices, inherently featuring smaller intrinsic carrier concentration, can deliver the excellent capability of operating at high temperatures at which mainstream Si and GaAs-based devices stop functioning.

Figure 1.1.2 The material limitations on the JFoM for GaN, InP and Si.

Figure 1.1.3 The temperature dependence of intrinsic carrier concentration profiles for GaN, 6H SiC, GaAs and Si.

#### 1.2 Fundamentals of GaN-based Acoustic Wave Devices and Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN HEMTs

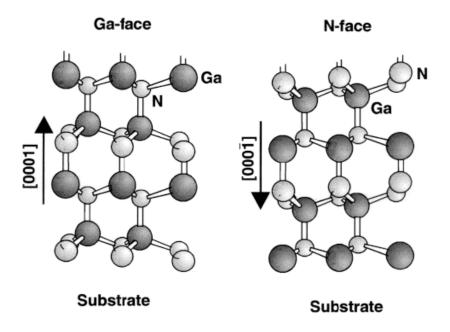

#### 1.2.1 Piezoelectric effects and spontaneous polarization of III-nitrides

The crystal structure of III-nitride epitaxial layers is wurtzite, where the most common growth direction is normal to the (0001) basal plan and the bilayers consist of two closely spaced hexagonal layers [1, 15]. One of the layers is formed by cations and the other by anions, leading to polar faces. In the case of GaN, a basal surface should be either a Ga- or N-face, as shown in Fig 1.2.1. Almost all metal-organic chemical vapor deposition (MOCVD) grown nitrides are Ga-faced, while those grown in a molecular beam epitaxial (MBE) system are usually N-faced.

Figure 1.2.1 Crystal structures of Ga-faced and N-faced wurtzite GaN. [1]

The noncentrosymmetric III-nitride crystals lead to a strong ionicity and a residual electrical polarity of the semiconductors along the (0001) axis; therefore, both strong piezoelectric effects and spontaneous polarizations can be observed [9, 16]. The piezoelectric properties of GaN and AlN are much larger than those in conventional III-V compounds and SiC. In addition, the spontaneous polarization of III-nitrides along the (0001) axis is also very large and leads to strong electric fields up to 3 MV/cm. In this case, the piezoelectric and spontaneous polarization can have a significant influence on the electrical and optical properties of devices. This is because the induced electric fields can influence the shape of the band edges and the carrier distribution inside III-nitride heterostructures, and consequently influence the radiative recombination in light-emitting devices as well as the electrical properties of transistor structures [1, 15-18].

#### 1.2.2 GaN-based acoustic wave devices

Acoustic wave devices based on piezoelectric materials, which allow transduction of electric and acoustic energies, have been constructed in a number of configurations for sensing and communication applications [19, 20]. The medium used to generate acoustic waves in the acoustic wave devices is generally a sputtered polycrystalline material with a

piezoelectric property, mainly AlN, ZnO, and lead zirconate titanate (PZT) [21-29]. We believe the choice of material can be extended to crystalline GaN, a wide bandgap semiconductor currently being exploited in the fabrication of LEDs and HEMTs. The piezoelectric property of GaN is modest when compared to standard piezoelectric ceramics such as PZT that possess hundreds of times higher piezoelectric constants. However, single crystalline GaN can be epitaxially grown, thus giving a very smooth surface and excellent control of layer quality, properties and thickness across the wafer. In addition, GaN offers the benefits of high acoustic velocity, high chemical, mechanical, and thermal stability, as well as monolithic integration with microelectronic systems on the basis of the same material. Hence, GaN has been considered as an attractive thin film piezoelectric material for fabrication of on-chip acoustic wave devices [6, 30, 31]. A distinction can be made depending on how the acoustic wave propagates through the piezoelectric GaN layers: Film Bulk Acoustic-wave Resonators (FBARs) [32-34], Surface Acoustic Wave (SAW) devices [35-37] and Lamb-wave, also known as Flexural Plate Wave (FPW), devices [38, 39], as shown in Fig 1.2.2.

Figure 1.2.2 GaN-based acoustic wave devices: FBAR (a), SAW (b), FPW (c).

The waves that can propagate in a solid depends upon both the properties of the solid and its boundaries [19]. Fig 1.2.3 shows schematically the waves that propagate in a semi-infinite solid having a single plane boundary and in a solid plate that has two plane boundaries. The

SAW is an elastic wave traveling along the surface of a solid, with an amplitude that typically decays exponentially with depth into the substrate, as shown in Fig 1.2.3 (a). The Lamb waves propagate in a solid plate, whose particle motion lies in the plane that contains the direction of wave propagation and the direction perpendicular to the plate, as shown in Fig 1.2.3 (b). Both SAW and Lamb waves are constrained by the elastic properties of the material surfaces that guide them.

Figure 1.2.3 Pictoral representations of elastic waves in solids. Motions of groups of atoms are depicted in these cross-sectional views of plane elastic waves propagating to the right. Vertical and horizontal displacements are exaggerated for clarity. Typical wave speeds,  $v_p$ , are shown below each sketch. (a) SAW. (b) Lamb waves [19].

An interdigitated transducer (IDT) is the most convenient configuration to generate or detect SAW and Lamb waves in the settings of an acoustic wave delay line device. A delay line device consists of two IDTs on two ends of a piezoelectric substrate or membrane, serving as a transmitter or receiver. Each IDT has an array of periodic interlocking comb-shaped finger electrodes, as shown in Fig 1.2.4. [5, 19, 40, 41].

Figure 1.2.4 IDTs, formed by patterning electrodes on the surface of a piezoelectric substrate or membrane for exciting acoustic waves: (a) wave electrical potential, (b) top view, (c) side view [41].

When an alternating voltage is applied to the transmitter IDT, a periodic strain field is generated in the piezoelectric material because of the piezoelectric effect, and standing acoustic waves are produced. These standing waves will result in the propagation of waves launched away from the transmitter to the receiver. Propagation of a mechanical wave in a piezoelectric medium is accompanied by an associated wave potential (Ø). When the wave is incident on a receiving IDT, the piezoelectric effect generates an electrical response that can be detected. For typical delay line acoustic wave devices, the transmitter IDT is the same as the receiver IDT so that a reciprocity relation holds. A network analyzer can be used to measure the transfer function of this set-up.

The acoustoelectric conversion is the most efficient when the acoustic wave wavelength  $(\lambda)$  matches the IDT periodicity, where the coherent waves contributed by each electrode pair superimpose and reinforce, and constructive interference occurs. The effect of reinforcement

increases with the number of pairs of finger electrodes. The frequency of maximum wave excitation, i.e. peak amplitude of the transfer function, is given by

$$f_{peak} = v/\lambda \tag{1.1}$$

where the acoustic velocity v is a characteristic property of the material. Fig 1.2.5 shows the typical transfer function  $S_{12}$ -Parameter of SAW devices using  $Al_xGa_{1-x}N$  on sapphire substrates (x = 0, x = 0.53 and x = 1) [1]. The SAW velocity of epitaxial GaN film on sapphire substrates is around 4000 m/s.

Figure 1.2.5 The typical transfer function  $S_{12}$ -Parameter of SAW devices using  $Al_xGa_{1-x}N$  on sapphire substrates (x = 0, x = 0.53 and x = 1). [1]

#### 1.2.3 $Al_xGa_{1-x}N/GaN$ -based HEMTs

With a direct bandgap ranging from 3.4 to 6.2 eV for GaN and AlN, respectively, a III-nitride alloy system offers unique opportunities in heterojunction design. GaN processes a high electron saturation velocity, a large breakdown field and excellent thermal stability, making it very suitable for use as a channel material in RF power transistors [3, 4, 11-13, 42]. The AlGaN/GaN-based HEMT is the most widely investigated and mature one. Fig. 1.2.6 shows the cross-sectional schematic and the energy-band profile of a typical  $Al_xGa_{1-x}N/GaN$

HEMT. Because of the conduction band offsets, an electron potential well is formed at the hetero-interface between the AlGaN and GaN. The electrons are confined in this potential well to form a two-dimensional electron gas (2DEG) [1, 15]. As the electrons transport in a two-dimensional way, bulk scattering effects such as ionized impurity scattering are reduced, resulting in greatly improved electron mobility.

Figure 1.2.6 The cross-sectional schematic and the energy-band profile of a typical  $Al_xGa_{1-x}N/GaN$  HEMT.

Further contributing to the outstanding performance of AlGaN/GaN HEMTs is their ability to achieve a 2DEG with sheet carrier concentration of  $10^{13}$  cm<sup>-2</sup> or even higher without any intentional doping, well in excess of that achievable in the conventional III-V material systems. It has been proved that the formation of the high density 2DEG in AlGaN/GaN structures relies on strong spontaneous and piezoelectric polarization [18]. For the Ga-face AlGaN/GaN heterostructure grown by MOCVD, a thin AlGaN barrier layer on the GaN buffer layer experiences tensile strain caused by lattice mismatch. In the absence of external electric fields, the total macroscopic polarization (P) is the sum of the spontaneous polarization ( $P_{SP}$ ) in the equilibrium lattice and the strain-induced or piezoelectric polarization ( $P_{PE}$ ). The directions of the spontaneous and piezoelectric polarizations are both pointing towards the substrate, leading to a positive polarization induced charge density ( $+\sigma$ ).

$$|\sigma(x)| = |P_{PE}(Al_XGa_{1-x}N) + P_{SP}(Al_XGa_{1-x}N) - P_{SP}(GaN)|$$

(1.2)

Figure 1.2.7 The calculated charge density at the  $Al_xGa_{1-x}N/GaN$  interface plotted versus the alloy composition [15].

Free electrons tend to compensate the positive polarization induced charge and form a 2DEG with a sheet carrier concentration  $(n_s)$ , which is bound at the lower AlGaN/GaN interface for the Ga-face structures, as shown in the inset of Fig 1.2.7 [15].

$$n_{S}(x) = \frac{+\sigma}{e} - \left(\frac{\varepsilon_{0}\varepsilon_{r}(x)}{de^{2}}\right) \left[e\phi_{b}(x) + E_{F}(x) - \Delta E_{C}(x)\right]$$

(1.3)

where e is the electron charge,  $\varepsilon_0$  is the vacuum permittivity,  $\varepsilon_r$  is the relative dielectric constant of the  $Al_xGa_{1-x}N$  layer, d is the thickness of the barrier layer,  $\emptyset_b$  is the Schottky barrier height,  $E_F$  is the Fermi level with respect to the GaN conduction-band-edge energy, and  $\Delta E_C$  is the conduction band offset at the AlGaN/GaN interface where a 2DEG forms.

By increasing the Al composition of the barrier, the piezoelectric and spontaneous polarizations are increasing, and likewise the polarization induced charge  $(+\sigma)$  and the sheet carrier concentration  $(n_s)$ . In Fig 1.2.7, the charge density  $(\sigma/e)$  at the Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN interface caused by the spontaneous and piezoelectric polarizations is plotted versus the alloy

composition.

Figure 1.2.8 The 15-element small signal equivalent circuit model for a HEMT [43].

As shown in Fig. 1.2.6, a HEMT is formed by placing one Schottky contact as the gate electrode and two Ohmic contacts as the source/drain (S/D) electrodes on top of an AlGaN/GaN heterostructure. The 2DEG sheet carrier concentration within the heterojunction channel and therefore the drain current of the HEMT can be controlled or modulated by applying an appropriate bias voltage on the Schottky barrier gate. In order to design an RF or microwave HEMT device, it is crucial to understand the principles of device operation and to take into consideration the effect of parasitic components. Fig. 1.2.8 shows the most popular 15-element small signal equivalent circuit model for a HEMT [43]. The grey box highlights the intrinsic device elements, which include the intrinsic transconductance ( $g_m$ ), the gate-source and gate-drain capacitance ( $G_{gs}$  and  $G_{gd}$ ), the drain-source coupling capacitance ( $G_{ds}$ ), the charging resistance ( $G_{hs}$ ) and the output resistance ( $G_{hs}$ ). The  $G_{hs}$ , in the expression of  $G_{hs}$  of  $G_{hs}$ , is the time delay it takes for the channel depletion region to respond to the gate signal. The parasitic elements include the pad capacitances  $G_{hs}$ ,  $G_{hs}$  and  $G_{hs}$ .

the pad inductances  $L_g$ ,  $L_d$ , and  $L_s$ , and the gate and series S/D resistances  $R_g$ ,  $R_s$ , and  $R_d$ . The physical origins of these equivalent circuit elements are illustrated in Fig. 1.2.9 [44]. The intrinsic elements are a function of the direct current (DC) bias, while the parasitic ones are bias independent. The equivalent circuit elements, which are usually extracted from the devices' microwave S-parameter measurements, can be used to analyze and predict the RF performance of a HEMT.

Figure 1.2.9 The physical origins of the elements in an equivalent circuit model [44].

The  $g_m$  is the measure of the devices' intrinsic gain, representing the effectiveness of the gate in modulating the drain current. When taking into account the parasitic components, such as  $R_s$ , the extrinsic transconductance  $(G_m)$  can be described as

$$G_m = \frac{g_m}{1 + g_m \cdot R_s} \tag{1.4}$$

The current gain cut-off frequency  $(f_T)$  and the maximum oscillation frequency  $(f_{max})$  are two figures of merit (FoMs) for the high frequency performance of a HEMT. The  $f_T$  is the frequency at which the short circuit current gain  $(|h_{2I}|^2)$  of the device falls to unity. In the first order approximation, the equation below gives the definition of  $f_T$ :

$$f_T = \frac{g_m}{2\pi (C_{gs} + C_{gd})} \tag{1.5}$$

In general, a device with a high  $f_T$  value will function usefully at a higher frequency than a

device with a lower  $f_T$  value. A high  $f_T$  can be achieved by increasing  $g_m$  and reducing  $C_{gs}$  and  $C_{gd}$  of the HEMT. Considering the physical mechanism of a HEMT operation,  $f_T$  can also be represented by the channel electron drift velocity through the following equation:

$$f_T = \frac{v_{sat}}{2\pi L_G} \tag{1.6}$$

where  $v_{sat}$  is the saturation electron drift velocity and  $L_G$  is the gate (channel) length ( $L_G$ ). It is apparent that a higher electron saturation velocity and smaller  $L_G$  in higher  $f_T$ .

The  $f_{max}$  is the highest frequency at which power gain can be obtained from a device. This may be used as an indicator of the ultimate frequency limits of a device. For most RF/microwave applications, the  $f_{max}$  appears to be more useful than the  $f_T$  because microwave designers are typically concerned with power gain at matched conditions. The  $f_{max}$  is defined as the frequency at which the power gain of a device reaches unity, which can be expressed as:

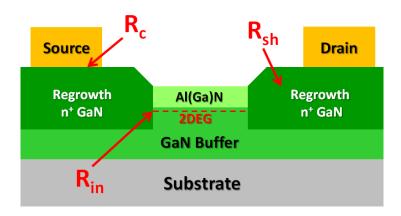

$$f_{max} = \frac{f_T}{\sqrt{\frac{\frac{4}{R_{ds}}\left(R_{in} + \frac{R_S + R_g}{1 + g_m R_S}\right) + \frac{^{4C}gd}{^{5C}gs}\left(1 + \frac{^{2.5C}gd}{^{5C}gs}\right)(1 + g_m R_S)^2}}$$

(1.7)

A simple form of the equitation can be written as:

$$f_{max} = \frac{f_T}{2} \sqrt{\frac{R_{ds}}{R_g + R_{in}}} \tag{1.8}$$

Apparently, to maximize the  $f_{max}$ , the  $f_T$  and the resistance ratio  $\frac{R_{ds}}{R_g + R_{in}}$  of the HEMT have to be optimized.

#### 1.3 Contributions and Organization of Thesis

Electronic sensing and RF-communication systems have dramatically changed our daily lives since 1947, when the first transistor was invented. Advanced semiconductor devices are the key components within these systems and ultimately determine their performances. In this never ending challenge, GaN-based semiconductors and heterostructure devices are unique

contenders for future leading-edge electronic systems due to their outstanding material properties with respect to speed, power, efficiency, linearity, and robustness. Therefore, it is essential and meaningful to develop novel GaN-based devices and circuits for next-generation sensing and RF-communication applications.

This thesis aims at the exploration and design of such devices and monolithic integration technologies for GaN-based sensors and RF/microwave power electronics. The work can be divided into sensors and high-frequency power devices.

For the sensors, Lamb-wave and SAW delay line devices and their monolithically integrated oscillators were designed and fabricated with MOCVD-grown GaN-based thin films on silicon substrates. The Lamb-wave sensors were firstly improved by optimizing the device geometries. Then the Lamb-wave and SAW delay line devices were integrated with AlGaN/GaN HEMT circuits to form monolithic oscillators. After that, the temperature effects and power handling capabilities were investigated for the discrete and integrated devices. These integrated oscillators are reported up-to-date.

For the high frequency power devices, innovative device scaling technologies were implemented to boost the device performance of the GaN-based HEMTs. A gate-last self-aligned process was first developed by employing S/D regrowth and low-k benzocyclobutene (BCB) planarization techniques, which enabled the reduction of access resistance and parasitic capacitance, minimizing the RC-related delay. A thin AlN barrier was then used to facilitate the device scaling, with increased gate control capabilities and maintaining high channel conductivity. *In-situ* SiN<sub>x</sub> grown by MOCVD was investigated as gate dielectric for the AlN/GaN MISHEMTs. The advantages of the *in-situ* SiN<sub>x</sub> over other *ex-situ* deposited insulators includes better surface passivation effects, suppression of gate leakage current and the elimination of process- and growth- related defects.

Finally, high performance in-situ  $SiN_x/AlN/GaN$  MISHEMTs were fabricated using the abovementioned techniques. The device with a  $L_G$  of 0.23  $\mu$ m exhibited a maximum drain current density ( $I_{DS}$ ) exceeding 1600 mA/mm, with a high on/off ratio ( $I_{on}/I_{off}$ ) of over  $10^7$ . The  $f_T$  and  $f_{max}$  were 55 and 86 GHz, respectively. Additionally, the effect of temperature on

both the DC and RF performances of the gate-last self-aligned MISHEMTs was studied from room temperature (RT) up to 550 K. The small signal equivalent circuit model of the fabricated MISHEMTs was also analyzed to provide insights into the role of various parameters in the device performance.

The rest of this dissertation is organized as follows:

Chapter 2 presents the design and fabrication of Lamb-wave and SAW delay line devices and their monolithic integrated oscillators using GaN-on-Si technology. After a review of prior works, Lamb-wave sensors with improved performance are demonstrated. The development of the monolithic acoustic wave oscillators is also discussed in detail.

Chapter 3 describes the development of a gate-last self-aligned technology for fabrication of AlGaN/GaN HEMTs. Regrown S/D Ohmic contactS, low-k BCB planarization and precisely defined gate-to-regrown-S/D distances ( $L_{GS}/L_{GD}$ ) by the SiN<sub>x</sub> sidewall spacers are key elements of the devices. The details of the fabrication processes and device characterizations are provided in this chapter.

Chapter 4 reports the investigation of an in-situ SiN<sub>x</sub> gate dielectric grown on AlN/GaN heterostructures by MOCVD. Both material structural and electrical characterizations are performed to evaluate the performance of the in-situ SiN<sub>x</sub> film as a gate insulator. The benefits of using in-situ SiN<sub>x</sub> as gate dielectric, such as suppressed leakage current and a low interface trap state density, are presented.

In Chapter 5, high performance *in-situ* SiN<sub>x</sub>/AlN/GaN MISHEMTs are demonstrated using the techniques and material structures developed in Chapter 3 and Chapter 4. The thermal evolution of the DC and RF performances of the fabricated devices and their small signal equivalent circuit modeling are discussed.

Chapter 6 summarizes the dissertation and suggests future research work.

# CHAPTER 2 LAMB-WAVE SENSORS AND MONOLITHIC INTEGRATED ACOUSTIC WAVE OSCILLATORS USING GAN-ON-SI

#### 2.1 Introduction

Acoustic wave technology has been used extensively in commercial applications such as telecommunications, automotives and environmental sensing, for several decades. Monolithic integration of acoustic wave devices with on-chip electronics yields a compact system-on-chip (SoC) solution, which has advantages in both detection and communication applications. The advantages include improved performance, increased yield, reduced packaging volume and lower overall cost.

With high acoustic wave velocity and a strong piezoelectric effect, GaN has been exploited for the fabrication of acoustoelectric devices such as filters and UV sensors [30-37]. Their inherent chemical inertness and bio-compatibility also make them attractive for biosensors [5, 38, 39]. Furthermore, GaN-based acoustic wave devices can be potentially integrated with a wide range of other well-developed GaN devices, such as HEMTs, LEDs, and power switches. The first demonstration of a monolithic integrated SAW oscillator on a GaAs substrate can be traced back to 1999 [45]. However, the integration of GaN-based electronics with acoustic functions is still limited and mostly at device level without proper circuit functions [46, 47], for example the integration of one acoustic wave filter with one HEMT for signal amplification.

Compared to their conventional counterparts, such as those based on silicon and GaAs technologies, circuits based on wide bandgap materials (GaN and SiC) offer superior performance under high-temperature environments. Smart sensors with integrated electronics that can operate at high ambient temperatures without external cooling can greatly benefit a variety of industrial applications, especially in automotive, aerospace and deep-well drilling systems [48]. For example, automobile engines and brake sensors are required to operate reliably at ambient temperatures above 150 °C, telemetry during underground mining and oil

drilling requires sensors and electronics to handle up to 225  $^{\circ}$ C, and aircraft engine intelligent control and structural health monitoring systems with various sensors need to function up to 500  $^{\circ}$ C and higher [49, 50]. In such applications, monolithic integration of the sensor circuits with wireless transceivers would greatly reduce the system form factor, weight, and complexity. An essential component in these wireless sensor systems with high-temperature tolerance is an RF local oscillator possessing low-temperate dependence and coefficients. The RF carrier signal will be modulated by the sensor signal and transmitted to the cooler part of the system.

Recently, there have been several reported results of hybrid oscillators based on SiC operating at high temperatures ranging from 200  $\,^{\circ}$ C to 475  $\,^{\circ}$ C [51-53]. These oscillators used Cree's SiC MESFETs mounted onto a substrate carrier. In addition, an NMOS SiC ring oscillator operating at 625 kHz under 300  $\,^{\circ}$ C [54] and a 66 MHz, 375  $\,^{\circ}$ C ring oscillator based on AlGaN/GaN HEMTs on a sapphire substrate [55] have been demonstrated. However, these oscillators suffered from a relatively large temperature drift with large temperature coefficient of frequency (TCF) in the order of  $10^3$  ppm/ $\,^{\circ}$ C.

In this work, GaN-based Lamb-wave sensors were firstly improved by modifying the device geometries [56]. Then, monolithic integrated SAW and Lamb-wave oscillators [57, 58], which are suitable for sensing applications at high ambient temperature and can potentially be extended to high power RF systems, were developed.

#### 2.2 Two generations of GaN-based Lamb-wave sensors

Nowadays, MOCVD technology is mature enough to allow versatile sensors to be fabricated with high-quality epitaxial GaN on silicon substrates, instead of on traditional sapphire or SiC substrates, whilst conventional Si-based semiconductor processing techniques can still be adopted. Recently, high performance Lamb-wave sensors have been developed using GaN-on-Si structures by both our group [39] and others [38] independently, with the former showing good mass sensitivity and the latter demonstrated for chemical and biological sensing.

Figure 2.2.1 The schematic of the Lamb-wave sensor using a GaN-on-Si structure.

Fig. 2.2.1 shows a schematic of the sensor structure previously developed by our group, referred as first generation sensors (*G-I*) in this dissertation. The Lamb-wave sensors are of two-port delay line configurations formed by a 1-µm thick suspending GaN membrane with two Cr/Au top IDTs located near the edges of the back side cavity formed by local excavation of the silicon substrate.

Table 2-1 The design parameters of *G-I* and *G-II* sensors.

| Design Parameters              | G-I           | G-II                      |

|--------------------------------|---------------|---------------------------|

| IDT Period (λ)                 | 16 μm         | 16 μm                     |

| Width of IDT Fingers           | 4 μm          | 4 μm                      |

| Number of Pairs in each IDT    | 15            | 20                        |

| IDT Aperture                   | 400 μm        | 400 μm                    |

| Side to Side IDT Separation    | 240 μm (15 λ) | $1440 \mu m (90 \lambda)$ |

| Thickness of the Membrane      | 1.085 μm      | 1.085 μm                  |

| Dimension of the Si Excavation | 1.2 mm×1.2 mm | 0.6 mm×2.2 mm             |

In this work, second generation sensors (*G-II*) with similar configurations to *G-I*, but different geometries, were designed. The design parameters of the *G-I* and *G-II* sensors are compared in Table 2-1. Optical micrographs of the fabricated sensors are shown in Fig. 2.2.2. The IDT electrodes that appear suspended in air are, in fact, mechanically supported by the transparent GaN membrane.

Figure 2.2.2 The optical micrographs of the fabricated G-I and G-II sensors.

There were four main processing steps in the fabrication of Lamb-wave sensors, as illustrated in Fig. 2.2.3. Firstly, a stack of GaN-based epitaxial layers was grown on a high-resistivity Si (111) substrate using an AIXTRON2000HT MOCVD system, as shown in Fig. 2.2.3(a). High-resistivity substrates were used to minimize electromagnetic feedthrough. The full epitaxial stack consisted of a 40 nm buffer layer and a 900 nm GaN layer. A 20 nm interlayer and a 125 nm AlGaN layer were inserted in the GaN layer to counter-balance the tensile strain produced by the mismatch of the thermal expansion between the substrate and the epi-layers and to prevent cracks on the surface. Secondly, the IDT electrodes were formed on top of the epi-layers by e-beam evaporation of Cr/Au (3 nm / 30 nm) and a liftoff process, as shown in Fig. 2.2.3(b). Thirdly, similar techniques to those in the second step were performed on the back side of the wafer to pattern a 300 nm thick Al etch mask for silicon substrate removal, as shown in Fig. 2.2.3(c). Finally, the silicon substrate was selectively removed by an SF<sub>6</sub>-based inductively coupled plasma (ICP) etching process for releasing the membrane. The fabrication was completed by stripping away the Al mask with a hot H<sub>3</sub>PO<sub>4</sub> solution. Fig. 2.2.3(d) is a cross-sectional view of the finished device.

Figure 2.2.3 The fabrication process of the Lamb-wave sensors.

The fabricated sensors were characterized using an RF-probe station, a pair of RF-probes, and an Agilent Vector Network Analyzer. Short-Open-Load-Through (SOLT) calibration was performed prior to taking measurements, and no de-embedding was carried out. All the measurements were conducted with  $50-\Omega$  termination impedance. The magnitude of the  $S_{21}$  Parameters from 300 kHz to 600 MHz of the unloaded G-I and G-II sensors are shown in Fig. 2.2.4. The peak is observed at around 473 MHz, which indicates the propagation of the lowest order symmetric mode ( $S_0$ ) wave. The corresponding phase velocity is ~7580m/s for the 16

$\mu$ m wavelength and the 1.085  $\mu$ m thick GaN-based membrane. This is in agreement with the reported value in the literature [38]. The lowest order anti-symmetric mode (A<sub>0</sub>) wave, appearing at around 50 MHz, is much weaker than the S<sub>0</sub> wave. This suggests a weak electroacoustic coupling and a high noise level near the lower frequency A<sub>0</sub> peak.

Figure 2.2.4 The magnitude of the S<sub>21</sub> Parameter of the unloaded *G-I* and *G-II* sensors.

There are three different design parameters between the two generations of sensors: the number of pairs in each IDT, the separation between two IDTs, and the dimension of the silicon excavation, as listed in Table 2.2.1.

Firstly, the signal strength of the  $S_0$  wave in the G-II sensors is -20 dB, approximately 4 dB higher than that of the G-I sensors. This can be explained by the increased number of IDT pairs (from 15 to 20), which results in a stronger electroacoustic coupling in the G-II sensors, that is more than needed for compensating for the attenuation induced by a longer acoustic path length.

Secondly, the noise floor around the  $S_0$  peak is considerably lower, by more than 10 dB in the G-II sensors, compared with that of the G-I sensors. Other weak acoustic modes, such as the shear horizontal acoustic plate mode (SH-APM), can also be observed in Fig. 2.2.4, but they are out of the scope of this dissertation. The lower noise floor in the G-II sensors is a

result of the significantly increased IDT separation from 15  $\lambda$  to 90  $\lambda$ .

Thirdly, the *G-II* sensors have a smaller area of silicon excavation (1.32 mm<sup>2</sup>) than that of the *G-I* sensors (1.44 mm<sup>2</sup>). This indicates that the performance improvements do not come at the expense of device size. As well, an improvement of fabrication yield and mechanical robustness in wafer handling was realized due to the reduction of the suspended membrane width from 1.2 mm down to 0.6 mm.

The mass sensitivities of the sensors were evaluated by loading or depositing different thicknesses of  $SiO_2$  on the back side of the membranes using plasma-enhanced chemical vapor deposition (PECVD). The shift of resonant frequency, due to the mass-loading effect in the acoustic wave propagation path, was recorded by measuring the  $S_{21}$  Parameters after each successive deposition. The linear relationships of the resonant frequency versus the thicknesses of deposited  $SiO_2$  for the G-I and G-II sensors are derived in Fig 2.2.5, with the correlation coefficients ( $R^2$ ) of 0.95834 and 0.99812, respectively. The absolute mass sensitivity in terms of frequency shift ( $S_{mf}$ ) is defined as

$$S_{mf} = \frac{\Delta f}{\Delta m} \tag{2.1}$$

where  $\Delta f$  is the shifts of the resonant frequency produced by mass loading on the sensor surface.  $\Delta m$  is the loaded mass per unit area. Since

$$\Delta m = \rho \times \Delta d \tag{2.2}$$

where  $\rho$  and  $\Delta d$  are the density of the loaded material (2.3 g/cm<sup>3</sup> for PECVD SiO<sub>2</sub> [59]) and the change of thickness, respectively,

$$S_{mf} = \frac{\Delta f}{\Delta d} \cdot \frac{1}{\rho} \tag{2.3}$$

where  $\frac{\Delta f}{\Delta d}$  is the gradient of the linear fit in the graph. The normalized mass sensitivity in terms of frequency shift is defined as the absolute mass sensitivity divided by unloaded resonant frequency, which is 473 MHz in this case. The *G-II* sensors exhibit 1.6 times higher sensitivity (272 cm<sup>2</sup>/g vs.174 cm<sup>2</sup>/g) and better linearity than the *G-I* sensors. This can be