## Integration of Low Loss Interconnects in CMOS

by

### Salahuddin Raju

A Thesis Submitted to

The Hong Kong University of Science and Technology

in Partial Fulfillment of the Requirements for

the Degree of Doctor of Philosophy

in the Department of Electronic and Computer Engineering

August 2016, Hong Kong

## **Authorization**

I hereby declare that I am the sole author of the thesis.

I authorize the Hong Kong University of Science and Technology to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize the Hong Kong University of Science and Technology to reproduce the thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Salahuddin Raju

Lalalmodin Room

August 2016

## Integration of Low Loss Interconnects in CMOS

by

#### Salahuddin Raju

This is to certify that I have examined the above PhD thesis and have found that it is complete and satisfactory in all respects, and that any and all revisions required by

| the thesis examination committee have been made.                   |

|--------------------------------------------------------------------|

|                                                                    |

| - Mure                                                             |

| Prof. Mansun Chan, ECE, Thesis Supervisor                          |

| MEUS.                                                              |

| Prof. Patrick Yue, ECE, Thesis Co-Supervisor                       |

| - Shigan                                                           |

| Prof. Zhigang Li, MAE, Chairperson of Thesis Examination Committee |

| disconting.                                                        |

| Prof. Wing-Hung Ki, ECE, Thesis Examination Committee Member       |

| LC: Cler                                                           |

| Prof. Kevin Chen, ECE, Thesis Examination Committee Member         |

| 30. D                                                              |

| Prof. Zhiyu Yang, PHYS, Thesis Examination Committee Member        |

| Mystal                                                             |

Prof. Philip Mok, ECE, Acting Head of Department

The Department of Electronic and Computer Engineering  ${\bf August~2016}$

### Acknowledgments

I would like to express my deepest gratitude to my supervisors, Prof. Mansun Chan and Prof. Patrick Yue. Throughout my study, their patient guidance helped me to develop clear understanding in my research area. Without their supervision this work would have not been possible. Most importantly, their enthusiasm towards research has motivated me to move forward, and challenge the boundary of my work.

Many people have contributed to this work. I would like to express my heartfelt gratitude each one of my colleagues and friends for their support. In early stage of my research, I had many discussion and brainstorming with Dr. Changjian Zhou. The work on low dielectric material was initiated after one of such brainstorming sessions. Since then, we had numerous collaborations, certainly a significant portion of the credit goes to him. I would also like to thank Suwen Li for helping me to grow CNTs for low dielectric materials. I had a great pleasure and fun working with the wonderful friends in the Device Characterization Lab (DCL). It was always enjoyable to discuss research topics in the meeting. The feedback from my friends in DCL was very useful. Since, a part of my research is related to the circuit-device interaction, I had always interaction with the members of High Speed Silicon Lab (HS2L). I would like to thank all my friends in HS2L. In particular, I would like to thank Yipeng Wang for helping with circuit simulation. It was my privilege to work with Dr. Haikun Jia in HS2L. Dr. Jia helped me with CMOS integration of antenna and measurements. I am extremely thankful to him in this regard.

The completion of this work would not be possible without one person, Sanjida Yeasmin, whose love and affection played the most important role in my PhD life. I am also extremely grateful to my parents. Their steadfast support and belief in me have been my greatest strength at every step of my life.

# Contents

| ${f T}{f i}$     | tle             |                                                                     | i            |

|------------------|-----------------|---------------------------------------------------------------------|--------------|

| $\mathbf{A}$     | utho            | rization                                                            | ii           |

| Si               | $\mathbf{gnat}$ | ure                                                                 | iii          |

| $\mathbf{A}_{0}$ | ckno            | wledgments                                                          | iv           |

| Ta               | ıble (          | of Contents                                                         | $\mathbf{v}$ |

| Li               | ${ m st}$ of    | Figures                                                             | vii          |

| ${f Li}$         | ${ m st}$ of    | Tables                                                              | xii          |

| $\mathbf{A}$     | bstra           | uct                                                                 | xiii         |

| 1                | Int             | erconnect Challenges and Technology Requirements                    | 1            |

|                  | 1.1             | Low- $k$ Material Integration Challenges in BEOL                    | 2            |

|                  | 1.2             | Benchmarking Interconnects for On-Chip Magnetics                    | 4            |

|                  | 1.3             | Interconnect Non-Idealities for Electromagnetic Applications        | 6            |

|                  | 1.4             | References                                                          | 7            |

| <b>2</b>         | Na              | ${f notube}$ Assisted Ultralow- $k$ Dielectrics                     | 9            |

|                  | 2.1             | Formation of Nanotube Assisted Vertically Aligned Cylindrical Pores | 10           |

|    | 2.2   | Improved Mechanical Properties of the Dielectric Through VACP                   | 15        |

|----|-------|---------------------------------------------------------------------------------|-----------|

|    | 2.3   | Impact of Pore Morphology on the Material Characteristics                       | 19        |

|    | 2.4   | Reliability of Ultralow- $k$ Porous Dielectrics                                 | 25        |

|    | 2.5   | Signal Integrity Improvement Utilizing VACP Dielectrics                         | 28        |

|    | 2.6   | Concluding Remarks on VACP Dielectrics                                          | 29        |

|    | 2.7   | References                                                                      | 29        |

| 3  | Eng   | gineered Interconnects with Ultra-Thick Dielectric and Metal                    | 33        |

|    | 3.1   | BEOL Compatible Ultra-Thick Dielectric Processing                               | 34        |

|    | 3.2   | Ultra-Thick Interconnect Metal Processing                                       | 35        |

|    | 3.3   | Engineered Interconnects for High Quality On-Chip Magnetics                     | 36        |

|    |       | 3.3.1 Inductor Self-Resonance Frequency Improvement through Dielec-             |           |

|    |       | tric Engineering                                                                | 37        |

|    |       | 3.3.2 Resistive Loss Reduction in On-Chip Magnetics                             | 39        |

|    | 3.4   | Engineered Interconnects for Power Supply On-Chip                               | 44        |

|    | 3.5   | Conclusion on Engineered Interconnects                                          | 49        |

|    | 3.6   | References                                                                      | 49        |

| 4  | Mi    | tigation of Interconnect Radiation Loss on Silicon                              | <b>54</b> |

|    | 4.1   | Improved Radiation Efficiency through Thick Dielectric Processing $\ \ . \ \ .$ | 55        |

|    | 4.2   | Broadband Millimeter-Wave On-Chip Planar Antennas                               | 59        |

|    | 4.3   | Integration of On-Chip Antenna with BEOL and System Demonstration               | 65        |

|    | 4.4   | Concluding Remarks on Integrated On-Chip Antennas                               | 69        |

|    | 4.5   | References                                                                      | 69        |

| 5  | Co    | nclusions                                                                       | 72        |

| Ρι | ıblic | ations                                                                          | 74        |

# List of Figures

| Cross-section of an interconnect structure (Courtesy of IBM)                  | 2                                                        |

|-------------------------------------------------------------------------------|----------------------------------------------------------|

| Implementation of porous dielectric with spherical pores                      | 3                                                        |

| Inverse relationship between $k$ -value and the elastic modulus of the porous |                                                          |

| dielectrics                                                                   | 3                                                        |

| Cross-section of an inductor and its basic circuit parameters                 | 5                                                        |

| Simulation platform of the benchmark test                                     | 5                                                        |

| Highest possible $Q$ -value at different frequency and its corresponding in-  |                                                          |

| ductance.                                                                     | 6                                                        |

| Antenna radiation (a) and surface wave mode (b) in silicon                    | 7                                                        |

| The radiation pattern of a dipole on silicon at 60 GHz                        | 7                                                        |

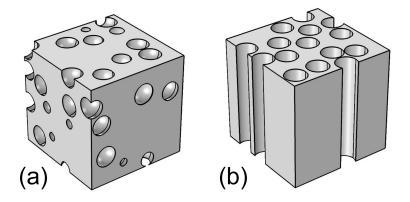

| Dielectric films with spherical (a) and vertically aligned cylindrical pores  |                                                          |

| (b) geometries with $\approx 50\%$ porosity                                   | 10                                                       |

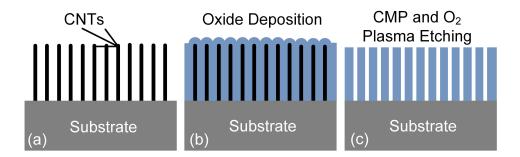

| Formation process of vertically aligned cylindrical pores in dielectric as-   |                                                          |

| sisted by vertically aligned nanotubes. (a) CNT growth on a substrate, (b)    |                                                          |

| Desired oxide deposition, and (c) Chemical mechanical polishing (CMP)         |                                                          |

| and CNT removal by $O_2$ plasma                                               | 11                                                       |

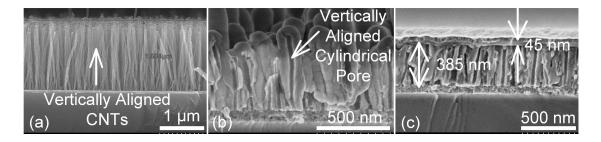

| Formation process of vertically aligned cylindrical pores in dielectric as-   |                                                          |

| sisted by vertically aligned nanotubes. (a) CNT growth on a substrate, (b)    |                                                          |

| Desired oxide deposition, and (c) Chemical mechanical polishing (CMP)         |                                                          |

| and CNT removal by $O_2$ plasma                                               | 13                                                       |

|                                                                               | Implementation of porous dielectric with spherical pores |

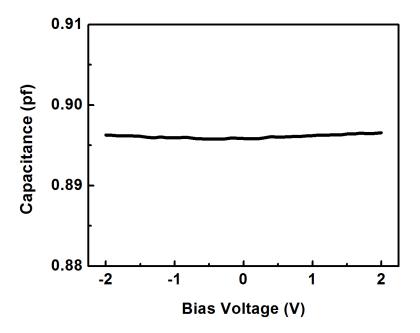

| 2.4  | Capacitance measurement at different bias voltages                                     | 14 |

|------|----------------------------------------------------------------------------------------|----|

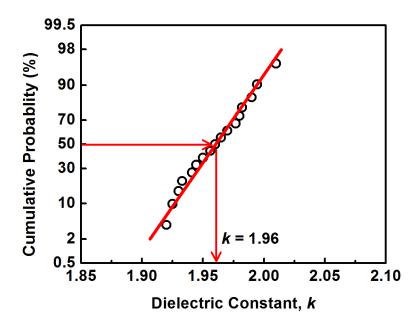

| 2.5  | Cumulative probability of measured dielectric constants                                | 14 |

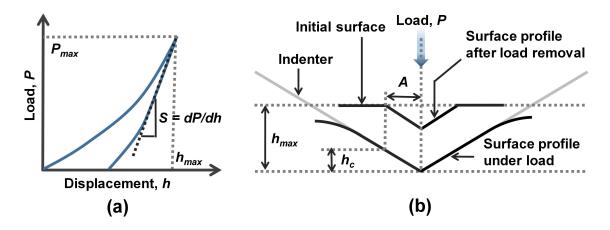

| 2.6  | (a) Load versus displacement curve for a elastic material, the loading                 |    |

|      | is followed by elastic unloading process. (b) Cross-section of indenter                |    |

|      | and sample interaction during loading and unloading indicating quantities              |    |

|      | used for analysis                                                                      | 15 |

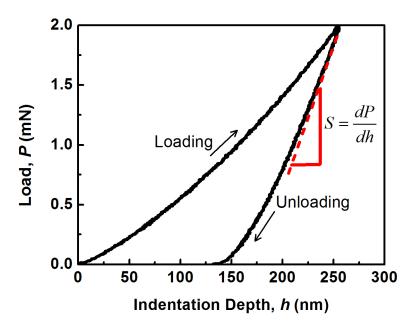

| 2.7  | Experimentally obtained load versus displacement curve during elastic                  |    |

|      | modulus measurement of VACP dielectric by nanoindentation                              | 17 |

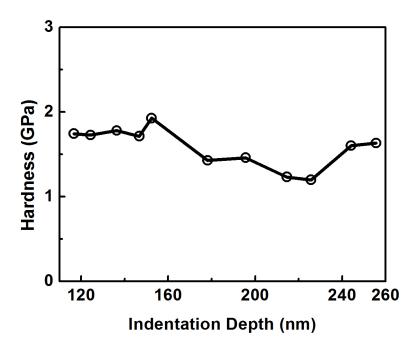

| 2.8  | Experimentally obtained hardness of VACP dielectric at different inden-                |    |

|      | tation depths                                                                          | 18 |

| 2.9  | Experimentally obtained elastic modulus of VACP dielectric at different                |    |

|      | indentation depths                                                                     | 19 |

| 2.10 | Normalized elastic modulus $(E_P/E_B)$ as a function of porosity. Here, $E_B$          |    |

|      | is the elastic modulus of bulk dielectric                                              | 21 |

| 2.11 | Normalized shear modulus $(G_P/G_B)$ as a function of porosity. Here, $G_B$            |    |

|      | is the elastic modulus of bulk dielectric                                              | 22 |

| 2.12 | Impact on porosity and pore morphology on the dielectric constant of $\mathrm{SiO}_2.$ | 23 |

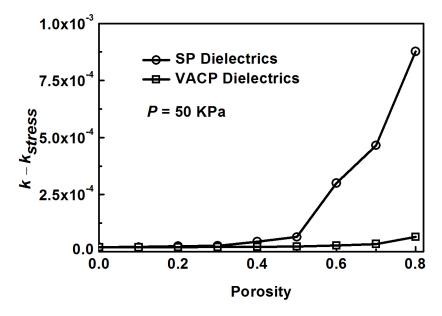

| 2.13 | Impact of an external stress on the dielectric constant at different porosity          |    |

|      | and pore morphology                                                                    | 23 |

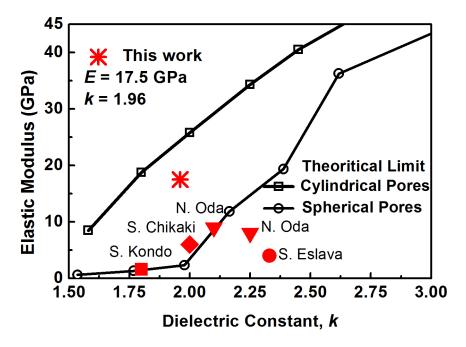

| 2.14 | Comparison of VACP dielectric with other reported technologies. And the                |    |

|      | theoretical (elastic modulus and dielectric constant upon different pore               |    |

|      | morphologies) and measured elastic modulus as a function of dielectric                 |    |

|      | constant                                                                               | 24 |

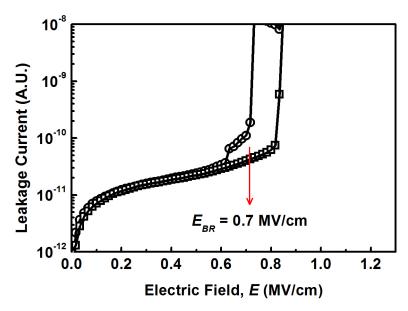

| 2.15 | Leakage current in VACP dielectric at different applied electric field                 | 25 |

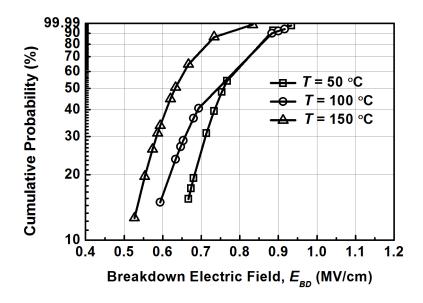

| 2.16 | The temperature dependency of the dielectric breakdown field                           | 26 |

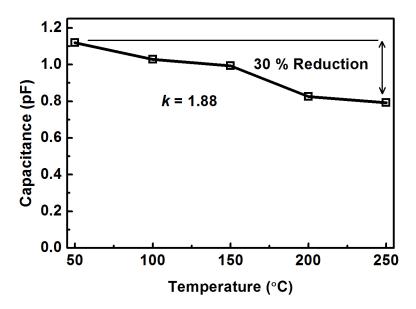

| 2.17 | Measured capacitance at different temperatures, impact on moisture uptake.             | 27 |

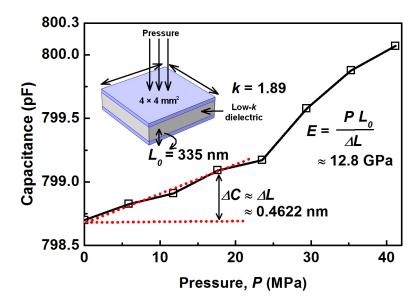

| 2.18 | The impact on capacitance upon different applied stresses                              | 27 |

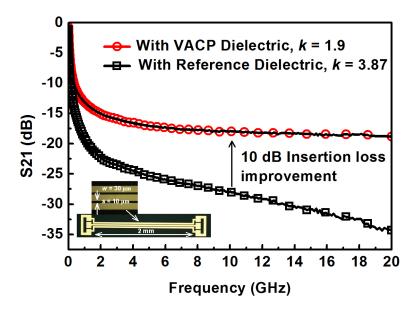

| 2.19 | Frequency response (S21) of 2 mm transmission lines in different dielectric                  |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | system                                                                                       | 28 |

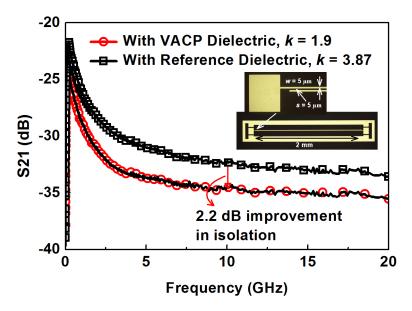

| 2.20 | Crosstalk response of 2 mm long adjacent traces upon different frequency.                    | 29 |

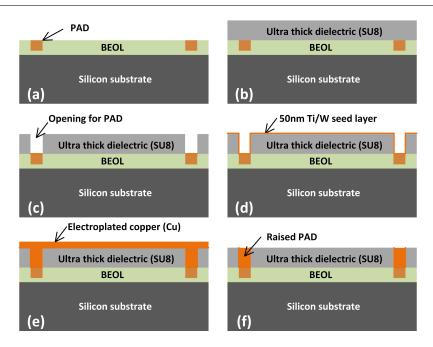

| 3.1  | Fabrication process of ultra-thick dielectric process for interconnects. (a)                 |    |

|      | A sample IC with BEOL, (b) Spin coating of the thick dielectric, (c)                         |    |

|      | Photolithography to remove material over the PAD, (d) Ti/W seed layer                        |    |

|      | deposition, (e) Copper electroplating, and (f) Polishing to remove over-                     |    |

|      | burden copper                                                                                | 34 |

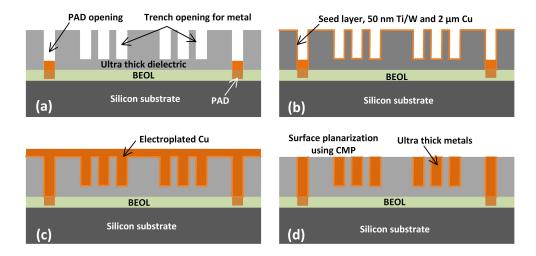

| 3.2  | Fabrication steps of ultra-thick metal processing. (a) Deep trench patterns                  |    |

|      | for thick metals, (b) Ti/W seed layer deposition for electroplating, (c)                     |    |

|      | Copper electroplating, and (d) Overburden copper removal for thick metal                     |    |

|      | tracks                                                                                       | 36 |

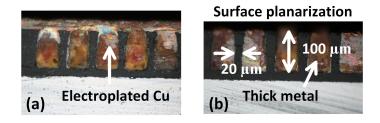

| 3.3  | The cross-section of the wafer before (a) and after (b) the CMP process.                     | 36 |

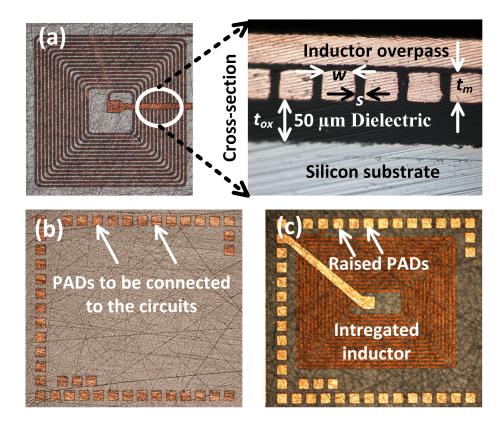

| 3.4  | (a) The micrograph of a test-inductor and its cross-section. (b) Dummy                       |    |

|      | PADs to mimic a CMOS chip configuration. (c) Integrated inductor                             | 37 |

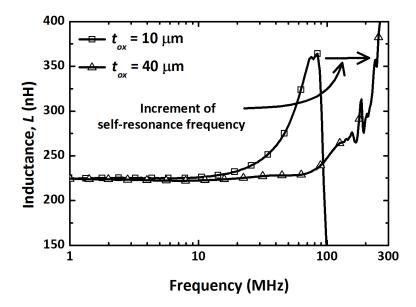

| 3.5  | Improvement of self-resonance frequency due to thick dielectric                              | 39 |

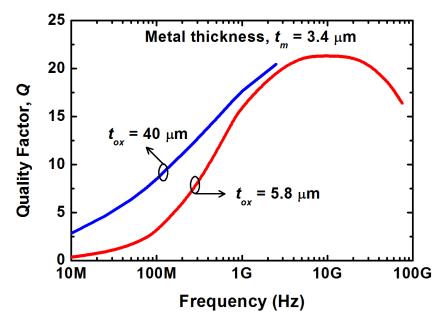

| 3.6  | Benchmarking of thick dielectric process for integrated magnetics                            | 39 |

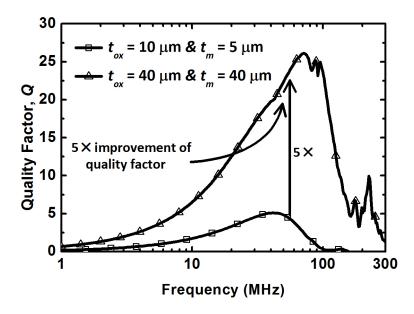

| 3.7  | Improvement of indctor quality factor due to thick metal and dielectric                      | 40 |

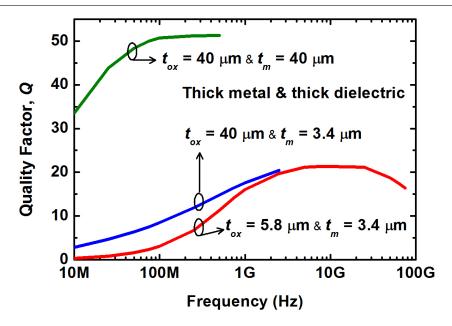

| 3.8  | Benchmarking of thick dielectric and metal process for integrated magnetics.                 | 41 |

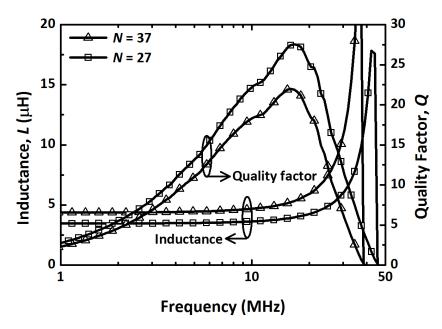

| 3.9  | Frequency response of $L$ and $Q$ of $4.5 \times 4.5 \text{ mm}^2$ inductors on top of a 10  |    |

|      | $\Omega\text{-cm}$ substrate. Design parameters: track width $w=30~\mu\text{m},$ spacing $s$ |    |

|      | = 15 $\mu$ m, metal thickness $t_m$ = 40 $\mu$ m, bottom dielectric thickness $t_{ox}$ =     |    |

|      | 50 $\mu$ m, and turn number $N=37$ and 27                                                    | 42 |

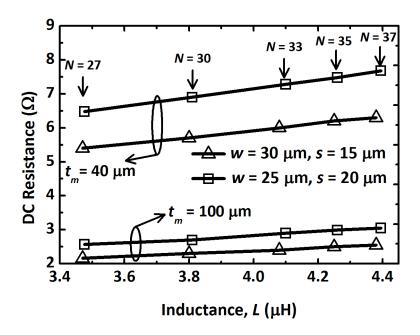

| 3.10 | DC resistance was reduced by increasing the thickness of the metal $(t_m)$ .                 | 43 |

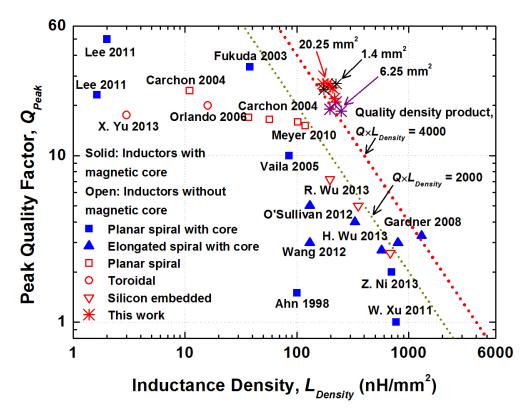

| 3.11 | Measured peak quality factor $(Q)$ and inductance density $(L_{Density})$ of the         |    |

|------|------------------------------------------------------------------------------------------|----|

|      | leading technologies for inductor integration on silicon. Here, $L_{Density}$ is         |    |

|      | defined as inductance per $mm^2$                                                         | 43 |

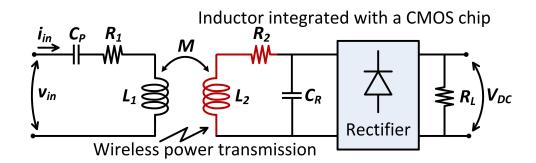

| 3.12 | Complete schematic diagram of a wireless power system on-chip                            | 44 |

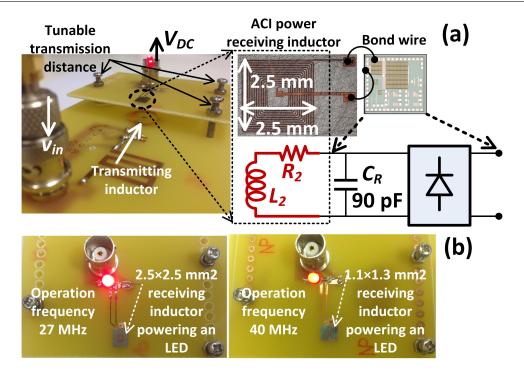

| 3.13 | (a) The experimental setup for measuring the characteristics of the wire-                |    |

|      | less power transmission system. (b) The mm-size power receiving inductor                 |    |

|      | is powering an LED at 10 mm distance                                                     | 46 |

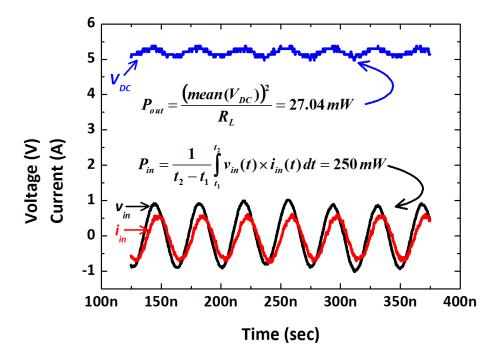

| 3.14 | Time domain measurement of transmitting signals $v_{in}$ and $i_{in}$ , and the          |    |

|      | received DC voltage $V_{DC}$ across the 1 K $\Omega$ load resistance, at 5.3 mm          |    |

|      | distance. The efficiency was calculated as $\eta = P_{out}/P_{in} = 10.8\%$              | 46 |

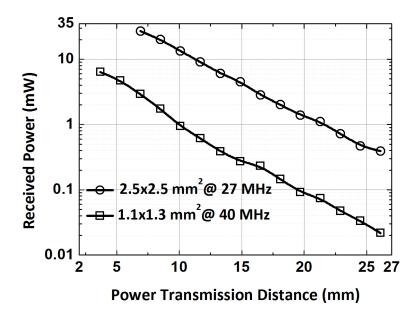

| 3.15 | Received power by the mm–size wireless power receiver at different trans-                |    |

|      | mission distances, provided that the transmitted power was 250 mW. $$                    | 47 |

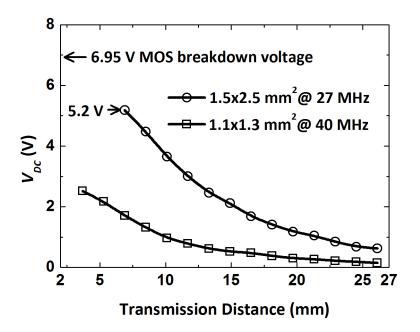

| 3.16 | Measured rectified DC voltage across the load resistance ( $R_L=1~\mathrm{K}\Omega$ ) at |    |

|      | different transmission distances                                                         | 47 |

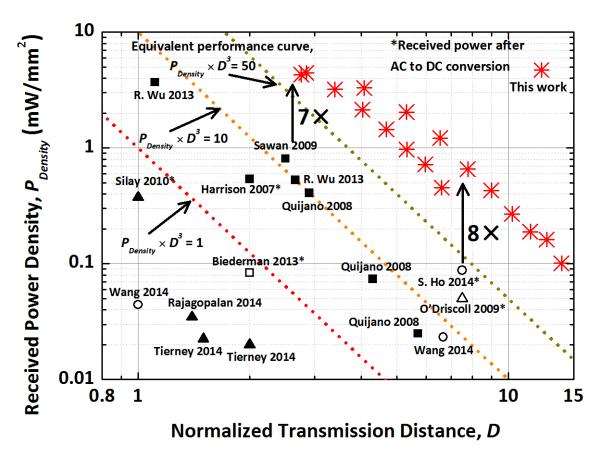

| 3.17 | Summary of reported wireless power transmission systems with different                   |    |

|      | inductor integration schemes in the literature. The normalize transmission               |    |

|      | distance, $D$ , is defined as the ratio of transmission distance and the size            |    |

|      | of the power receiving inductor, and the received power density is defined               |    |

|      | as- $P_{Density} = P_{out}/Area = P_{in} \times \eta/Area$                               | 48 |

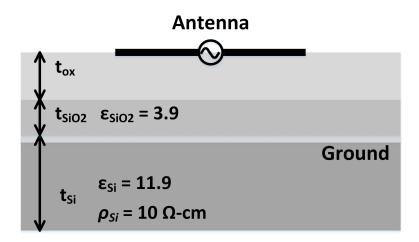

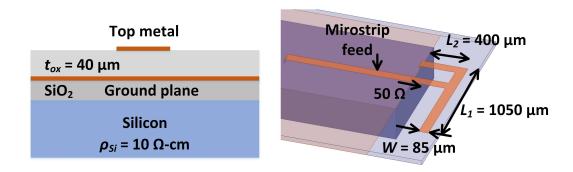

| 4.1  | Cross-section of the thick dielectric process technology to reduce on-chip               |    |

|      | radiation loss                                                                           | 56 |

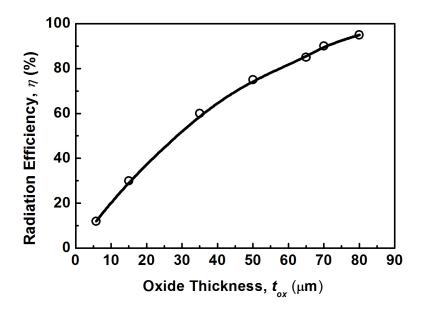

| 4.2  | The dependency of oxide thickness on the radiation efficiency                            | 57 |

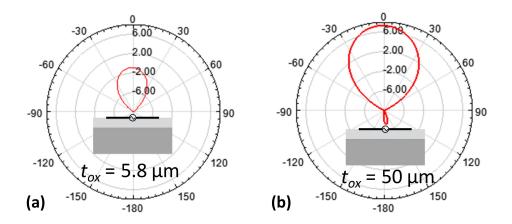

| 4.3  | Antenna radiation pattern at different oxide thickness                                   | 57 |

| 4.4  | Cross-sectional view and layout of an an-chip planar inverted-F (PIFA)                   |    |

|      | antenna                                                                                  | 58 |

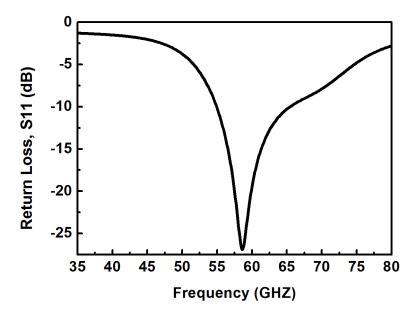

| 4.5  | Return loss (S11) of the PIFA antenna implemented on thick dielectric                 |    |

|------|---------------------------------------------------------------------------------------|----|

|      | process technology                                                                    | 58 |

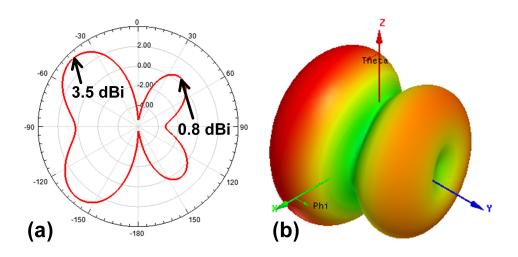

| 4.6  | Radiation pattern of on-chip PIFA antenna                                             | 59 |

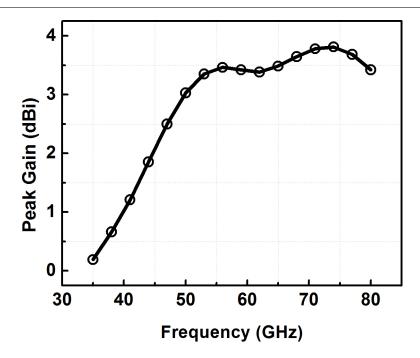

| 4.7  | Peak gain of PIFA antenna at frequency                                                | 60 |

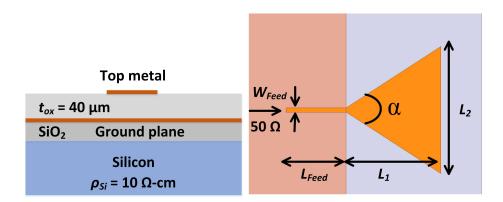

| 4.8  | Cross-sectional view and top view of a triangular monopole antenna im-                |    |

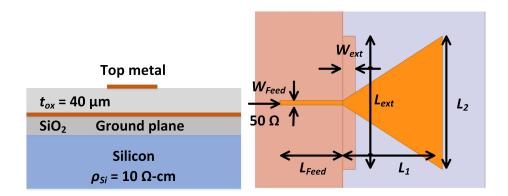

|      | plemented by thick dielectric porocess technology                                     | 61 |

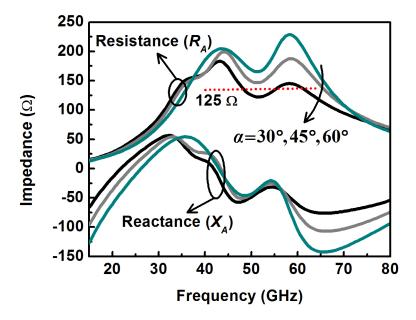

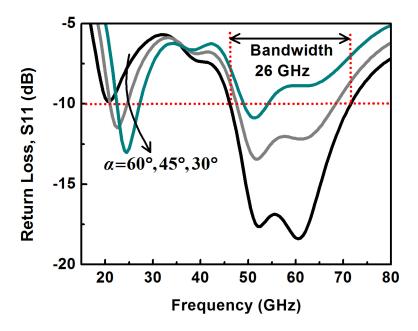

| 4.9  | Input impedance of a triangular moropole antenna with different flare                 |    |

|      | angles                                                                                | 61 |

| 4.10 | Return loss (S11) of the triangular monopole antenna at flare angle of $30^{\circ}$ , |    |

|      | $45^{\circ}$ and $60^{\circ}$                                                         | 62 |

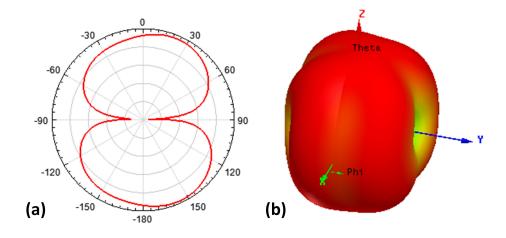

| 4.11 | Radiation pattern of micro-strip fed triangular monopole antenna                      | 62 |

| 4.12 | Cross-sectional and top view of a triangular sleeve monopole antenna                  | 63 |

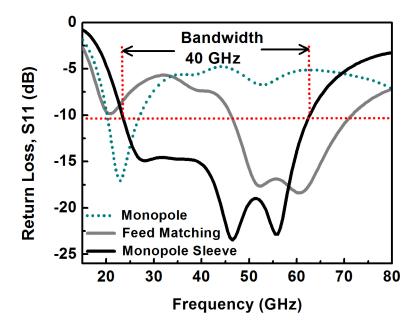

| 4.13 | Return loss (S11) triangular monopole antenna, monopole antenna with                  |    |

|      | quarter wave matching and triangular sleeve monopole antenna                          | 63 |

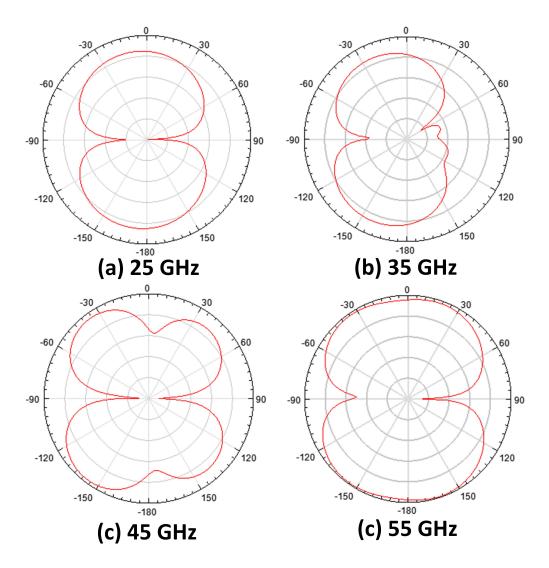

| 4.14 | Radiation pattern of the micro-strip fed triangular sleeve monopole an-               |    |

|      | tenna at different operation frequency                                                | 64 |

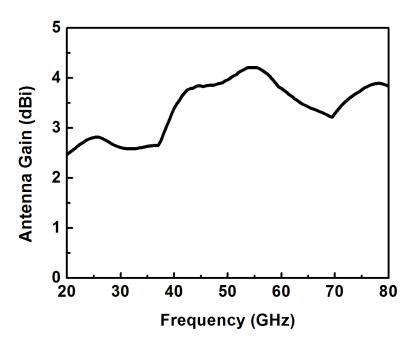

| 4.15 | Peak gain of the micro-strip fed triangular sleeve monopole antenna at                |    |

|      | different operation frequency                                                         | 65 |

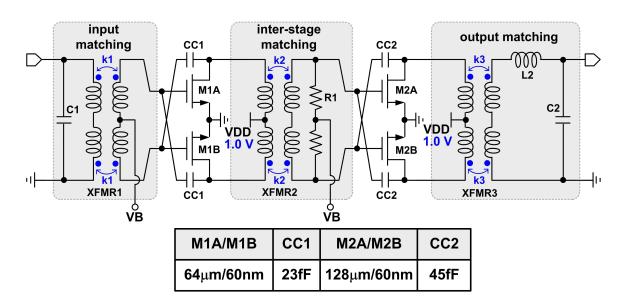

| 4.16 | The schematic diagram of a wideband power amplifier (PA) [18] for $5^{\rm th}$        |    |

|      | generation (5G) wireless system                                                       | 66 |

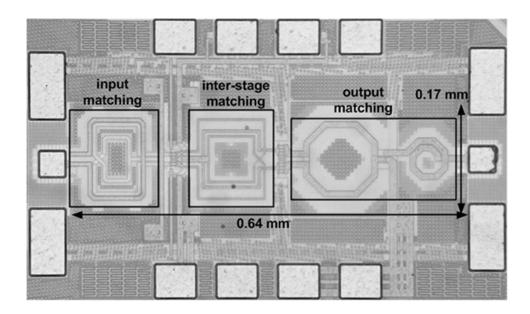

| 4.17 | The micrograph of the wideband power amplifier (PA), the core area of                 |    |

|      | which is $0.64 \times 0.17 \text{ mm}^2$ [18]                                         | 67 |

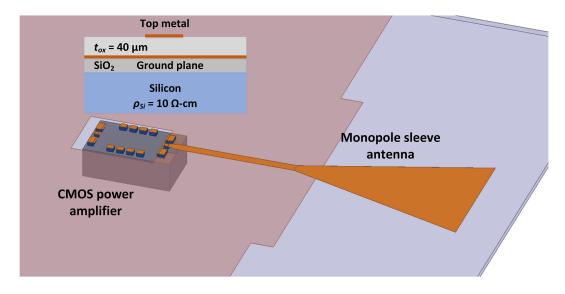

| 4.18 | Integration of a thick dielectric base chip antenna with a foundry fabricate          |    |

|      | IC                                                                                    | 67 |

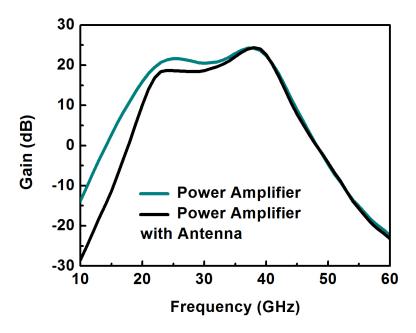

| 4 19 | The overall gain of the wide band power amplifier                                     | 68 |

# List of Tables

| 2.1 | Analytical parameters of elastic modulus for different pore morphologies. | 20 |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | Analytical parameters of shear modulus for different pore morphologies    | 21 |

| 3.1 | Design parameters of the on-chip wireless power supply system             | 45 |

### Integration of Low Loss Interconnects in CMOS

#### by Salahuddin Raju

The Department of Electronic and Computer Engineering

The Hong Kong University of Science and Technology

#### Abstract

In this work, an interlayer dielectric with an extremely low dielectric constant of 1.96 is achieved using  $SiO_2$  with vertically aligned cylindrical pores. Vertically grown carbon nanotubes are used as templates to form cylindrical pores to achieve high porosity while maintaining structural stability. Measurements show that an elastic modulus of 17.5 GPa can be maintained, even at 65% porosity, to provide sufficient mechanical strength for most back end of line (BEOL) processes. The tradeoff between the dielectric constant and elastic modulus for different porous structures has also been studied to project the ultimate achievable k-value.

A BEOL compatible thick dielectric and metal based interconnect, which eliminates the resistive and substrate eddy current loss from on-chip magnetics, is also proposed. Fully integrated on-chip inductors with up to  $200 \text{ nH/mm}^2$  inductance density and a peak quality factor of 25, were implemented based on the proposed interconnect technology, and a complete system for on-chip wireless power supply was implemented to demonstrate the integration capability. The  $2.5 \times 2.5 \text{ mm}^2$  wireless power receiver chip can harvest 27 mW power from a 250 mW transmitting power source at a distance of 5.3 mm, which is the best power harvesting capability compared to other reported technologies.

The thick dielectric interconnect technology is also proved to be useful to minimize the radiation loss of on-chip antennas. Several millimeter-wave antenna topologies are demonstrated utilizing this technology. An on-chip triangular sleeve monopole, which has a wide bandwidth from 23 GHz to 63 GHz, with 3.5 dB gain and efficiency of 98%, has been implemented. The antenna is integrated with a foundry fabricated wideband power amplifier IC. This demonstrates the efficacy of the proposed interconnect technology, which has applications ranging from power management to high-speed wireless data communication.

## Chapter 1

# Interconnect Challenges and

## Technology Requirements

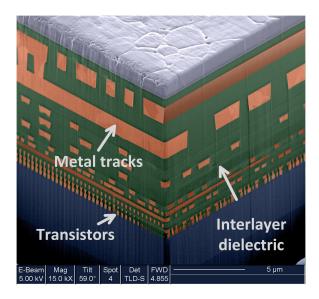

The task of interconnects is to connect active devices in a certain configuration to achieve a collective functionality. The interconnects consist of metal lines and contact plugs to route the electrical signal to its destination, as shown in Figure 1.1. The metal lines are arranged layer by layer buried inside dielectrics, and different layers of metal lines are connected via contact plugs. When signal travels through the metal lines, it encounters metal resistance, R, and capacitance from the dielectric, C, and signal become delayed. In advanced technologies, this RC delay became comparable to the delay from the active devices [1], [2]. Also there is certain amount of power is consumed during the process. In practice, it is desirable to make the interconnect with highest conductive metal buried inside a low dielectric, k, constant material. One of the best conducting metal, Copper, has already been adopted to the interconnects, but there is still room for improvement to achieve low-k.

Since, the advance interconnects are mainly optimized for digital electronics, it became inefficient for analog and RF applications, especially for integrated magnetics applications and on-chip radiation structures. This work is mainly focused on the strategies to achieve low-k, and efficient implantation of interconnects for magnetics and

radiating structures.

Figure 1.1: Cross-section of an interconnect structure (Courtesy of IBM).

### 1.1 Low-k Material Integration Challenges in BEOL

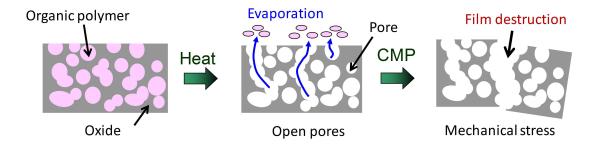

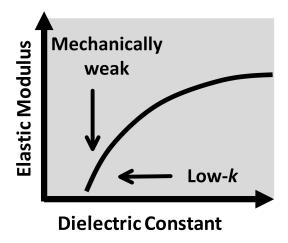

The international technology roadmap for semiconductors (ITRS) states that the effective k-value of 1.8–2.2 [2] will be required beyond 2024, but the manufacturable solution for such low-k ILDs are not known [3]–[5]. There is no solid material in nature exhibit such stringent k-value requirements. Most promising way of decreasing the k-value of a material is by introducing porosity. A typical way of porous dielectric implementation is described in Figure 1.2. To achieve such a low-k, more than 50% porosity will is required. However, there is an inverse relationship in between mechanical strength of the dielectric and the k-value, as described in Figure 1.3. The low-k material should satisfy some key requirements upon integration.

- Electrical: High breakdown strength, low loss tangent and low leakage.

- Mechanical: High elastic modulus, good adhesion between metal and other substrate.

- Chemical: Low moisture uptake.

• Thermal: Good thermal conductivity and high thermal stability.

Figure 1.2: Implementation of porous dielectric with spherical pores.

Figure 1.3: Inverse relationship between k-value and the elastic modulus of the porous dielectrics.

There is a complex interaction between pore morphology, porosity and the mechanical strength of the material. Conventionally, the porosity is introduced by using spherical pores (SP). The porous structure with SP reach its percolation threshold beyond 50% porosity, i.e. pores become interconnected. If any external force applied at this state, the material immediately collapses on itself; as a result the Young modulus (E) goes near zero as compared to the bulk. To overcome this barrier, this work presents a dielectric structure with vertically aligned cylindrical pores (VACP) is imprinted inside the bulk. Extremely low dielectric constant was achieved while surviving the stress during the chemical mechanical polishing (CMP). The reliability analysis upon electrical, thermal and mechanical stress was carried out, and the implication of such an ultralow-k

dielectric technology was investigated for high speed signal transmission.

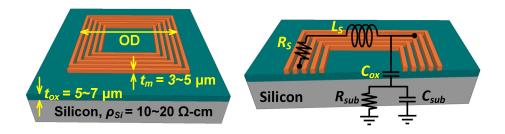

# 1.2 Benchmarking Interconnects for On-Chip Magnetics

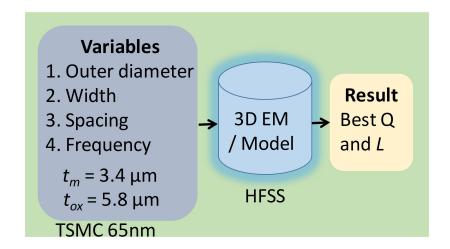

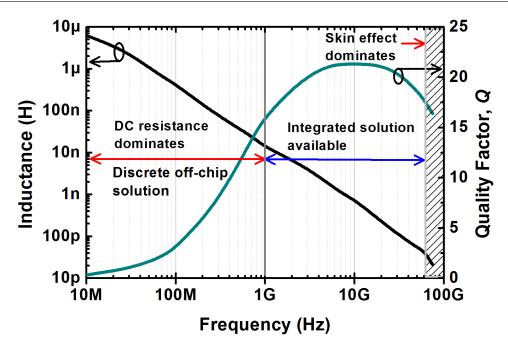

Efficient magnetic components are required for analog and RF applications. In some applications, passive discrete components take more space than the CMOS control IC itself. Integration of these passives into the control IC could reduce the overall size, and most importantly it would reduce the total solution cost. A theoretical benchmarking test was performed to evaluate the capability of magnetic integration, mainly inductor, in a particular foundry technology. To perform this test all interconnect layer information, including dielectric thickness, k-value and metal thickness were required. A typical crosssection of a on-chip inductor is shown in Figure 1.4. The main concern is to reduce the loss in the inductor. If the impedance of the inductance is defined as,  $Z_S = R_S + j\omega L$ , where  $R_S$  is the loss component and L is the value of inductance, the relative loss component can be quantified as  $Q = \omega L/R_S$ . Large quality factor, Q, indicates low loss in the inductor. A simulation platform, in Figure 1.5, was implemented for this benchmark. The TSMC 65 nm technology was used for this benchmark. All dielectric and metal layer information were inserted as fixed parameters. The outer diameter, metal width, metal spacing and operation frequency were the input variables of the benchmark. All fixed and input variables were inserted to an algorithm to create all possible inductor structures. The full 3D EM [6] simulation were performed to find out loss basic circuit parameters of those inductors. At a particular frequency, there was a best achievable inductor with highest Q value. At each operating frequency, extending from 10 MHz to 100 GHz, the highest Q-value inductors were extracted. The summary of the shown in

Figure 1.4: Cross-section of an inductor and its basic circuit parameters.

Figure 1.6. The highest possible Q-value and its corresponding inductance is shown in Figure 1.6. The results indicate that magnetic on TSMC 65 nm technology prove to be efficient in 1 GHz to 60 GHz. In low frequency range, the inductor becomes lossy even though large inductance value can be achieved. There is an interest of efficient inductors in such low frequencies, less than 1 GHz, especially in power management applications. It is evident that this is not possible in conventional CMOS interconnects. The conventional interconnects mainly consist of thin dialectic and metal (typically about several  $\mu$ m) on a low resistive (10–30  $\Omega$ -cm) silicon substrate. Due to small metal thickness, inductors suffer severe resistive loss. And for the thin dielectric, inductors suffer from substrate loss and low-self resonance frequency [7], [8]. In this work, an interconnect technology was proposed to eliminate such losses, and efficient on-chip magnetics were implemented in MHz frequency range.

Figure 1.5: Simulation platform of the benchmark test.

Figure 1.6: Highest possible Q-value at different frequency and its corresponding inductance.

# 1.3 Interconnect Non-Idealities for Electromagnetic Applications

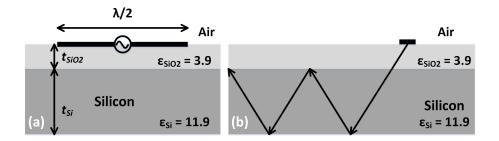

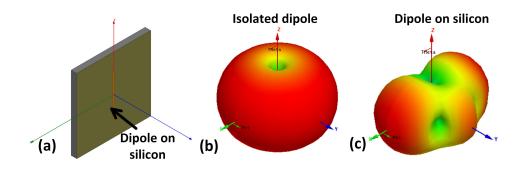

The electromagnetic radiation from CMOS interconnect is most inefficient. In terms of cost and system integration, it is preferable to have radiating antenna on silicon. Low silicon resistivity is one of the major prohibiting factor of such applications. Since the dielectric constant of the silicon is large, when an antenna radiates close to the silicon, the EM wave sucked inside the silicon and certain amount of power was dissipated inside the silicon due to its lossy nature, especially in millimeter-wave frequency range. This loss may have been eliminated by using high resistive SOI substrate. Secondly, due to its high permittivity the silicon substrate, there is a surface wave created inside the silicon, as shown in Figure 1.7. This has severe detrimental effect of the antenna radiation patterns. As shown in Figure 1.8, radiation is uniformly spread out to the space from an isolated dipole. But when the diople implemented on silicon, it creates an undesirable radiation pattern, also its efficiency reduces.

Figure 1.7: Antenna radiation (a) and surface wave mode (b) in silicon.

Figure 1.8: The radiation pattern of a dipole on silicon at 60 GHz.

This work proposed a interconnect technology to eliminate such radiation losses. Several antenna topologies were implemented. Effectiveness of the technology was also demonstrate by imhementing a broadband wireless data communication system.

### 1.4 References

- [1] A. Grill, S. M. Gates, T. E. Ryan, S. V. Nguyen, and D. Priyadarshini, "Progress in the development and understanding of advanced low-k and ultralow-k dielectrics for very large-scale integrated interconnects State of the art," *Applied Physics Reviews*, vol. 01, pp. 011306 (1–17), Jan. 2014.

- [2] International Technology Roadmap for Semiconductors (ITRS)-Interconnect, available at http://www.itrs.net/.

- [3] K. Maex, M. R. Baklanov, D. Shamiryan, F. lacopi, S. H. Brongersma, and Z. S. Yanovitskaya, "Low dielectric constant materials for microelectronics," *Journal of Applied Physics*, vol. 93, no. 11, pp. 8793–8841, June 2003.

- [4] W. Volksen, R. D. Miller, and G. Dubois, "Low dielectric constant materials," *Chemical Review*, vol. 110, no. 01, pp. 56–110, 2010.

- [5] B. Lee, Y. Hee Park, Y. T. Hwang, W. Oh, J. Yoon, and M. Ree, "Ultralow-k nanoporous organosilicate dielectric lms imprinted with dendritic spheres," *Nature Materials*, vol. 04, pp. 147–151, Jan 2005.

- [6] High Frequency Structure Simulator (HFSS), www.ansys.com.

- [7] C. P. Yue, and S. S. Wong, "Physical modeling of spiral inductors on silicon," *IEEE Transaction of Electron Devices*, Vol. 47, No.3, pp. 560–568, March 2000.

- [8] J. N. Burghartz, "Progress in RF Inductors on Silicon-Understanding Substrate Losses," IEEE International Electron Device Meeting (IEDM), pp. 523–526, 1998.

## Chapter 2

## Nanotube Assisted Ultralow-k

## **Dielectrics**

As the feature size in integrated circuits continues to scale down according to Moores law, reducing the dielectric constant (or k-value) of interlayer dielectric (ILD) becomes important [1] for minimizing propagation delay and dynamic power consumption in the back-end-of-line (BEOL). The international technology roadmap for semiconductors (ITRS) states that the effective k-value of 1.8–2.2 [2] will be required beyond 2024, but the manufacturable solution for such low-k ILDs are not known [3]–[5]. There is no solid material in nature exhibit such stringent k-value requirements. Most promising way of decreasing the k-value of a material is by introducing porosity. According to Maxwell-Garnett effective medium approximation, more than 50% porosity is required to achieve k-value less than 2.2 using typical silicon dioxide dielectric [6]–[9]. At this porosity, the pores become entirely interconnected, and such porous material does not survive upon integration due to its weak mechanical strength [10], [11]. To satisfy the manufacturing requirements of BEOL, relatively hard dielectric is required with an elastic modulus larger than 3 GPa.

In this chapter, a dielectric structure with vertically aligned cylindrical pores (VACP) is proposed to achieve high porosity while maintaining high mechanical strength.

The fabrication process, experimental characterization and effectiveness of cylindrical pore morphology will be described.

# 2.1 Formation of Nanotube Assisted Vertically Aligned Cylindrical Pores

The mechanical structure has a strong impact on the achievable porosity. As shown in Figure 2.1(a), the most common spherical porous (SP) structure reaches its percolation threshold beyond 50% porosity. After the percolation threshold, multiple pores become interconnected to form voids. Such a structure is mechanically unstable and will collapse with the application of small external force. It is due to the significant reduction of the elastic modulus (E). For VACP, even though the pores reach the percolation threshold as shown in Figure 2.1(b), there is always some fraction of the solid material directly opposing the stress of the applied force. Therefore, the displacement upon the external force is less, leading to a high E of the structured material.

The formation process of the VACP structure is illustrated in Figure 2.2. The process starts with a supporting substrate, it can be semiconductor, dielectric or metal. Then, nanotubes were grown on top of the supporting substrate, as shown in Figure

Figure 2.1: Dielectric films with spherical (a) and vertically aligned cylindrical pores (b) geometries with  $\approx 50\%$  porosity.

Figure 2.2: Formation process of vertically aligned cylindrical pores in dielectric assisted by vertically aligned nanotubes. (a) CNT growth on a substrate, (b) Desired oxide deposition, and (c) Chemical mechanical polishing (CMP) and CNT removal by  $O_2$  plasma.

2.2(a). These nanotubes serve as templates of the cylindrical pores, and the diameter of the nanotubes are directly translated into the pore diameter. The empty space among nanotubes are filled with dielectric, as shown in Figure 2.2(b). In the following step, chemical mechanical polishing (CMP) is being done to planarize the surface. The top tip of the nanotubes would be exposed after CMP. The polishing time may need to be extended to expose all nanotube tips. The nanotubes are removed depending on their conductivity. If the insulating nanotubes are used, such as boron nitride (BN) nanotubes, it can be left inside the dielectrics. On the other hand, if the nanotubes are semiconducting or metallic, such as carbon nanotubes (CNT), it should be removed to obtain VACP dielectric, as shown in Figure 2.2(c).

The porosity in the material defined by the fraction of voids over the total volume. In VACP structure, the porosity, P, depends on the nanotube density  $(N_D)$  and the diameter of the tubes  $(d_{avg})$ , and the relationship can be described as,

$$P = \pi \left(\frac{d_{avg}}{2}\right)^2 N_D. \tag{2.1}$$

The void fraction in VACP structure is determined by the volume occupied by the nanotubes. A high density of nanotubes would be desirable to have highly porous dielectric.

For demonstration of VACP dielectrics, CNTs were used as templates, since it can be grown vertically aligned, density can be more than 10<sup>11</sup> tubes/cm<sup>2</sup> [12], and most importantly, it can be synthesized at low temperature ( $\leq 450^{\circ}$  C) [13]. Starting with the first metal layer for which Ti had been chosen in our process, vertically aligned CNTs were grown using Nickel catalyst. About 2 nm Nickel was deposited using evaporation method. The whole wafer was then loaded inside the plasma enhanced chemical vapor deposition (PECVD) chamber, and kept in vacuum for 10 min to eliminate any ambient gas. To form the nanoparticles, the catalyst film was annealed at 450° C with  $H_2$  :  $N_2$  = 3: 1 at 2.8 Torr for 10 min. Then, 200 W RF plasma was introduced along with 35 sscm CH<sub>4</sub> to grow vertically aligned CNTs. The length of the CNT was controlled by the CH<sub>4</sub> plasma exposure time. The CNT height was about 1  $\mu$ m. The temperature ramp up and ramp down were 100° C/min and 22° C/min, respectively. This operating condition is compatible to CMOS process and the temperature budget can further optimized such as that described in [14]. Under this condition, most CNTs were multiwall, the diameters were between 20 nm to 30 nm ( $d_{avg}$  was about 25 nm), and the density of the tubes was about  $1.1 \times 10^{11}$  tubes/cm<sup>2</sup>. According to the Equation 2.1, about 54% porosity was expected. A layer of SiO<sub>2</sub> (or any other desirable dielectrics) is deposited by chemical vapor deposition to cover the CNTs [15]. The film was then partially polished to about 385 nm thick. More than half of the film was polished away to ensure all top ends of the CNTs are exposed. After carefully washing the wafer, it was kept in a vacuum oven at 110° C about an hour to remove any residual moisture. After the baking process, the wafer was immediately loaded into the O<sub>2</sub> plasma chamber. High power O<sub>2</sub> plasma was used to completely remove the CNTs leaving the VACP at the dielectrics as shown in Figure 2.3. The CNT etching and capping layer deposition were done consecutively to prevent any contaminant deposition and absorption in the pores. A thin layer of SiO<sub>2</sub> around 45 nm was then deposited to cap the VACP dielectrics. The top metal layer used in our process was formed by Ti/Au for capacitance measurement. The processing

Figure 2.3: Formation process of vertically aligned cylindrical pores in dielectric assisted by vertically aligned nanotubes. (a) CNT growth on a substrate, (b) Desired oxide deposition, and (c) Chemical mechanical polishing (CMP) and CNT removal by  $O_2$  plasma.

conditions in our experiment have not been optimized and fine-tuning is possible. The size of the pores can be controlled by the conditions of CNT growth. The temperature for CNT growth can also be reduced using other processes that can be applied at lower temperature such as that reported in [16]. At this stage, only a proof of concept is achieved. For implementation of VACP dielectric in advanced BEOL, small pore diameter, about 1 5 nm [4], would be required, which can be achieve by using vertically aligned single walled CNTs [13] as templates. In addition, CNTs need to be grown on top of dielectric with tip-growth mode [14], so that all nanoparticles remain at the top end of the CNTs. Later on, these nanoparticles would be removed during the polishing step. This will prevent any shorting between adjacent metals in the same level.

Capacitors with an area of  $150 \times 150 \ \mu\text{m}^2$  were designed with SiO<sub>2</sub> containing the VACP as the dielectric. The measured capacitance is ranging from 0.889 pF to 0.945 pF. There was no DC bias (from -2 to +2 V) dependency observed in the measurement as shown in Figure 2.4. From the capacitance, we can extract the effective dielectric constant which is found to be in between 1.92 and 2.04. To check the reproducibility of the VACP dielectric, multiple samples were prepared and capacitance measurements were performed in various locations on those samples. The cumulative probabilities of dielectric constant are shown in Figure 2.5. The average dielectric constant was about 1.96.

Figure 2.4: Capacitance measurement at different bias voltages.

The variation in the dielectric constant is mainly attributed to the nanotube density during the growth.

Figure 2.5: Cumulative probability of measured dielectric constants.

Figure 2.6: (a) Load versus displacement curve for a elastic material, the loading is followed by elastic unloading process. (b) Cross-section of indenter and sample interaction during loading and unloading indicating quantities used for analysis.

# 2.2 Improved Mechanical Properties of the Dielectric Through VACP

The elastic modulus of the VACP dielectric was characterized through nanoindentation experiment. The nanoindentation experiment involves application of force though diamond indenter on a desired sample. The force measured as a function of the depth during loading of the indenter. This represents the resistance of the sample to both plastic and elastic deformation. The applied force decreases during unloading of the indenter. The force versus the depth during unloading defines the sample's stiffness. Figure 2.6(a) shows a typical displacement curve during loading and unloading of an indenter. The applied load P and depth of penetration h into the sample are continuously monitored by the test equipment. The sample hardness, H and reduced elastic modulus  $E_r$  can be calculated from this load versus displacement curve. However, several critical information need to be evaluated for to extract those information, most importantly the projected contact area, A. A typical cross-section of an indentation shown in Figure 2.6(b). The contact penetration depth,  $h_c$ , is defined as

$$h_c = h_{max} - 0.75 \frac{P_{max}}{S}. (2.2)$$

The unloading stiffness is defined as  $S = \frac{dP}{dh}$ , as shown in Figure 2.6(a). Here,  $h_{max}$  is the indentation depth at the maximum applied force,  $P_{max}$ . The contact area is determine from the probe area function,  $A(h_c)$ , for a given  $h_c$ . The corrected area function can be expressed as sixth order polynomial function

$$A(h_c) = C_0 h_c^2 + C_1 h_c + C_2 h_c^{1/2} + C_3 h_c^{1/4} + C_4 h_c^{1/8} + C_5 h_c^{1/16}$$

(2.3)

where, the first coefficient,  $C_0$ , represent the ideal function of the indenter, it is 24.5 for a Berkovich indenter. To determine all the coefficient of the area function, a series of indentations are performed a various contact depth on a sample of known elastic modulus. Typically fused quartz is used for this calibration. Then coefficients were numerically fitted to obtain complete corrected area function. The hardness calculate as

$$H = \frac{Pmax}{A(h_c)}. (2.4)$$

The reduced modulus is calculated as

$$E_r = \frac{S\sqrt{\pi}}{2\sqrt{A(h_c)}}. (2.5)$$

To determine the elastic modulus of the sample,  $E_{sample}$ , the elastic modulus of the indenter,  $E_i$ , needs to be considered. The  $E_{sample}$  can be calculated as

$$E_{sample} = (1 - \nu_i^2) \left( \frac{1}{E_r} - \frac{(1 - \nu_i^2)}{E_i} \right)^{-1}.$$

(2.6)

Figure 2.7: Experimentally obtained load versus displacement curve during elastic modulus measurement of VACP dielectric by nanoindentation.

For a standard diamond indenter probe,  $E_i$  is about 1140 GPa and the Poisson's ratio,  $\nu_i$ , of the indenter is about 0.07.

The nanoindentation experiment was performed using Hysitron TriboIndenter, and a Berkovich type three sided pyramidal probe was used for indentation. The probe tip radius was about 150 nm. Because of this, minimum compliance of the indentation depth was about 40 nm. A large indentation depth (> 40 nm) was required for accurate contact area determination. However, it is advisable to limit the maximum indentation depth to one tenth of the film thickness for minimizing the substrate effect [13]. A thick, about 4  $\mu$ m, VACP dielectric was prepared for this measurement. The Figure 2.7 shows the load versus displacement during indentation. The penetration depth was up to 255 nm at a maximum load,  $P_{max}$ , of 2 mN. This load versus displacement data was directly translated into the elastic modulus. At his particular indentation test, the projected indentation area was about 1.25  $\mu$ m<sup>2</sup>.

The nanoindentation measurements have been carried out in several indentation

Figure 2.8: Experimentally obtained hardness of VACP dielectric at different indentation depths.

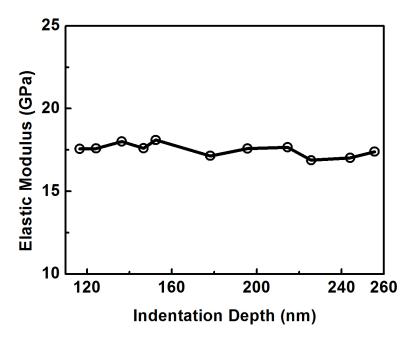

depths. The elastic modulus and hardness of the VACP dielectric was measured at various indentation depths. The hardness of VACP dielectric at different indentation depths is shown in Figure 2.8, and the elastic modulus measurement results shown in Figure 2.9. The hardness of the VACP dielectric varies between 1.23 GPa and 1.8 GPz, and the average hardness was about 1.58 GPa. The elastic modulus of the dielectric is ranging from 16.87 GPa to 18.10 GPa. The average elastic modulus of the VACP dielectric was about 17.5 GPa.

Two major contributing factors assisted this variations. The first cause was the surface roughness. It is a very important issue in nanoindentation test. Since the contact area is measured indirectly from the penetration depth, the surface roughness causes measurement errors in determination of the projected area of contact between the indenter tip and the sample. Careful polishing was carried out during the formation of VACP dielectrics. However, there was variation in surface roughness among different samples. Besides, there was CNT density variation during growth. Densely located VACP could weaken the dielectric and sparsely populated VACP could strengthen dielectric form the

Figure 2.9: Experimentally obtained elastic modulus of VACP dielectric at different indentation depths.

nominal value. However, the variation elastic modulus were limited to 10% from the nominal value.

# 2.3 Impact of Pore Morphology on the Material Characteristics

It is important to understand how the mechanical and electrical properties of the material vary with porosity and their pore morphology. The overall mechanical properties of porous low-k dielectrics are determined by the properties of the solid matrix and the pore morphology. That's why, the successful integration of porous dielectric requires a detailed understanding of how the mechanical stability of porous dielectric varies with porosity and pore microstructures. Although significant advancement has been made toward porous dielectrics, there is still relatively little fundamental understanding of the impact of pore morphology on the mechanical properties of porous low-k dielectrics. In this section, theoretical studies have been carried out to model the effects of porosity on

the elastic and dielectric properties of materials.

The impact of pore morphology was investigated by comparing the mechanical and electrical properties using 3D finite element (FE) simulation [16]. As inputs of FE simulation, two different kinds of pore morphologies were used. These two pore morphologies are vertically aligned cylindrical pore (VACP) and spherical pores (SP). For the geometric models, a Cartesian coordinate was used. The pores were assumed to be uniformly and randomly distributed in the structure. The representative volume element approach was used to model the porous microstructures with different pore morphologies. The FE simulation was performed using COMSOL multiphysics sofware.

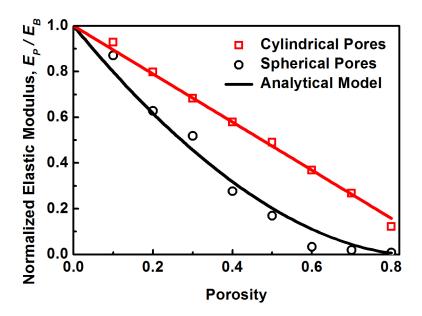

From the FE simulation results, an analytical relationship has been established between bulk elastic modulus  $E_B$  and elastic modulus  $E_P$  at a specific porosity. The relationship is described as,

$$\frac{E_P}{E_B} = \left(1 - \frac{P}{P_c}\right)^n. \tag{2.7}$$

Here, porosity value is defined as P,  $P_c$  is the porosity at which effective elastic modulus of the microstructure becomes zero, and n is the parameter dependent on the pore morphology. It is desirable to have small n, close to one, for a particular pore morphology. For a large value of n, effective modulus decreases sharply along with the porosity.

Table 2.1: Analytical parameters of elastic modulus for different pore morphologies.

| Pore Morphology | n   | $P_c$ |

|-----------------|-----|-------|

| Spherical Pores | 1.8 | 0.85  |

| VACP            | 1   | 0.95  |

The FE simulation of the microstructure at different porosity is summarized along with the analytical results in Figure 2.10. Analytical parameters for different pore morphologies have been extracted, which are shown in Table 2.1. The n value was found to be one, which indicates that in VACP elastic modulus decreases linearly with increasing porosity. Where as in spherical pores, the elastic modulus decreases sharply

Figure 2.10: Normalized elastic modulus  $(E_P/E_B)$  as a function of porosity. Here,  $E_B$  is the elastic modulus of bulk dielectric.

with increasing porosity. For SP dielectric, the effective modulus practically vanishes at 80% porosity.

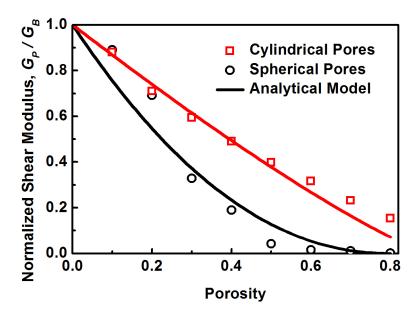

Table 2.2: Analytical parameters of shear modulus for different pore morphologies.

| Pore Morphology | n   | $P_c$ |

|-----------------|-----|-------|

| Spherical Pores | 2.2 | 0.8   |

| VACP            | 1.1 | 0.9   |

The FE simulation is also performed to evaluate shear modulus,  $G_P$ , at different porosity. Figure 2.11 shows the behavior of shear modulus at different porosity. The analytical model was also calibrated to describe nature of shear modulus behavior with porosity. The results are described in Table 2.2. The shear modulus in SP dielectric becomes zero at 80% porosity, and deteriorate sharply with increasing porosity. On the other hand, in VACP dielectric, the shear modulus shows a linear decrements (n value was about 1.1) with porosity. Even 80% porosity would be achievable at a considerably large shear modulus.

The overall dielectric property of porous film depends on the solid matrix and the pore morphology. That's why it is important to understand how the dielectric constant

Figure 2.11: Normalized shear modulus  $(G_P/G_B)$  as a function of porosity. Here,  $G_B$  is the elastic modulus of bulk dielectric.

varies with porosity and the pore morphology. An effective medium approximation is the simplest way of investigating phenomena. The Maxwell Garnett approximation gives the functional description the composite dielectric constant. The dielectric constant of host matrix was assumed to be  $k_B$ . If the host matrix is diluted with another material, whose dielectric constant is  $k_1$ , the original dielectric constant of the host matrix will be changed according to the and the dilute volume fraction,  $\delta$ . The effective dielectric constant, k, will be,

$$k = k_B \frac{k_1(1+2\delta) - k_B(2\delta-2)}{k_B(2+\delta) + k_1(1-\delta)}.$$

(2.8)

For a porous material with spherical pores, the value of  $k_1$  would be 1 and volume fraction would be represented by porosity P. The simplified effective dielectric constant would be

$$k = k_B \frac{(1+2P) - k_B(2P-2)}{k_B(2+P) + (1-P)}. (2.9)$$

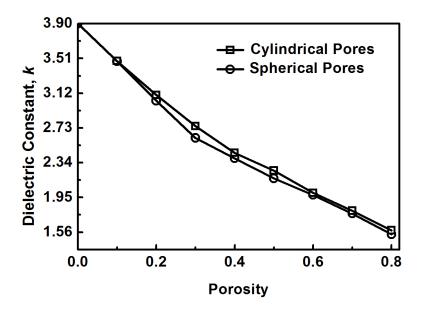

However, this effective medium theory could not be extended for cylindrical pores, i.e. VACP dielectrics. Compete FE treatment would be required to evaluate the effect of pore morphology on the dielectric constant of the microstructure. Figure 2.12 describes the

Figure 2.12: Impact on porosity and pore morphology on the dielectric constant of SiO<sub>2</sub>.

impact of porosity and pore morphology on the  $SiO_2$  dielectric. The dielectric constant of both cylindrical and spherical pore decreases similarly with the increase of porosity. The decrements of dielectric constant is slightly sharper than cylindrical pores. This is due to series parallel connection of pores in the SP dielectrics. However, the difference is not significant.

Figure 2.13: Impact of an external stress on the dielectric constant at different porosity and pore morphology.

Figure 2.14: Comparison of VACP dielectric with other reported technologies. And the theoretical (elastic modulus and dielectric constant upon different pore morphologies) and measured elastic modulus as a function of dielectric constant.

From the measured k-value, we estimated the porosity achieved by the VACP is about 65%. Simulation result shows that VACP structure is capable of maintaining an acceptable E, equivalent to 30% of its bulk moduli  $(E_B)$  at this porosity, and experimentally it was to be found about 17.5 GPa. Whereas at the same porosity level, the elastic modulus,  $E_P$ , in SP dielectrics became less than 3 GPa. The impact of the pore morphology on the permittivity is shown in Figure 2.12. The k-value of both structures decreases with porosity in a similar manner. In such case, the VACP can structurally enhance the value  $E_P$  at the same value of k. As an example, SiO<sub>2</sub> having VACP structure with k = 1.6 and  $E_P = 8$  GPa is feasible at a porosity of 80%.

The applied stress during processing, chemical mechanical polishing (CMP) and packaging, squeezes the porous material and increases the effective k value. This effect grows exponentially with the increased porosity as shown in Figure 2.13. The VACP structure can relief the impact of post-processing stress due to its low displacement. As an example, the typical 50 KPa stress in a CMP processing can increase the k value by

$3 \times 10^{-4}$  in 60% SP porous dielectrics on a 100 mm wafer. The increment in the VACP dielectrics is merely  $2.7 \times 10^{-5}$  as shown in Figure 2.13. Clearly the mechanical stability of the VACP dielectrics is better than SP dielectrics.

It is desirable to have large elastic modulus for any porous low-k material to sustain the manufacturing stress. Thats why it serves as a key metric for fair comparison among different porous material technologies. The elastic modulus and k value were compared with different types of low-k materials, as shown in Figure 2.14. In leading technologies [7], [17] – [25], elastic modulus always remains less than 5 GPa when the k-value is less than 2. The elastic modulus of the VACP dielectric is up to 17.5 GPa at a k-value of 1.96, clearly in terms of mechanical stability the VACP dielectrics is better than any other reported technologies.

Figure 2.15: Leakage current in VACP dielectric at different applied electric field.

### 2.4 Reliability of Ultralow-k Porous Dielectrics

Ideally, a dielectric should be a perfect insulator. But in reality, it has finite resistivity and allows to leak current through the dielectric at certain applied voltage. That's why any dielectric system, the leakage behavior and dielectric strength needs

to be investigated. The leakage behavior and dielectric strength of VACP dielectric is shown in Figure 2.15. The hollow pores act as defective trap sites in the material that enhances the breakdown process and reduces the breakdown field [9]. The defect site concentration of VACP dielectric should follow the density of the CNTs, as they are used as templates. Due to such large defect density, the effective dielectric strength of the material is reduced to about 0.7 MV/cm as shown in Figure 2.15. The temperature dependence of the breakdown field is shown in Figure 2.16. The breakdown voltage deteriorates with at increased temperature.

Figure 2.16: The temperature dependency of the dielectric breakdown field.

The temperature dependence of the dielectric constant is shown in Figure 2.17. This measurement was done to investigate the moisture uptake in the VACP dielectric. Due to the high dielectric constant of water (about 80), a small amount of water adsorption could signicantly increase the effective k-value. At a high temperature, trapped water molecules in the pores are expelled and the effective k-value drops. The measured reduction of k-value is less than 30% indicating the pores were well sealed with only minor opening for absorption of ambient moisture [3]. The impact of the external stress on capacitance was also investigated and the results indicated that capacitance

Figure 2.17: Measured capacitance at different temperatures, impact on moisture uptake.

increases with the increment of the stress as shown in Figure 2.18. It was observed that the capacitance increased by 0.045% for a stress of 17.65 MPa, equivalent to 0.46 nm displacement suggesting that the elastic modulus of the dielectric was 12.8 GPa, which is close to the observed value form the nanoindentation experiment.

Figure 2.18: The impact on capacitance upon different applied stresses.

Figure 2.19: Frequency response (S21) of 2 mm transmission lines in different dielectric system.

# 2.5 Signal Integrity Improvement Utilizing VACP Dielectrics

The direct advantage of using low-k dielectric can be observed by the frequency response of transmission lines fabricated on it. Mainly the transmission lines are capacitively coupled. Any reduction in dielectric constant would enhance the insertion and isolation capability of the transmission line. The insertion capability (i.e. propagation delay and loss) of a transmission line and the isolation capability of adjacent traces were measured and shown in Figure 2.19 and Figure 2.20. Indeed the measurements verified that the dielectric with VACP can reduce the insertion loss by 10 dB, and the isolation capability is improved by 2.2 dB compared with the non-porous structure.

Figure 2.20: Crosstalk response of 2 mm long adjacent traces upon different frequency.

### 2.6 Concluding Remarks on VACP Dielectrics

In this work, we have demonstrated an interlayer dielectric based on silicon dioxide with vertically aligned cylindrical pores (VACP) that achieved an ultralow k-value of 1.96. The vertically grown CNTs as an imprinting template provides a straightforward way of making this highly porous ultralow-k dielectric with improved stability in electrical and mechanical properties. The structure has been shown to be useful to reduce dynamic power consumption and signal propagation delay in the integrated circuits.

#### 2.7 References

[1] A. Grill, S. M. Gates, T. E. Ryan, S. V. Nguyen, and D. Priyadarshini, "Progress in the development and understanding of advanced low-k and ultralow-k dielectrics for very large-scale integrated interconnects - State of the art," *Applied Physics Reviews*, vol. 01, pp. 011306 (1–17), Jan. 2014.

- [2] International Technology Roadmap for Semiconductors (ITRS)-Interconnect, available at http://www.itrs.net/.

- [3] K. Maex, M. R. Baklanov, D. Shamiryan, F. lacopi, S. H. Brongersma, and Z. S. Yanovitskaya, "Low dielectric constant materials for microelectronics," *Journal of Applied Physics*, vol. 93, no. 11, pp. 8793–8841, June 2003.

- [4] W. Volksen, R. D. Miller, and G. Dubois, "Low dielectric constant materials," *Chemical Review*, vol. 110, no. 01, pp. 56–110, 2010.

- [5] B. Lee, Y. Hee Park, Y. T. Hwang, W. Oh, J. Yoon, and M. Ree, "Ultralow-k nanoporous organosilicate dielectric lms imprinted with dendritic spheres," *Nature Materials*, vol. 04, pp. 147–151, Jan 2005.

- [6] J. Liu, et al., "Porosity effect on the dielectric constant and thermomechanical properties of organosilicate lms," Applied Physics Letters, vol.81, no. 22, pp. 4180– 4182, Nov. 2002.

- [7] H. Miyoshi, et al., "Theoretical Analysis of Elastic Modulus and Dielectric Constant for Low-k two-dimensional periodic porous silica films," Japanese Journal of Applied Physics, vol. 43, no. 2, pp. 498–503, Feb. 2004.

- [8] D. J. Michalaka1, et al., "Porosity scaling strategies for low-k lms," Journal of Marials Research, vol. 30, no. 22, pp. 3363–3385, Nov. 2015.

- [9] A. Palov, T V. Rakhimova, M. B. Krishtab, and M. R. Baklanov, "Dependence of dielectric constant of SiOCH low-k films on porosity and pore size," *Journal of Vacuum Science and Technology B*, vol. 33, pp. 020603 (1–3), Jan. 2015.

- [10] G. Stan, et al., "Mechanical property changes in porous low-k dielectric thin films during processing," *Applied Physics Letters*, vol. 105, pp. 152906 (1–4), Oct. 2014.

- [11] S. Kondo, et al., "Low-pressure CMP for 300-mm ultra-low-k (k=1.6-1.8)/Cu integration," IEEE International Electron Device Meeting (IEDM), pp. 151–154, 2003.

- [12] J. Yang, et al., "Growth of high-density carbon nanotube forests on conductive

- TiSiN supports," Applied Physics Letters, vol. 106, pp. 083108 (1–5), Feb. 2015.

- [13] H. Sugime, et al., "Low-temperature growth of carbon nanotube forests consisting of tubes with narrow inner spacing using Co/Al/Mo catalyst on conductive supports," Applied Materials and Interfaces, vol. 07, pp. 16819–16827, 2015.

- [14] S. Hofmann, G. Csanyi, A. C. Ferrari, M. C. Payne, and J. Robertson, "Surface diffusion: the low activation energy path for nanotube growth," *Physical Review Letters*, vol. 95, pp.36101 (1–4), 2005.

- [15] J. K. Holt, H. G. Park, Y. Wang, M. Stadermann, A. B. Artyukhin, C. P. Grigoropoulos, A. Noy, and O. Bakajin, "Fast mass transport through sub-2-nanometer carbon nanotubes," *Science*, vol. 312, pp. 1034–1037, May 2006.

- [16] J. Li, Q. Ye, A. Cassell, H. T. Ng, R. Stevens, J. Han, and M. Meyyappan, "Bottom-up approach for carbon nanotube interconnects," *Applied Physics Letters*, vol. 82, no. 15, pp. 135–137, April 2003.

- [17] S. Hofmann, C. Ducati, J. Robertson, and B. Kleinsorge, "Low-temperature growth of carbon nanotubes by plasma-enhanced chemical vapor deposition," *Applied Physics Letters*, vol. 82, no. 01, pp. 135–137, July 2003.

- [18] J. C. Tan, T. D. Bennett, and A. K. Cheetham, "Chemical structure, network topology, and porosity effects on the mechanical properties of Zeolitic Imidazolate Frameworks," *Proceedings of the National Academy of Sciences*, vol. 107, no. 22, pp. 9938–9943, March 2010.

- [19] A. C. Fischer-Cripps, "Nanoindentation of thin films and small volumes of materials," in *Nanoindentation*, 3rd ed., New York: Springer, pp. 147–161, 2011.

- [20] Z. Chen, X. Wang, F. Giuliani, and A. Atkinson, "Microstructural characteristics and elastic modulus of porous solids," *Acta Materialia*, vol. 87, pp. 268–277, May 2015.

- [21] Y. Oku, et al., "Novel Self-Assembled Ultra-low-k porous silica films with high mechanical strength for 45 nm BEOL technology," *IEEE International Electron*

- Device Meeting (IEDM), pp. 139–142, 2003.

- [22] S. Chikaki, et al., "32 nm node ultralow-k (k = 2.1)/Cu damascene multilevel interconnect using high-porosity (50%) high-modulus (9 GPa) self-assembled porous silica," *IEEE International Electron Device Meeting (IEDM)*, pp. 969–972, 2007.

- [23] N. Oda, et al., "Comprehensive study of 32 nm node ultralow-k/Cu (keff=2.6) dual damascene integration featuring short TAT silylated porous silica (k = 2.1),"

IEEE International Electron Device Meeting (IEDM), pp. 1–4, Dec. 2008.

- [24] N. Oda, et al., "Total performance of 32-nm-node ultralow-k/Cu dual-damascene interconnects featuring short-TAT silylated porous silica (k = 2.1)," IEEE Transactions of Electron Devices, vol. 57, no. 11, pp. 2821–2830, Nov. 2010.

- [25] S. Eslava, et al., "Metal-Organic framework ZIF 8 films as low dielectrics in microelectronics," Chemistry of Materials, vol. 25, no. 01, pp. 27–33, 2013.

## Chapter 3

## **Engineered Interconnects with**

### Ultra-Thick Dielectric and Metal

In conventional interconnects, thin dielectric and metal is used due to its compact nature. This type of interconnects is highly suitable for digital circuitry. But, for analog and RF application it becomes a major sources of losses. To study this loss mechanism, on-chip inductors are most suitable circuit components. Inductors has a complex interaction among resistance, capacitance and inductance, and its losses are sensitive to the dimension of the used dielectric and metal. Typically, on-chip dielectric thickness is in between 10–15  $\mu$ m, maximum metal thickness is in the range of 3–5  $\mu$ m, and the silicon resistivity is about 10  $\Omega$ -cm. Due to small metal thickness, inductors suffer severe resistive loss, and for the thin dielectric devices suffer from substrate loss and low-self resonance frequency [1], [2]. Hence, in the conventional interconnects high performance magnetics can not be realized. Besides, any new proposal to overcome these barrier has to comply the CMOS compatibility issue. Mainly, it should take minimum number of steps, area minimization and temperature budget should limited to 200° C. Upon considering all these limitation, this work proposed a thick dielectric and metal processing technology. Eventually, using the proposed technology, large value inductors were fabricated and its practical applicability was also demonstrated.

Figure 3.1: Fabrication process of ultra-thick dielectric process for interconnects. (a) A sample IC with BEOL, (b) Spin coating of the thick dielectric, (c) Photolithography to remove material over the PAD, (d) Ti/W seed layer deposition, (e) Copper electroplating, and (f) Polishing to remove overburden copper.

# 3.1 BEOL Compatible Ultra-Thick Dielectric Processing

To suppress substrate loss due to low resistivity CMOS IC substrate [1], [2], a thick low-k polymer dielectric (SU8, k = 2.8) was placed on top of the BEOL of the IC. The detail fabrication process is described in Figure 3.1. At the begining of the process, the polymer (SU8) was spin coated on top of the passivation layer of the IC. The thickness of the dielectric can be controlled by the spin speed. The thickness of the material depends on the viscosity, which is determined by the vendor. Viscous polymer need to be chosen for thick dielectric. In this work, SU8 2050 was used for 50  $\mu$ m thick dielectric deposition. It is worth mentioning that the SU8 material is photo patternable.

After spin coating of polymer dielectric, photolithography was done to remove the dielectric on top of the PAD, as shown in Figure 3.1. At this stage, the dielectric remains soft and some portion of the solvent remain inside. Hard baking was done for one hour at 150° C to remove the solvent. After the baking, the dielectric became strong, the measured elastic modulus was about 2 GPa. The dielectric strength was about 11 MV/cm, which is comparable to the silicon dioxide. Then, a 50 nm Ti/W layer was deposited as seed layer for electroplating. The Ti/W was also worked as adhesion layer between copper and the dielectric. Then copper was deposited using electroplating, and the overburden copper was removed by chemical mechanical polishing in the following step. Thus, the ultra-thick dielectric layer was achieved on top the passivation layer of BEOL. This thick dialectic will serve as a base of further processing. It will prevent substrate loss in the electromagnetic device, and also reduce the capacitive coupling.

### 3.2 Ultra-Thick Interconnect Metal Processing

To achieve a thick metal layer, another layer of dielectric was spin coated on top the thick dielectric. Then, a lithography was done to pattern the the dielectric. The aspect ratio of photopatternable SU8 dielectric can be very high (greater than 10) [3]. The detail fabrication process is described in Figure 3.2. Since, these deep trench patterns served as templates for metal tracks, the thickness of the metal directly proportional to the height of the trenches. Then, the trenches were filled by electroplated copper and polishing was done to remove overburden copper. It is worth mentioning that the temperature did not exceed 150° C during all these processes. Figure 3.3 shows the cross section of the wafer before and after the polishing process. It also shows that the void-free copper filled trenches, which will render ideal copper resistance during application. This thick metal processing will reduce the DC resistive loss in inductors.

In terms of CMOS compatibility, simple process steps were used in these technology, which includes photolithography, metal sputtering, electroplating and chemical mechanical polishing. These are the standard processes used in conventional BEOL.

Total number required photolithography steps would be one to three, depending upon the design. Most importantly, the process temperature was limited to 150° C. All these satisfied criteria justified the CMOS compatibility of the proposed technology.

Figure 3.2: Fabrication steps of ultra-thick metal processing. (a) Deep trench patterns for thick metals, (b) Ti/W seed layer deposition for electroplating, (c) Copper electroplating, and (d) Overburden copper removal for thick metal tracks.

Figure 3.3: The cross-section of the wafer before (a) and after (b) the CMP process.

# 3.3 Engineered Interconnects for High Quality On-Chip Magnetics

Inductors were fabricated using above mentioned thick dielectric and metal processing. The micrograph of an inductor and its cross-section is shown in Figure 3.4(a). The dielectric thickness was about 50  $\mu$ m and the metal thickness was about 40  $\mu$ m. To

Figure 3.4: (a) The micrograph of a test-inductor and its cross-section. (b) Dummy PADs to mimic a CMOS chip configuration. (c) Integrated inductor.

demonstrate the CMOS integration capability, dummy PADs were created to mimic a CMOS die. When the inductor was fabricated on top of the IC, and the PADs were also raised in the process for external electrical connections, as shown in Figure 3.4(c).

# 3.3.1 Inductor Self-Resonance Frequency Improvement through Dielectric Engineering

Due to the thick dielectric in between the inductor metal tracks and the substrate, capacitance was reduced. The resonance frequency of the inductor was defined by  $f_r = 1/\sqrt{LC}$ . Here, L is the inductance value and C is the parasitic capacitance of the inductor. Due to the utilization of thick dielectric C is reduced, which contributed to the increased self-resonance frequency of the inductor. Multiple samples were prepared with different dielectric thicknesses. And the thickness dependency on self-resonance

frequency was studied. The measurement result is shown in Figure 3.5. When the dielectric thickness is 10  $\mu$ m, the self-resonance frequency was at 100 MHz. But, the self-resonance frequency exceeded 300 MHz, when the inductor fabricated on top of 40  $\mu$ m thick dielectric, as shown in Figure 3.5. Certainly, the self-resonance was improved due to the thick dielectric processing. The loss factor of the inductor is quantified by the quality factor, Q, quantitatively it is determined by  $\omega L/R_S$ , where the resistive loss is defined by  $R_S$ . The loss of the inductor is inversely proportional to the Q. At higher operating frequency the value of  $\omega L$  increases, but at the same  $R_S$  increases a bit due to the skin effect. The skin depth,  $\delta$ , of the metal is quantified by the operating frequency, f, and the conductivity,  $\sigma$ , of the metal. It is defined as  $\delta = \sqrt{2/2\pi f\mu\sigma}$ . If the skin depth is larger than the thickness of the metal tracks,  $R_S$  remains constant. In such a case, increase dielectric would be useful to reduce inductor loss. A benchmarking was performed to evaluate the improvement of the Q, as shown in Figure 3.6. The benchmarking was performed according to the TSMC 65 nm technology, in which top metal thickness was about 3.4  $\mu$ m. At low frequency range,  $R_S$  remains unaffected by the operating frequency. That's why the is slight improvement of Q in the range of 10 MHz to 1 GHz. But, when the skin depth approaches the thickness of the metal, at frequency larger that 1 GHz, there was no improvement of the Q due to thick dielectric process.

Figure 3.5: Improvement of self-resonance frequency due to thick dielectric.

Figure 3.6: Benchmarking of thick dielectric process for integrated magnetics.

### 3.3.2 Resistive Loss Reduction in On-Chip Magnetics

There were two fundamental resistive losses in the inductor. One is the eddy current loss in the substrate, and another is resistive loss in the metal, which is discussed earlier. The substrate loss can be reduced by placing the inductor far away from the

Figure 3.7: Improvement of indctor quality factor due to thick metal and dielectric.

substrate. By using the thick dielectrics, the substrate loss can be minimized. But the resistive loss will still be there due to thin metal. To minimize the resistive loss, thick metal processing technique was followed. For a low loss on-chip inductor both thick dielectric an metal process should be carried out. Figure 3.7 shows that the quality factor was improved five-fold due to the thick metal and dielectric processing. A benchmarking was also performed to show the theoretical effectiveness of the process, as shown in Figure 3.8. The benchmarking shows that significant improvement of Q due to the thick metal and dielectric process. Effectively, this process is minimizing all losses of the interconnects associated with the integrated magnetics.

Figure 3.8: Benchmarking of thick dielectric and metal process for integrated magnetics.