# Energy-Efficient CMOS Optical Receiver for Short-Reach Data Center Application

by

# **Chongyun ZHANG**

A Thesis Submitted to

The Hong Kong University of Science and Technology

In Partial Fulfillment of the Requirements for

The Degree of Doctor of Philosophy

in the Department of Electronic and Computer Engineering

July 2025, Hong Kong

## **Abstract**

Optical interconnects have been deployed in data centers to replace electrical interconnects, offering enhanced traffic capacity and reduced power consumption. As data center networks scale in bandwidth (BW) and physical size, the cost and power consumption of optical transceivers have risen significantly. Further scaling of energy efficiency and BW density remains challenging due to limited integration in optical modules. This thesis focuses on the design of energy-efficient CMOS four-level pulse amplitude modulation (PAM-4) optical receivers (ORXs) for short-reach data center applications.

Based on a simplified shunt feedback (SF) transimpedance amplifier (TIA) model, noise-BW relationship is first analyzed and derived. ORX sensitivity enhancement by the continuous-time linear equalizer (CTLE), the feed-forward equalizer (FFE), and the decision feedback equalizer (DFE) are analyzed and simulated. The derivations indicate that the CTLE reduces the thermal noise from the SF resistor, but it leaves the color noise unaffected. System-level simulations demonstrate sensitivity improvement through post-TIA equalizations.

A 48-Gb/s PAM-4 ORX data path, integrating a linear TIA and a sampler, is introduced. The TIA employs a transadmittance-stage transimpedance-stage (TAS-TIS) topology, replacing conventional variable gain amplifiers (VGA) and post-amplifiers based on current-mode logic, avoiding CTLEs and passive inductors while preserving the linearity and gain-BW product for PAM-4 operation. The sampler exploits a 2-tap FFE and a 2-tap DFE to improve sensitivity and ensure correct data recovery. Fabricated in a 28-nm CMOS process, the ORX demonstrates a -5.1-dBm sensitivity and 1.28-pJ/bit (0.27 pJ/bit for TIA alone) efficiency at 48-Gb/s PAM-4.

A 100-Gb/s PAM-4 TIA is designed to relax the tradeoffs between BW, noise, and power without compromising linearity. Inverter-based circuits are predominantly used across stages. A current reuse VGA employing a TAS-TIS topology with high linearity is proposed, offering a large tuning range with fine step size. Multi-layer stacked network, T-coils and inductors are employed to achieve high inductance density, expanding the overall BW despite the presence of ESD diodes at both input and output. Implemented in a 28-nm CMOS process, the TIA achieves a BW of 28 GHz, a dc transimpedance gain of 65 dB $\Omega$ , an input referred noise density of 16 pA/ $\sqrt{Hz}$ , a THD of less than 5% up to 640  $\mu$ App input current, and 0.32-pJ/bit efficiency.

## **Authorization**

I hereby declare that I am the sole author of the thesis.

I authorize the Hong Kong University of Science and Technology to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize the Hong Kong University of Science and Technology to reproduce the thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Chongyun Zhang

July 2025, Hong Kong

# **Energy-Efficient CMOS Optical Receiver for Short-Reach Data Center Application**

by

#### Chongyun ZHANG

This is to certify that I have examined the above PhD thesis and have found that it is complete and satisfactory in all respects, and that any and all revisions required by the thesis examination committee have been made.

Prof. C. Patrick YUE, Thesis Supervisor

Prof. Andrew Wing On POON, Head of ECE Department

#### **Thesis Examination Committee**

| 1. Prof. C. Patrick YUE (Supervisor)  | Department of Electronic and Computer Engineering |

|---------------------------------------|---------------------------------------------------|

| 2. Prof. Howard Cam LUONG             | Department of Electronic and Computer Engineering |

| 3. Prof. Man Hoi WONG                 | Department of Electronic and Computer Engineering |

| 4. Prof. Song GUO                     | Department of Computer Science and Technology     |

| 5. Prof. Chao WANG (External Examiner | School of Optical and Electronic Information,     |

|                                       | Huazhong University of Science and Technology     |

Department of Electronic and Computer Engineering

The Hong Kong University of Science and Technology

July 2025, Hong Kong

Tempus Fugit

## Acknowledgement

First, I would like to express my sincere gratitude to my supervisor, Prof. C. Patrick YUE, for his guidance, encouragement, and support through my research. He guided me into the world of integrated circuit design. Without his foresights and insights, I would never have finished the research work covered in this thesis. His enthusiasm for research, spirit for exploration, and expertise for academia have not only laid the foundations for my research experience but also shaped my academic character.

I would like to express my gratitude to Prof. Howard Cam LUONG, Prof. Man Hoi WONG, Prof. Song GUO, and Prof. Chao WANG for serving as my thesis examination committee members and providing valuable insights and suggestions to my research. I would also like to thank Prof. Wenjing YE for serving as the chairperson for my thesis defense.

I would like to thank Dr. Weimin SHI, Dr. Babar HUSSAIN, Dr. Rehan AZMAT, Dr. Fuzhan CHEN, and Mr. Sam Can WANG for their kind discussion and support in my research, especially during my initial days in the lab when I was unfamiliar with many things. I would like to have special thanks to Dr. Li WANG for his kind guidance and valuable discussion during these years.

I thank ECE lab technicians, Mr. Raymond WONG, Mr. Allen NG, Mr. Siu Fai LUK, and Mr. Kwok Wai CHAN (KW), for their technical support and help on chip-on-board bonding, tape-outs, and testing.

I thank my colleagues in the IC Design Center, including Mr. Jian KANG, Ms. Tianxin MIN, Ms. Xinyi LIU, Mr. Shaokang ZHAO, Mr. Matthew Ruitao MA, Mr. Johar ABDEKHODA, Mr. Dennis Jinyun LIU, Dr. Lin WANG, Dr. Bo XU, Dr. Zilu LIU, Dr. Yang GAO, Dr. Khoi PAN, Dr. Yi LIU, Dr. Yuan YAO, and Dr. Jeffry WICAKSANA, for all those shared experiences, challenges, discussions and collaborations. I also thank Dr. Jian YANG, Dr. Liping ZHONG, Mr. Zhenghao LI, Mr. Xuxu ZHONG, Mr. Yangyi ZHANG for providing help with the measurements in Shenzhen.

Finally, I would like to express my sincere appreciation to my family. Their encouragement and understanding gave me strength and confidence. In particular, I would like to thank my parents, for their unlimited support and love all the way.

# **Table of Contents**

| Title Page                                                          | i   |

|---------------------------------------------------------------------|-----|

| Abstract                                                            | ii  |

| Authorization Page                                                  | iii |

| Acknowledgement                                                     | vi  |

| Table of Contents                                                   | vii |

| List of Figures                                                     | ix  |

| List of Tables                                                      | xv  |

| Chapter 1 Introduction                                              | 1   |

| 1.1 Motivation                                                      | 1   |

| 1.2 Background                                                      | 3   |

| 1.3 Thesis Organization                                             | 5   |

| Chapter 2 Optical Receiver Sensitivity Enhancement by Equalization  | 7   |

| 2.1 Optical Receiver Equalization Techniques                        | 7   |

| 2.1.1 Continuous-Time Linear Equalizer (CTLE)                       | 7   |

| 2.1.2 Feed-Forward Equalizer (FFE)                                  | 9   |

| 2.1.3 Decision Feedback Equalizer (DFE)                             | 11  |

| 2.2 SF TIA Noise Analysis                                           | 14  |

| 2.3 Sensitivity Enhancement by Equalization                         | 17  |

| 2.3.1 CTLE-Equalized SF TIA                                         | 17  |

| 2.3.2 SF TIA with Post-TIA Equalization                             | 22  |

| Chapter 3 A 1.28-pJ/bit 48-Gb/s Inductorless PAM-4 Optical Receiver | 25  |

| 3.1 Overview                                                        | 25  |

| 3.2 System Architecture                                             | 27  |

| 3.3 Building Blocks                                                 | 29  |

| 3.3.1 PD Interface and TIS                                          | 29  |

| 3.3.2 VGA and Post-Amp.                                             | 31  |

| 3.3.3 Sampler with Integrated Equalizer                             | 36  |

| 3.3.4 Clock Buffer                                                  | 43  |

| 3.4 Measurement Results                          | 44 |

|--------------------------------------------------|----|

| 3.5 Conclusion                                   | 53 |

| Chapter 4 A 0.32-pJ/bit 100-Gb/s Linear TIA      | 54 |

| A 0.32-pJ/b 100-Gb/s PAM-4 Linear TIA            | 54 |

| 4.1 Overview                                     | 54 |

| 4.2 System Architecture                          | 59 |

| 4.3 Building Blocks                              | 61 |

| 4.3.1 TIS with Multi-peaking Network             | 61 |

| 4.3.2 CTLE and S2D                               | 62 |

| 4.3.3 VGA                                        | 64 |

| 4.3.4 Output Buffer                              | 67 |

| 4.3.5 COB and High-Frequency PCB                 | 70 |

| 4.4 Measurement Results                          | 72 |

| 4.4.1 Frequency Domain Measurement               | 73 |

| 4.4.2 Noise Measurement                          | 75 |

| 4.4.3 THD Measurement                            | 76 |

| 4.4.4 Time domain measurement                    | 77 |

| 4.5 Conclusion                                   | 81 |

| Chapter 5 Conclusion and Future Work             | 83 |

| 5.1 Summary                                      | 83 |

| 5.2 Future Work                                  | 84 |

| 5.2.1 Linearity Enhancement for PAM-4 TIA Design | 84 |

| 5.2.2 Transformer-Based Q Shaping                | 86 |

| Appendix A                                       | 88 |

| Appendix B                                       | 90 |

| Ribliography                                     | 02 |

# **List of Figures**

| Figure 1.1. Revenue in the data center market for different segments worldwide from 2022 to    |

|------------------------------------------------------------------------------------------------|

| 2029 (in billion U.S. dollars) [3]                                                             |

| Figure 1.2. (a) Illustration of the effect of linearity on PAM-4 eye diagrams. (b) Design      |

| tradeoffs with linearity taken into consideration                                              |

| Figure 1.3. System diagram of an IMDD optical interconnect                                     |

| Figure 1.4. (a) Retimed pluggable optics in which an ASIC is placed to a pluggable OE with a   |

| re-timer or DSP chip. (b) Co-packaged optics where the optical module is on the same substrate |

| as the ASIC. (c) Linear pluggable optics in which the OE is placed in a package near the ASIC, |

| and the re-timer/DSP is removed                                                                |

| Figure 1.5. (a) Front-panel transceivers implemented in SiGe BiCMOS and (b) integration of     |

| CMOS front-end transceivers with SerDes IC5                                                    |

| Figure 2.1. (a) Bode plot of a CTLE with one zero. (b) A CTLE circuit using resistive and      |

| capacitive degeneration in a differential pair                                                 |

| Figure 2.2. Pulse responses of a BW-limited signal and the CTLE-equalized signal               |

| Figure 2.3. Eye diagrams of the signal (a) before and (b) after equalized by the CTLE9         |

| Figure 2.4. Block diagram of a linear n-tap FFE                                                |

| Figure 2.5. Pulse responses of a BW-limited signal and the FFE-equalized signal                |

| Figure 2.6. Eye diagrams of the signal (a) before and (b) after equalized by the FFE 11        |

| Figure 2.7. Block diagram of a n-tap direct DFE.                                               |

| Figure 2.8. Block diagram of a 1-tap loop-unrolled DFE                                         |

| Figure 2.9. Pulse responses of a BW-limited signal and the DFE-equalized signal                |

| Figure 2.10. Eye diagrams of the signal (a) before and (b) after equalized by the DFE 13       |

| Figure 2.11. Illustration of noise contributions in SF TIA                                     |

| Figure 2.12. SF TIA (a) input referred current noise PSD, (b) magnitude frequency response,    |

| and (c) output voltage noise PSD                                                               |

| Figure 2.13. CTLE-equalized SF TIA design where a low-BW TIS is followed by a BW               |

| recovering CTLE                                                                                |

| Figure 2.14 Illustration of input-referred noise of a CTLF-equalized SETIA 18                  |

| Figure 2.15. Small-signal model of TIS for calculating the output noise                                   |

|-----------------------------------------------------------------------------------------------------------|

| Figure 2.16. Simulated SNR with different scaling factor <i>n</i>                                         |

| Figure 2.17. Simulated CTLE-equalized TIA responses under different Q values                              |

| Figure 2.18. Simulated SNR with different Q values. 21                                                    |

| Figure 2.19. ORX design with post-TIA equalizers.                                                         |

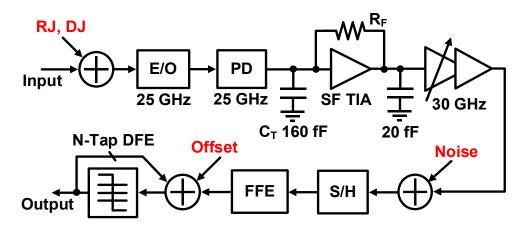

| Figure 2.20. ORX model used to evaluate post-TIA equalizations                                            |

| Figure 2.21. Simulated PAM-4 ORX sensitivity with different configurations of post-TIA                    |

| equalizations. 24                                                                                         |

| Figure 3.1. Integration of front-panel transceivers with SerDes circuits in a single CMOS IC.             |

|                                                                                                           |

| Figure 3.2. Integrated CMOS linear TIA and PAM-4 sampler with the FFE and the DFE 26                      |

| Figure 3.3. Block diagram of the proposed PAM-4 ORX architecture                                          |

| Figure 3.4. Block diagram of the proposed CMOS linear TIA                                                 |

| Figure 3.5. (a) Direct connection scheme where noise modulates the input signal. (b) On-chip              |

| connection scheme where noise is filtered and ac-coupled to VSS <sub>TIA</sub> . (c) Simulated conversion |

| gain from PD bias to TIA input. (d) Schematic of TIS and DCOC circuits                                    |

| Figure 3.6. Simulated gain and phase of the DCOC loop                                                     |

| Figure 3.7. (a) Schematic of a conventional Gilbert-cell-based VGA. (b) Simulated frequency               |

| responses of VGA with and without inductive shunt peaking                                                 |

| Figure 3.8. Schematic of a TAS-TIS topology-based VGA with its gain controlled by the                     |

| feedback resistor R <sub>F</sub> . 32                                                                     |

| Figure 3.9. Simulated frequency responses of the TAS-TIS VGA with different gain settings.                |

|                                                                                                           |

| Figure 3.10. Schematic of the proposed Gilbert-TIS VGA                                                    |

| Figure 3.11. Simulation results and comparison of frequency responses for three types of                  |

| VGAs                                                                                                      |

| Figure 3.12. Schematic of the post-amp                                                                    |

| Figure 3.13. Simulated responses of the entire linear TIA with max. and min. gain settings.35             |

| Figure 3.14. Layout of the TIA with DCOC circuits                                                         |

| Figure 3.15. Block diagram of the half-rate FFE and DFE                                                   |

| Figure 3.16. Schematic of (a) the S/H circuit and (b) the summer with FFE and DFE taps 37      |

|------------------------------------------------------------------------------------------------|

| Figure 3.17. Timing diagram for the pre-tap FFE and the first tap DFE in a half-rate design.   |

|                                                                                                |

| Figure 3.18. Schematic of the track-and-regenerate slicer                                      |

| Figure 3.19. Simulated large signal performance of the slicer at 15 GHz39                      |

| Figure 3.20. Monte Carlo simulation results of the slicer input offset                         |

| Figure 3.21. Block diagram of slicers with the calibration logic                               |

| Figure 3.22. Simulation result of (a) the calibration logic output and (b) the slicer output41 |

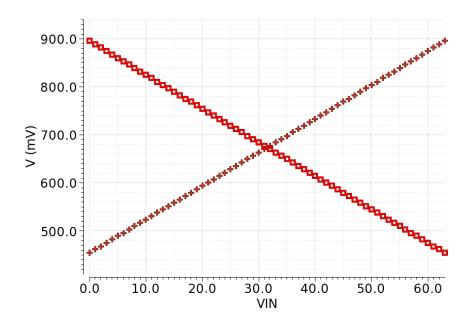

| Figure 3.23. DAC_cal output with different input control words                                 |

| Figure 3.24. Layout of the PAM-4 sampler                                                       |

| Figure 3.25. Simulated differential output at the summer (a) without equalization and (b) with |

| a 2-tap FFE and a 2-tap DFE                                                                    |

| Figure 3.26. Schematic of the CML-to-CMOS input clock buffer                                   |

| Figure 3.27. Block diagram of the clock divider and the voltage-controlled delay line 43       |

| Figure 3.28. Layout of the entire clock buffer                                                 |

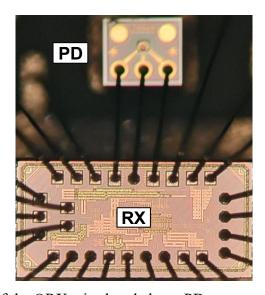

| Figure 3.29. Micrograph of the ORX                                                             |

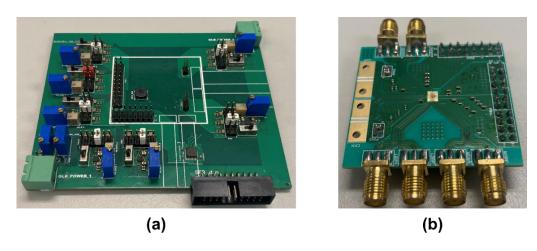

| Figure 3.30. (a) Power and control low-frequency PCB module. (b) Chip mounting high-           |

| frequency PCB module                                                                           |

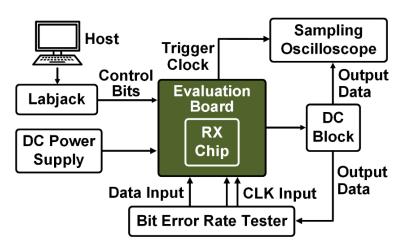

| Figure 3.31. Electrical measurement setup for the ORX                                          |

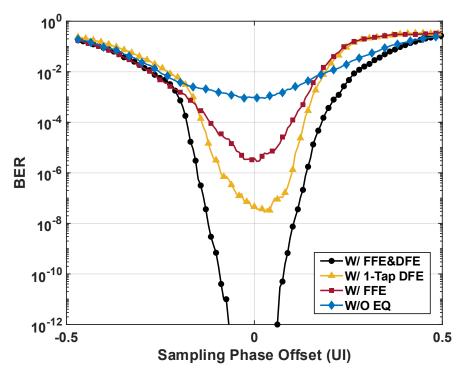

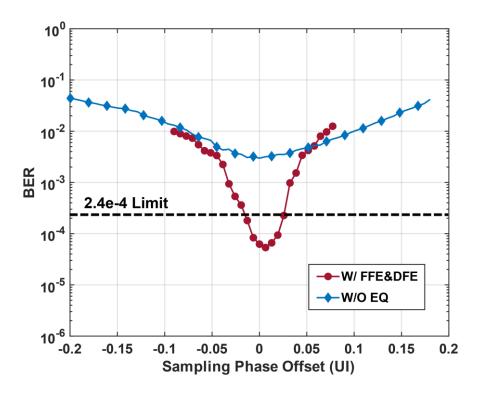

| Figure 3.32. Measured bathtub curves at 30-Gb/s NRZ with a 18-mV input amplitude 46            |

| Figure 3.33. Measured bathtub curves at 42-Gb/s PAM-4 input with a 40-mV input amplitude.      |

| 47                                                                                             |

| Figure 3.34. Micrograph of the ORX wire-bonded to a PD                                         |

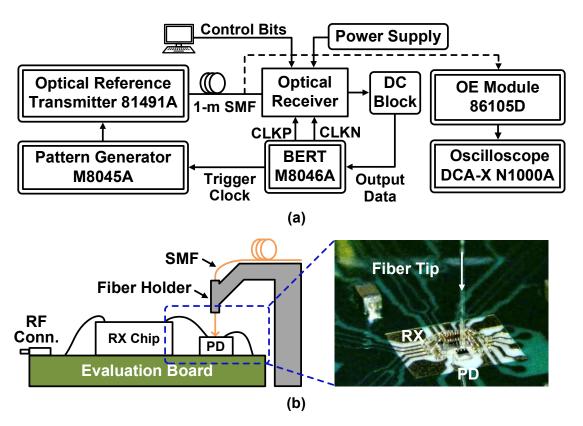

| Figure 3.35. (a) ORX optical measurement setup. (b) Block diagram and photo of the fiber       |

| coupling scheme                                                                                |

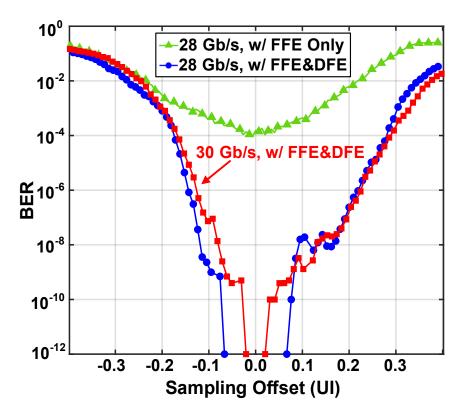

| Figure 3.36. Measured 28-Gb/s and 30-Gb/s NRZ bathtub curves                                   |

| Figure 3.37. Measured 48-Gb/s PAM-4 bathtub curves                                             |

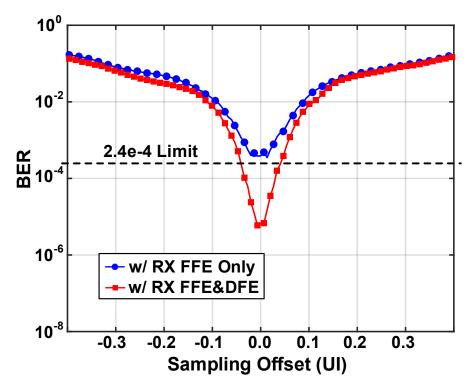

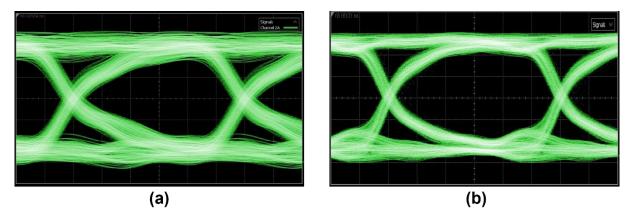

| Figure 3.38. Optical input eye diagrams of (a) a 30-Gb/s NRZ signal and (b) a 48-Gb/s PAM-     |

| 4 signal                                                                                       |

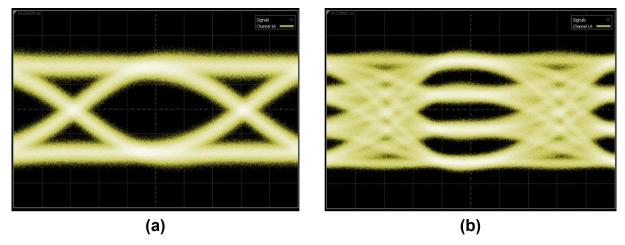

| Figure 3.39. Decoded output eye diagrams of (a) a 7.5 Gb/s with a 30-Gb/s NRZ optical input,   |

| and (b) a 6 Gb/s with a 48-Gb/s PAM-4 optical input                                                |

|----------------------------------------------------------------------------------------------------|

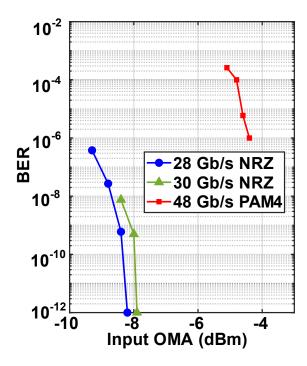

| Figure 3.40. Measured BER vs. input OMA sensitivity at 28, 30, and 48 Gb/s with the FFE            |

| and DFE. 51                                                                                        |

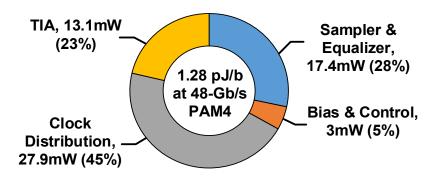

| Figure 3.41. ORX power breakdown                                                                   |

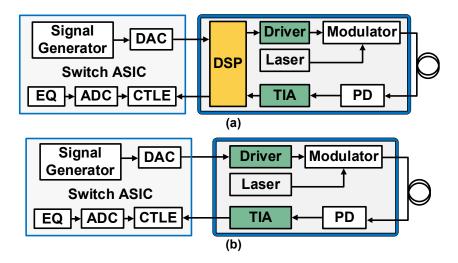

| Figure 4.1. Block diagrams of transmission links with (a) retimed and (b) linear drive optics.     |

|                                                                                                    |

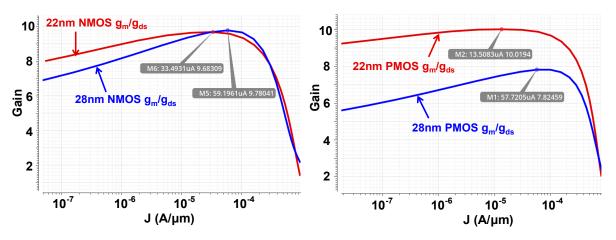

| Figure 4.2. Simulated intrinsic gain of 22-nm and 28-nm CMOS                                       |

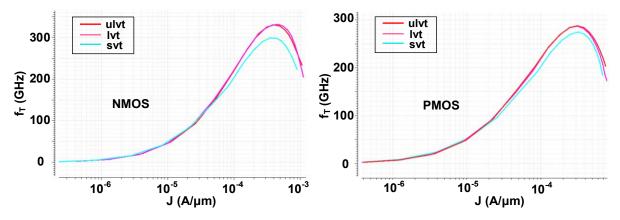

| Figure 4.3. Simulated f <sub>T</sub> of NMOS and PMOS in a 28-nm CMOS process                      |

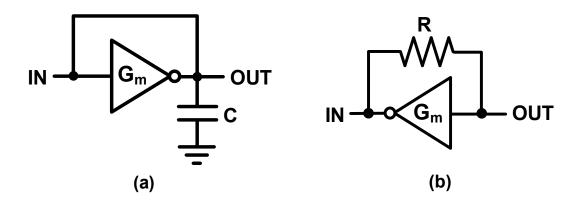

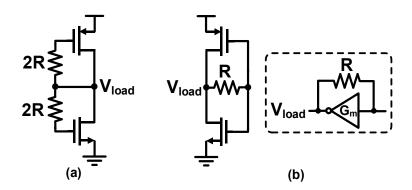

| Figure 4.4. (a) Inverter-based G <sub>m</sub> -C filter. (b) Inverter-based active inductor        |

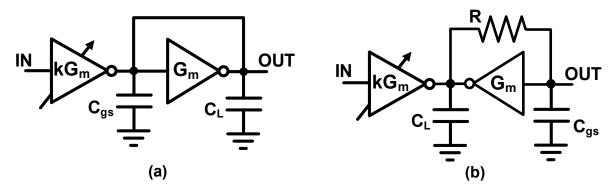

| Figure 4.5. Buffers with (a) diode connected load and (b) active inductor load 57                  |

| Figure 4.6. Schematic of a Cherry-Hooper amplifier                                                 |

| Figure 4.7. Modified Cherry-Hooper amplifiers. (a) Its second stage is replaced by an inverter-    |

| based TIA. (b) Inverter-based Cherry-Hooper amplifier                                              |

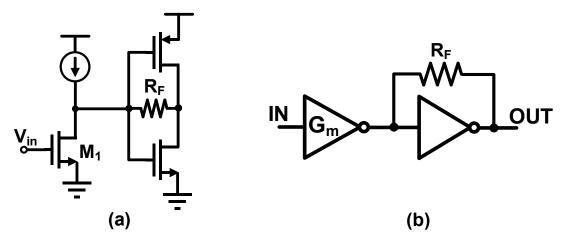

| Figure 4.8. TIA system design choices. Convert the signal to differential (a) right after the TIS. |

| or (b) after the CTLE, or (c) before the output buffer. (c) Keep the signal flow to be single      |

| ended through the TIA60                                                                            |

| Figure 4.9. Block diagram of the proposed TIA                                                      |

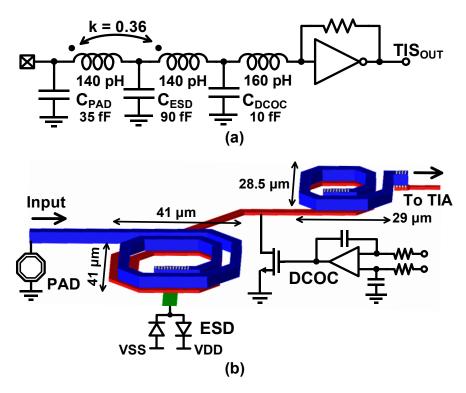

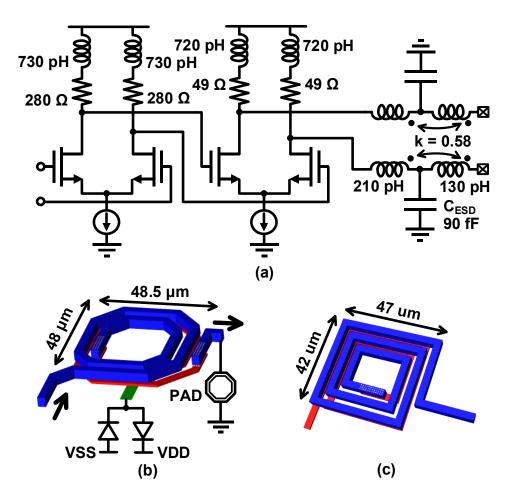

| Figure 4.10. (a) Schematic of the SF TIS with multi-peaking input network. (b) 3D layout of        |

| the proposed network                                                                               |

| Figure 4.11. Simulated S11 without and with the multi-peaking input network                        |

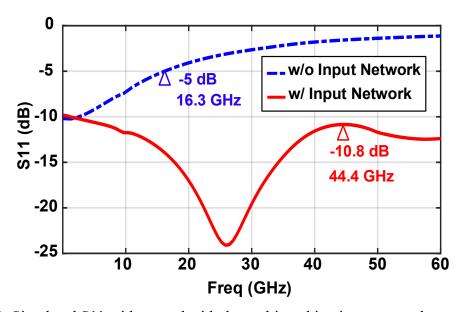

| Figure 4.12. (a) Schematic of the inverter-based CTLE with series peaking. (b) 3D layout of        |

| the series peaking inductor. (c) Schematic of the inverter-based S2D amplifier                     |

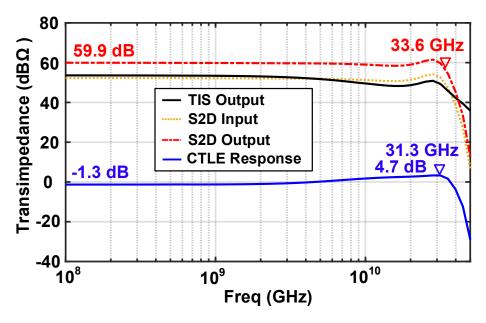

| Figure 4.13. Simulated frequency responses of the CTLE, the TIS, and signals at input and          |

| output of the S2D circuit                                                                          |

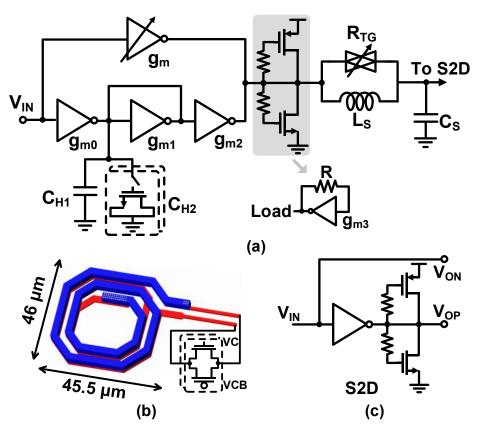

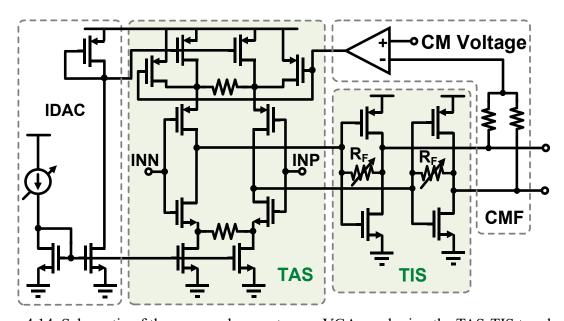

| Figure 4.14. Schematic of the proposed current reuse VGA employing the TAS-TIS topology            |

|                                                                                                    |

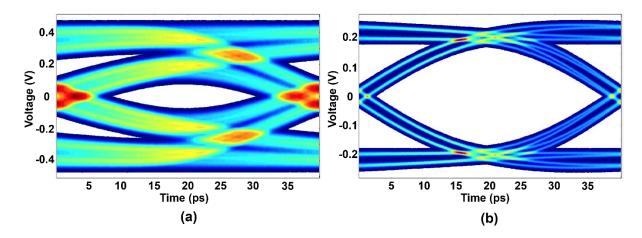

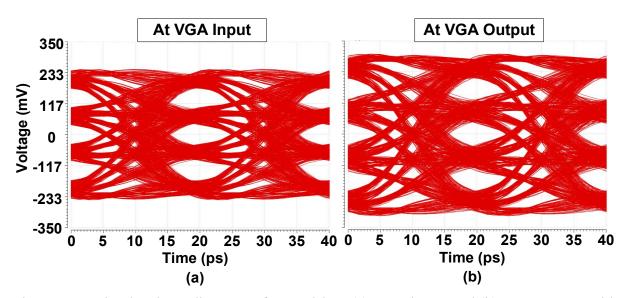

| Figure 4.15. Simulated eye diagrams of 100-Gb/s at (a) VGA input, and (b) VGA output, with         |

| a TIA input amplitude of 600 µApp                                                                  |

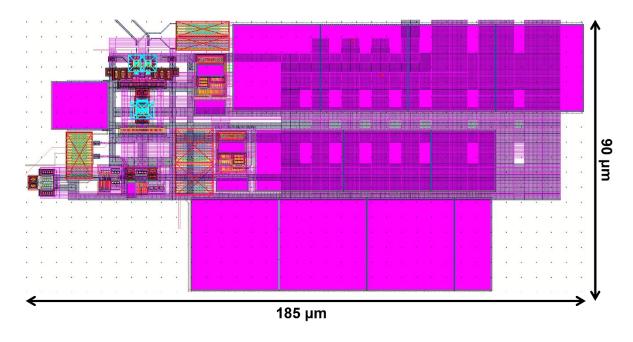

| Figure 4.16. Layout of the TIS, the CTLE, the S2D, and the VGA, except passive inductors.          |

| 67                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------|

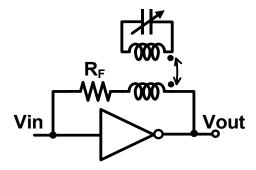

| Figure 4.17. (a) Schematic of the output buffer. 3D layout of (a) the T-coil and (b) the single-                    |

| ended shunt-peaking inductor. 68                                                                                    |

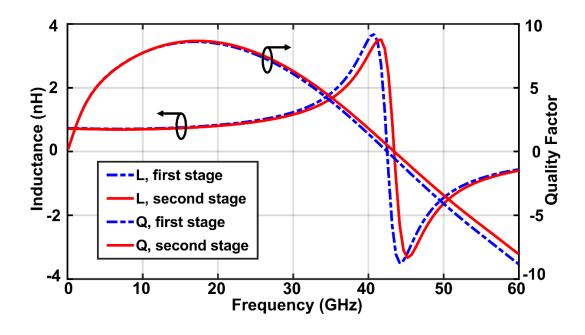

| Figure 4.18. Simulated inductance and quality factors of the inductor used in the output buffer.                    |

| 68                                                                                                                  |

| Figure 4.19. Layout of the two-stage output buffer                                                                  |

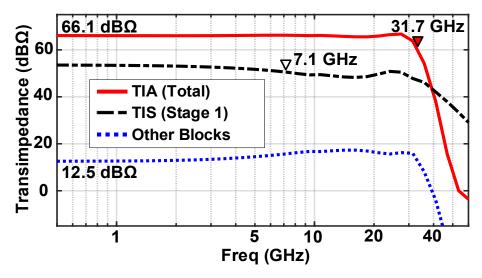

| Figure 4.20. TIA frequency response in post-layout simulation                                                       |

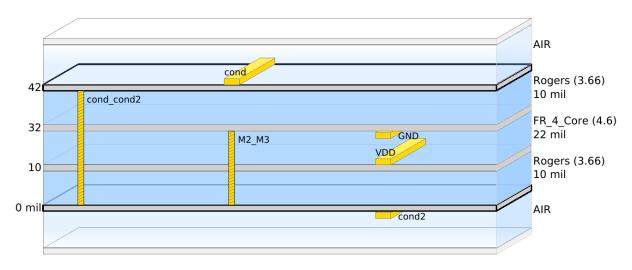

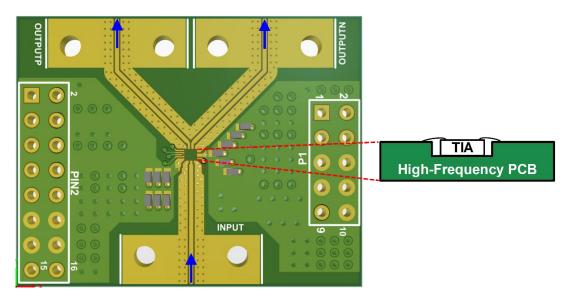

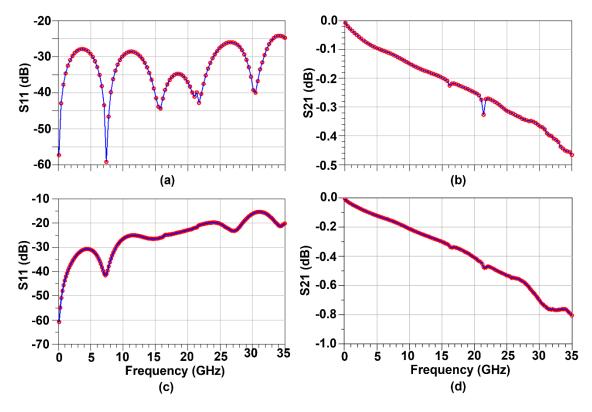

| Figure 4.21. 4-layer high-frequency PCB stackup                                                                     |

| Figure 4.22. High-frequency PCB layout                                                                              |

| Figure 4.23. (a) Simulated S11 and (b) S21 of the input PCB trace. (c) Simulated S11 and (d)                        |

| S21 of the output PCB trace. 71                                                                                     |

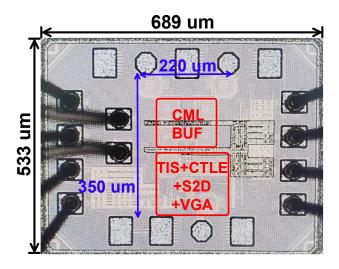

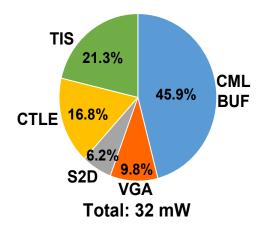

| Figure 4.24. Micrograph of the TIA.                                                                                 |

| Figure 4.25. TIA power breakdown                                                                                    |

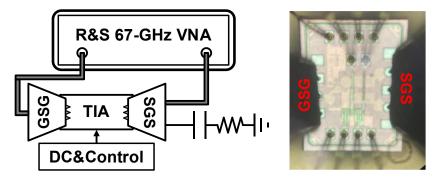

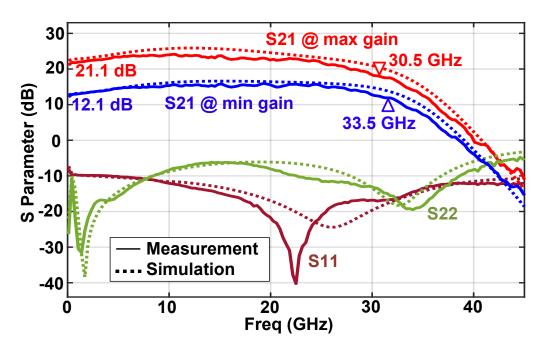

| Figure 4.26. Frequency domain measurement setup                                                                     |

| Figure 4.27. Measured and simulated S parameters of the TIA                                                         |

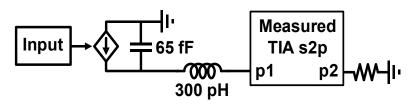

| Figure 4.28. Test bench for evaluating transimpedance of the TIA with a PD74                                        |

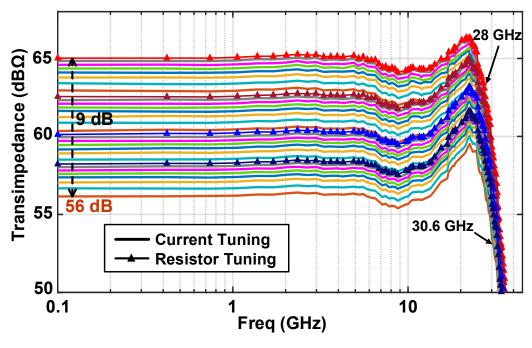

| Figure 4.29. Measured transimpedance of the TIA across the whole dynamic range74                                    |

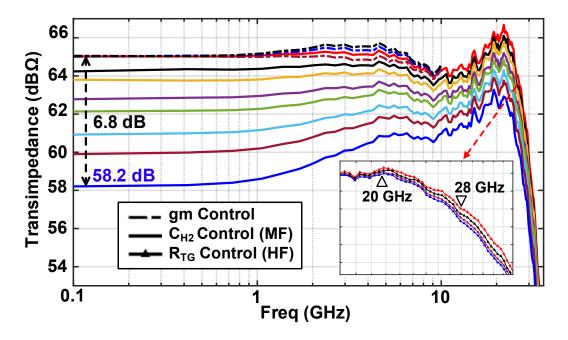

| Figure 4.30. Measured CTLE responses with MF and HF tuning                                                          |

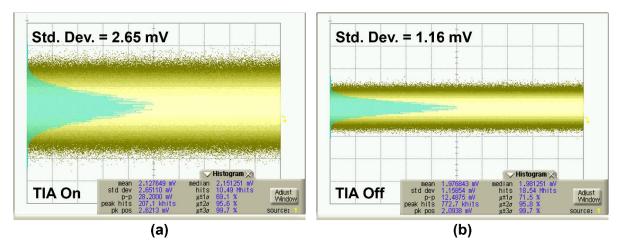

| Figure 4.31. Single-ended output voltage noise distribution measurements: (a) with the TIA                          |

| on, and (b) with the TIA off76                                                                                      |

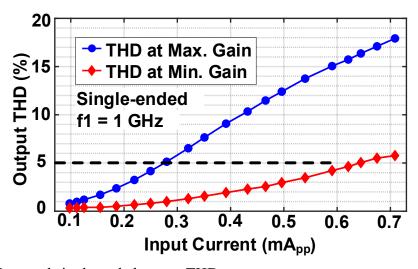

| Figure 4.32. Measured single-ended output THD                                                                       |

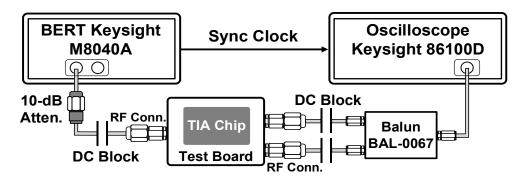

| Figure 4.33. Time domain measurement setup                                                                          |

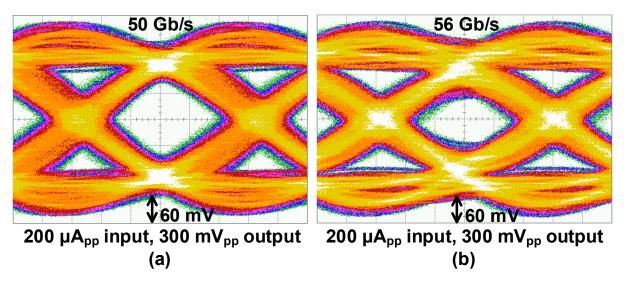

| Figure 4.34. Measured eye diagrams of (a) 50 Gb/s and (b) 56 Gb/s, both with 200 uA <sub>pp</sub> inputs            |

| and 300 mV <sub>pp</sub> outputs                                                                                    |

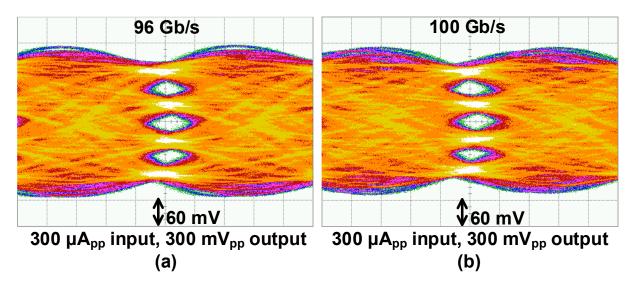

| Figure 4.35. Measured eye diagrams of (a) 96 Gb/s and (b) 100 Gb/s, both with 200 uA <sub>pp</sub> inputs           |

| and 300 mV <sub>pp</sub> outputs                                                                                    |

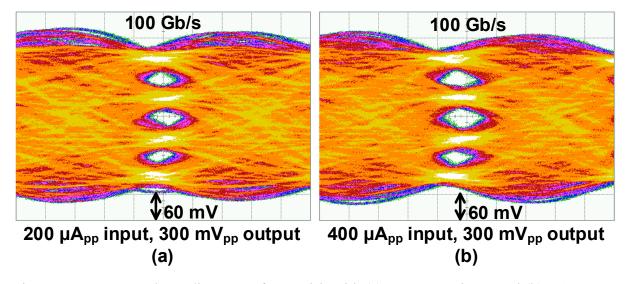

| Figure 4.36. Measured eye diagrams of 100 Gb/s with (a) a 200 uA <sub>pp</sub> input and (b) a 400 uA <sub>pp</sub> |

| input, both with 300 mV <sub>pp</sub> outputs                                                                       |

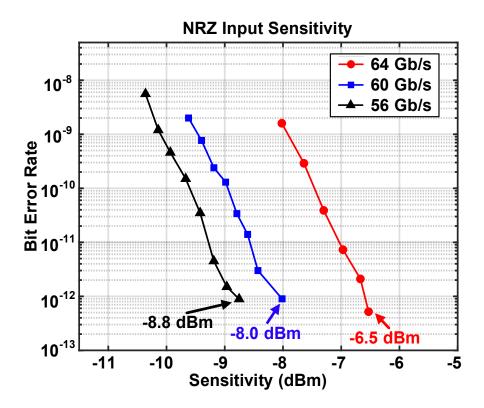

| Figure 4.37. BER versus NRZ input OMA sensitivity based on the measured BER at different                            |

| input amplitudes of electrical signals assuming a PD responsivity of 0.75 A/W                                       |

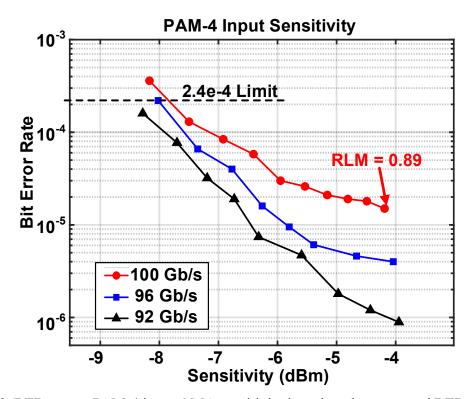

| Figure 4.38. BER versus PAM-4 input OMA sensitivity based on the measured BER a                      |

|------------------------------------------------------------------------------------------------------|

| different input amplitudes of electrical signals assuming a PD responsivity of $0.75~\mathrm{A/W}$ 8 |

| Figure 5.1. Illustration of signal distortion when TIA overloads.                                    |

| Figure 5.2. TIA with (a) a variable feedback resistor and (b) a variable input shunt resistor. 8     |

| Figure 5.3. Transformer-based Q shaping by modulating the varactor on the secondary side             |

| 8                                                                                                    |

| Figure A.1. Inverter-based active inductor circuits.                                                 |

| Figure A.2. Test voltage for input impedance of the inverter-based active inductor                   |

| Figure B.1. Test voltage for input resistance of the Cherry-Hooper amplifier9                        |

| Figure B.2. Test voltage for output resistance of the Cherry-Hooper amplifier9                       |

# **List of Tables**

| TABLE 3.1 Performance summary and comparison of CMOS ORX | 52 |

|----------------------------------------------------------|----|

| TABLE 4.1 Performance summary and comparison of CMOS TIA | 80 |

# Chapter 1

#### Introduction

#### 1.1 Motivation

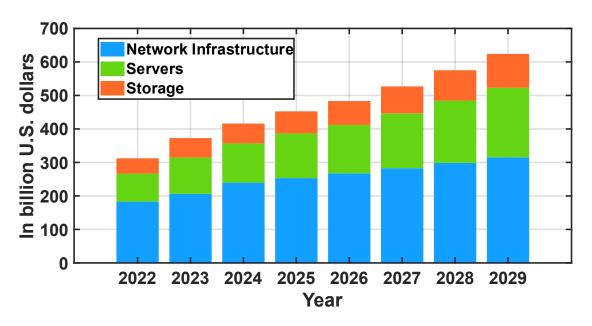

Data centers are crucial for storing, managing, analyzing and distributing data and information to the operation of online systems, applications, and services. The ever-increasing demand on the data centers with higher-bandwidth (BW), lower-cost and more energy-efficient solutions keeps increasing bolstered by the proliferation of data intensive applications, such as 5G, internet video, cloud-enabled services, and machine learning [1], [2]. The rise of big data and Internet of things (IoT) fuels data center market growth. As shown in Figure 1.1 [3], the size of data center market was valued at USD 312.3 billion in 2022 and is projected to grow from USD 372.78 billion in 2023 to USD 624.07 billion by 2030, exhibiting a compound annual growth rate (CAGR) of 7.6% during the forecast period (2023 - 2029). Of particular note is that network infrastructure accounts for more than 50% of the market share, and the revenue is forecast to exhibit strong growth in all segments in 2029.

Figure 1.1. Revenue in the data center market for different segments worldwide from 2022 to 2029 (in billion U.S. dollars) [3].

1

Scaling data centers to support higher traffic capacity poses significant challenges of providing higher data rate per area while managing power consumption and attendant heat dissipation. As the data rate continues to increase, traditional electrical interconnects within data centers have been pushed to their limits. Electrical I/Os have reached a bottleneck where it is impossible to overcome the BW limitation without sacrificing other performance metrics like power, reach or cost. Thus, the trend towards optical links has continued to grow due to the benefits provided by the optical channels and the development of electrical-to-optical (E/O) and optical-to-electrical (O/E) conversion technologies [4]. Optical scaling also continues to further support ultra-short-reach (USR) links and high-density interconnects, facilitating the increases in computational demands and performance of high-performance computing (HPC) modules [5]. In such cases, a high-BW, high-density, power-efficient and low-latency optical interface is therefore required.

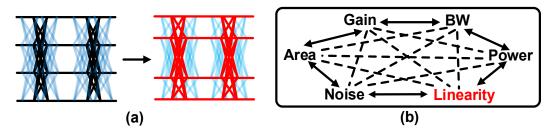

Figure 1.2. (a) Illustration of the effect of linearity on PAM-4 eye diagrams. (b) Design tradeoffs with linearity taken into consideration.

The modulation format is migrating towards four-level pulse amplitude modulation (PAM-4) format to provide higher spectral efficiency compared to non-return-to-zero (NRZ) modulation. However, as illustrated in Figure 1.2 (a), adapting to PAM-4 comes at the expense of enforced linearity constraints in both optical and electrical components, and the signal integrity becomes more vulnerable to both noise and linearity, presenting lower tolerance for signal-to-noise ratio (SNR). Compared with NRZ designs, besides the well-known BW-noise trade-off, PAM-4 systems place more emphasis on minimizing power consumption. Additionally, linearity has become a critical factor in design trade-offs, as highlighted in Figure 1.2 (b), which urges the development of optical interconnects featuring low noise, high-density, high power-efficiency, and high linearity.

#### 1.2 Background

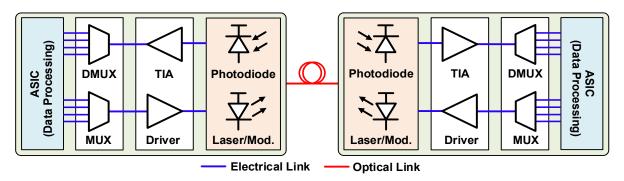

Intensity-modulation direct-detection (IMDD) optical system is the most straightforward implementation in short-reach interconnects due to its simplicity and low cost. In such systems, the transmitted data modulates the light intensity of a laser or an optical modulator, whereas a direct-detection receiver (RX) connected with a photodiode (PD) recovers the information at the RX side. Figure 1.3 provides a high-level overview of a typical IMDD optical interconnect, which consists of three main components: optical modules for electrical-to-optical (E/O) and optical-to-electrical (O/E) conversion, an electrical transceiver (front end + SerDes) for signal amplification and serialization/deserialization, and a digital signal processor (DSP) for data processing. On the RX side, the light from the optical fiber is detected by a PD, which generates a small output current in proportion to the light intensity. This current is then amplified and converted to a voltage by a transimpedance amplifier (TIA). A demultiplexer (DMUX) then converts the high-speed serial data stream into multiple parallel data streams for further digital processing. On the transmitter (TX) side, the data is processed reversely. Parallel lower-speed data from the DSP is combined into a single stream using a multiplexer (MUX). A laser/modulator driver drives the corresponding optoelectronic devices. The laser driver modulates the laser current, while the modulator driver drives the voltage across an optical modulator, which in turn modulates the light intensity from a continuous wave laser.

Figure 1.3. System diagram of an IMDD optical interconnect.

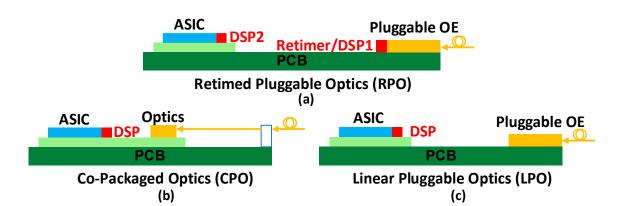

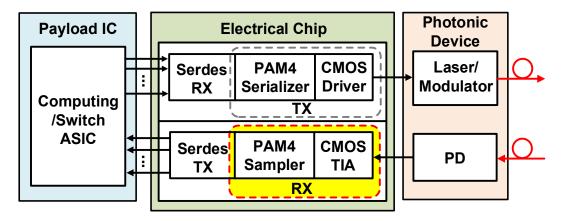

A conventional optical link from an application-specific integrated circuit (ASIC) on a host PCB to a pluggable optical engine (OE) with a re-timer or DSP chip is illustrated in Figure 1.4 (a). The host ASIC and the pluggable optical module are connected through electrical traces on

PCB. Inside the pluggable module, it usually includes a DSP chip to convert the interface on the host side, such as  $8 \times 50$  Gb/s signaling, into an optical interface, such as  $4 \times 100$  Gb/s signaling, or to convert them in a reverse order [6]. Crucially, the DSP also provides retiming and equalization, as it is too hard to directly connect the link from the ASIC to the optics [7]. During high-speed data transmission, this approach often leads to significant power consumption caused by the DSP and signal loss due to electrical traces on PCB. Generally, the shorter the electrical channel and the fewer the intermediate conversions, the easier it is to manage signal integrity issues. This has driven the trend of integrating optical modules closer to the ASIC, which can effectively reduce power consumption. Two main solutions have emerged based on this principle: co-packaged optics (CPO) and linear pluggable optics (LPO), as shown in Figure 1.4 (b) and (c), respectively. By co-packaging the optical module and the ASIC closely together, CPO technology greatly reduces the distance for signal conversion between electrical and optical domains, as well as the transmission distance. LPO technology places the optical module in a package near the ASIC and replaces DSPs with TIAs and drivers with high linearity and equalization capabilities. Both methods can significantly reduce power consumption, improve signal integrity, and reduce latency.

Figure 1.4. (a) Retimed pluggable optics in which an ASIC is placed to a pluggable OE with a re-timer or DSP chip. (b) Co-packaged optics where the optical module is on the same substrate as the ASIC. (c) Linear pluggable optics in which the OE is placed in a package near the ASIC, and the re-timer/DSP is removed.

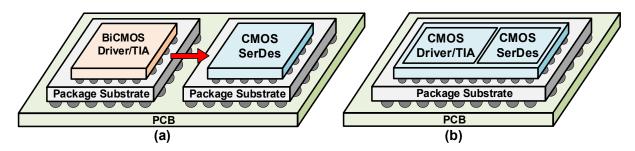

Furthermore, pluggable front-panel transceivers are often implemented in SiGe BiCMOS circuits, which necessitate separate dies for the front-end blocks and high-speed CMOS ASICs

[8]. Although scaling up with the speed and channels count to meet the throughput demand, these front-panel modules are soon becoming a bottleneck due to heavy cost and power associated with frequency-dependent losses in PCB traces and multiple discrete components in re-timer and buffer circuitry [9], [10]. Integration of front-end modulation driver and TIA and SerDes integrated circuits (ICs) in a single CMOS IC becomes desirable to reduce the length of electrical connections and the number of components as shown in Figure 1.5, hence improving power efficiency and BW density. On the optical receiver (ORX) side, CMOS implementation of linear TIA has already been demonstrated in prior works [11], [12], [13], [14], [15], and the integration of TIA with subsequent SerDes circuits provides additional design choices and flexibility to break design tradeoffs and enhance design capability of the front end by leveraging the characteristics and performance of post-TIA circuits [8], [16], [17], [18], [19], [20].

Figure 1.5. (a) Front-panel transceivers implemented in SiGe BiCMOS and (b) integration of CMOS front-end transceivers with SerDes IC.

#### 1.3 Thesis Organization

This thesis focuses on the design of energy-efficient CMOS PAM-4 ORXs for short-reach data center applications, targeting both CPO and LPO scenarios. In Chapter 2, equalization techniques are first introduced, followed by noise analysis and modelling of shunt-feedback (SF) TIAs. ORX sensitivity enhancement using continuous-time linear equalizers (CTLEs), feed-forward equalizers (FFEs), and decision feedback equalizers (DFEs) are further analyzed and simulated. Chapter 3 presents a 1.28-pJ/bit 48-Gb/s inductorless PAM-4 ORX implemented in a 28-nm CMOS technology, featuring a linear TIA integrated with a sampler. The proposed TIA avoids CTLEs and passive inductors, achieving a compact and energy-efficient design. A

FFE and a DFE are implemented at the sampler to compensate for TIA BW, ensuring reliable data recovery. Chapter 4 introduces a 0.32-pJ/bit 100-Gb/s PAM-4 TIA in a 28-nm CMOS technology. The design leverages multi-layer stacked networks, T-coils, and inductors for BW extension and electrostatic discharge (ESD) compensation. By exploiting CMOS scaling and complementary design techniques, the tradeoff between BW, noise, and power is effectively relaxed. Finally, Chapter 5 summarizes the work presented in Chapters 2–4 and discusses potential directions for future research.

# Chapter 2

# **Optical Receiver Sensitivity Enhancement by Equalization**

Equalizers are essential in high-speed communication to mitigate signal degradation and imperfections caused by BW limitations and channel nonidealities. In optical interconnect design, equalization techniques not only address BW constraints but also enhance ORX sensitivity. This chapter begins by discussing various equalization schemes on the RX side. Noise analysis is then conducted based on a simplified SF TIA model, and ORX sensitivity enhancement by different equalization techniques are analyzed and demonstrated.

### 2.1 Optical Receiver Equalization Techniques

#### 2.1.1 Continuous-Time Linear Equalizer (CTLE)

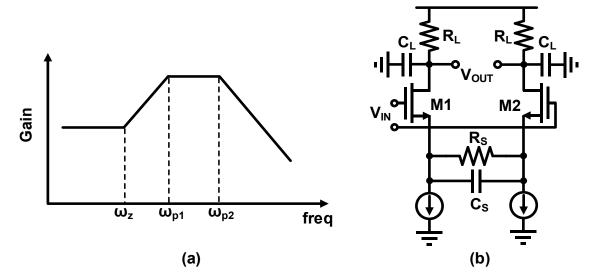

Figure 2.1. (a) Bode plot of a CTLE with one zero. (b) A CTLE circuit using resistive and capacitive degeneration in a differential pair.

CTLE is an analog equalizer that provides gain peaking in order to boost high frequencies. CTLEs are commonly designed in the frequency domain with a transfer function described as,

$$H_{CTLE}(s) = \frac{k(s+z_1)}{(s+p_1)(s+p_2)}$$

(2.1)

where  $z_1$ ,  $p_1$  and  $p_2$  are the zero and poles of the CTLE. Figure 2.1 (a) shows the Bode plot

of a CLTE, where one zero produces a +20 dB/decade rise and two poles produce -20 dB/decade falls in the frequency response. The poles locate the peaking frequency and determine the roll-off of the high frequency response. Filter design techniques using passive or active components can be adopted to design CTLEs. Using resistive and capacitive degeneration in an active differential pair to create high-frequency boosting is one of the most common methods as depicted in Figure 2.1(b), where high-frequency boosting is achieved by introducing real zero using the parallel resistor and capacitor network [21]. The transfer function of the CTLE in Figure 2.1 (b) can be expressed as,

$$H(s) = \frac{g_m}{C_L} \frac{s + \frac{1}{R_S C_S}}{\left(s + \frac{1 + g_m R_S/2}{R_S C_S}\right) \left(S + \frac{1}{R_L C_L}\right)}$$

(2.2)

where  $g_m$  denotes the transconductance of input transistors M1 and M2. The real zero and poles are given by:

$$\omega_z = \frac{1}{R_S C_S}, \omega_{p1} = \frac{1}{R_L C_L}, \omega_{p2} = \frac{1 + g_m R_S / 2}{R_S C_S}$$

(2.3)

The dominant pole  $\omega_{p1}$  is designed to be higher than the zero frequency to realize high-frequency peaking gain, and the peaking gain is controlled by the ratio of the dominant pole and zero frequencies.

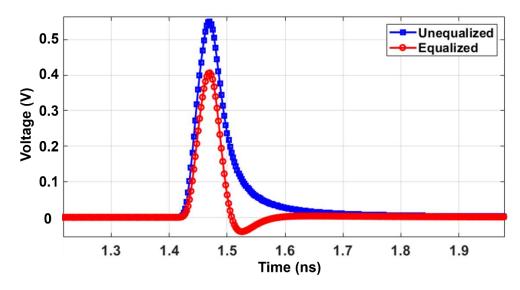

Figure 2.2. Pulse responses of a BW-limited signal and the CTLE-equalized signal.

Figure 2.3. Eye diagrams of the signal (a) before and (b) after equalized by the CTLE.

To illustrate the effect of the CTLE, a 25-Gb/s NRZ signal through a channel with 8-dB loss at 10 GHz without and with CTLE is simulated and compared. The CTLE has a peaking frequency of 12.5 GHz, a dc gain of -6 dB, and a peaking gain of 6 dB. The time domain pulse responses (pulse width = 40 ps) of the BW-limited signal and the equalized signal are given in Figure 2.2, where the postcursor of the original pulse is cancelled by the CTLE. The corresponding 1-unity interval (UI) eye diagrams of these two signals are given in Figure 2.3 (a) and (b), respectively, demonstrating a significant improvement in the eye opening.

#### 2.1.2 Feed-Forward Equalizer (FFE)

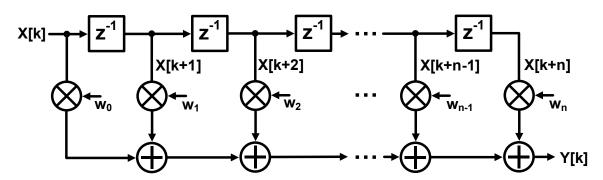

Figure 2.4. Block diagram of a linear n-tap FFE.

A FFE compensates for the signal degradation by amplifying or attenuating specific frequency components of the signal. This technique employs a finite impulse response (FIR) filter with a series of tap weights programmed to adjust the impulse and the frequency response with taps being both precursor and postcursor. The number of taps determines the complexity and

compensation ability of the FIR filter. The block diagram for a linear n-tap FFE is illustrated in Fig. 2.4, and the corresponding transfer function can be given as:

$$Y[k] = \sum_{j=0}^{n} X[k+j] \cdot w[j]$$

(2.4)

A FFE is configured to have high-pass characteristics and emphasizes the high-frequency signal components and hence ameliorates the inter-symbol interference (ISI). However, as a linear equalizer, the noise and crosstalk are also high-pass-filtered and amplified by the FFE. For analog implementations on the RX side, a number of delayed versions of input signal are generated using delay lines or multi-phase sampling and are added back at an analog summer with proper weights for summing or subtracting operations.

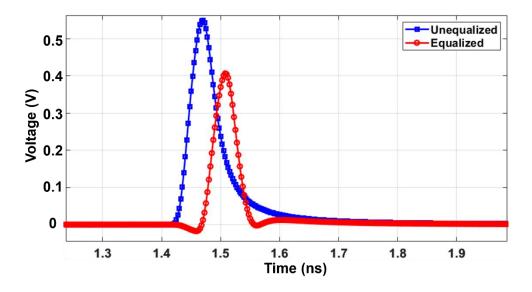

Figure 2.5. Pulse responses of a BW-limited signal and the FFE-equalized signal.

The 25-Gb/s NRZ signal described in 2.1.2 is also simulated and compared here to illustrate the effect of the FFE. A 3-tap FFE is used with a precursor of -0.05, main cursor of 1, and postcursor of -0.26. The time domain pulse responses of the BW-limited signal and the equalized signal are given in Figure 2.5, where both the precursor and the postcursor of the original pulse are cancelled by the FFE. The corresponding 1-UI eye diagrams of these two signals are given in Figure 2.6 (a) and (b), respectively, demonstrating a significant improvement in the eye opening.

Figure 2.6. Eye diagrams of the signal (a) before and (b) after equalized by the FFE.

## 2.1.3 Decision Feedback Equalizer (DFE)

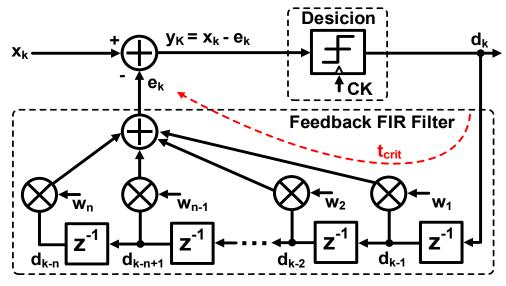

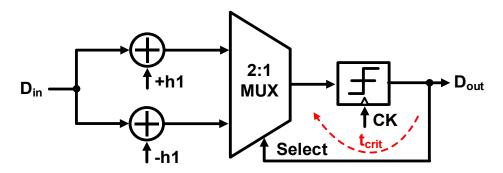

Figure 2.7. Block diagram of a n-tap direct DFE.

A DFE is a kind of nonlinear equalizer that uses a weighted sum of past decision(s) to cancel the ISI caused by previously detected symbols on the current symbol [22]. In effect, the distortion caused by previous pulses on the current pulse is subtracted. The block diagram of a n-tap DFE is depicted in Fig. 2.7, in which the decision function is also realized by a comparator, and postcursor ISI appearing in the uncompensated pulse response can be mitigated by the feedback signal. With an n-tap feedback FIR filter incorporated, an n-tap DFE can be built, enabling the compensation for n-tap post-cursor ISI. The corresponding transfer function can be expressed as

$$y_k = x_k - \sum_{i=0}^n d_k \cdot w_k \tag{2.5}$$

The key advantage of a DFE is that the feedback signal is a quantized symbol level, which prevents the amplification of noise and crosstalk that occurs in the CTLE and FFE topologies [23]. Nevertheless, unlike a FFE, the DFE can only cancel postcursor ISI because the subtraction is performed on the arriving symbols after the decision. In addition to clock phase alignment and proper setting of feedback taps, a major difficulty faced in DFE implementations is dealing with the total loop delay to meet the critical timing associated with feeding back the previous symbol decisions, which is denoted as t<sub>crit</sub> in Figure 2.7 with the red dashed line. The DFE architecture in Figure 2.7 falls into the category of direct DFE, and the timing constraint in such a direct DFE design can be expressed as:

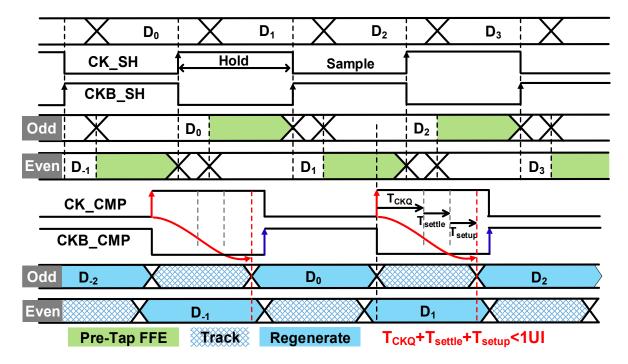

$$T_{CKQ} + T_{settle} + T_{setup} < 1 UI (2.6)$$

where  $T_{CKQ}$  is the clock-to-Q delay of the slicer,  $T_{settle}$  is the settling time of the summer, and  $T_{setup}$  is the setup time of the slicer. Similar speed limitations exist in other variants of this architecture as well. Another drawback of the DFE is that decision errors tend to propagate at future decisions due to residual ISI and a reduced margin against noise [24].

Figure 2.8. Block diagram of a 1-tap loop-unrolled DFE.

By transforming the feedback loop of Figure 2.7 to a predictive or "unrolled" topology, an alternative loop-unrolled (speculative) DFE architecture can be obtained as shown in Figure 2.8, which slightly relaxes the timing constraint of the first DFE tap to:

$$T_{CKO} + T_{setup} + T_{MUX} < 1 UI (2.7)$$

where  $T_{MUX}$  denotes the delay from the select input of the MUX to its output and is usually smaller than  $T_{settle}$  in Eq. (2.6). However, for loop-unrolled DFE, the number of required slicers increases exponentially with the number of taps unrolled. If DFE is designed with n taps loop-unrolled in NRZ systems, the demand for  $2^n$  slicers is required. Such hardware cost and power consumption are much more severe for a system with high-order modulation formats. For example, realizing an n-tap loop-unrolled DFE in PAM-4 systems leads to the required number of slicers to be proportional to  $4^n$ .

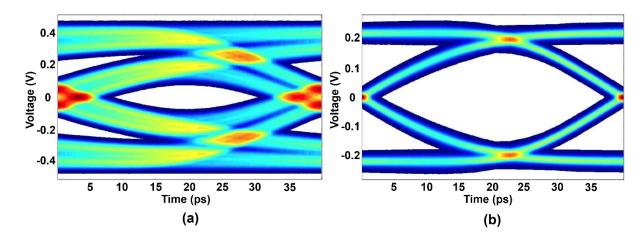

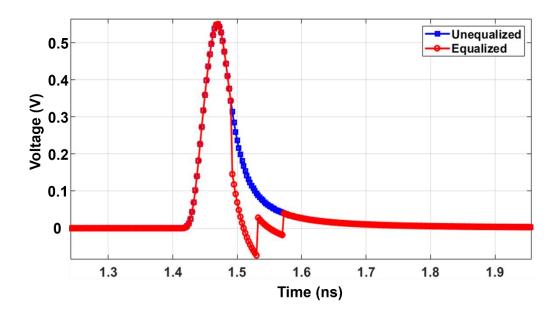

Figure 2.9. Pulse responses of a BW-limited signal and the DFE-equalized signal.

Figure 2.10. Eye diagrams of the signal (a) before and (b) after equalized by the DFE.

To demonstrate the impact of the DFE, a 25-Gb/s NRZ signal is simulated using a 2-tap DFE with postcursor coefficients of -0.17 (first tap) and -0.06 (second tap). Figure 2.9 compares the time-domain pulse responses of the BW-limited signal and the equalized signal, showing the effective cancellation of postcursor interference by the DFE. The nonlinear behavior of the DFE is also evident in the pulse responses. The corresponding 1-UI eye diagrams are presented in Figure 2.10 (a) and (b), respectively, demonstrating a significant improvement in the eye opening.

#### 2.2 SF TIA Noise Analysis

Figure 2.11. Illustration of noise contributions in SF TIA.

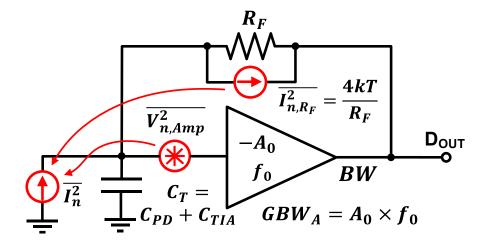

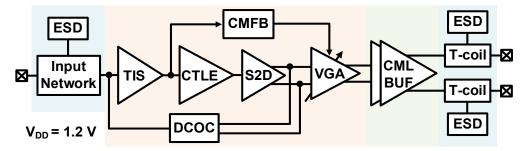

The overall achievable sensitivity in high-speed ORXs is usually limited by the noise performance of the TIA. Considering SF TIA which is the most common TIA circuit topology in deep sub-micron CMOS technology [14], [25], [26], a simplified SF TIA model is depicted in Figure 2.11, which consists of a feedback resistor  $R_F$  and a feed-forward amplifier with a gain and BW of  $A_0$  and  $f_0$  respectively. When accounting for the impact of finite BW of the feed-forward amplifier at high data rate, the transimpedance of TIA has a second-order response given by [27]

$$Z_T(s) = \frac{R_F A}{1+A} \times \frac{1}{1+s/(\omega_0 Q) + s^2/\omega_0^2} \approx \frac{R_F}{1+s/(\omega_0 Q) + s^2/\omega_0^2}$$

(2.8a)

$$\omega_0 = \sqrt{\frac{(1+A)\omega_A}{R_F C_T}} \tag{2.8b}$$

$$Q = \frac{\sqrt{(1+A)\omega_A R_F C_T}}{1 + R_F C_T \omega_A}$$

(2.8c)

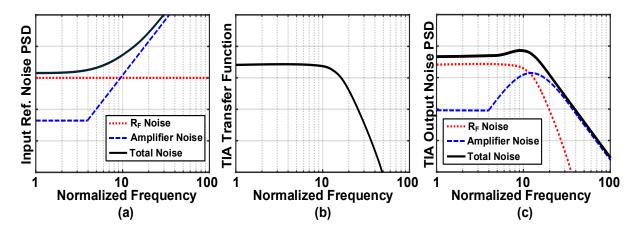

Figure 2.12. SF TIA (a) input referred current noise PSD, (b) magnitude frequency response, and (c) output voltage noise PSD.

For maximally flat TIA magnitude (Butterworth) response,  $Q = 1/\sqrt{2}$ , and the TIA BW (BW<sub>3dB</sub>) can be expressed using Eq. (2.8b) and (2.8c) as [27]

$$BW_{3dB} = \frac{\sqrt{2A(A+1)}}{2\pi R_E C_T} \approx \frac{\sqrt{2}A}{2\pi R_E C_T}$$

(2.9)

The feedback resistance,  $R_F$ , needed to achieve the Butterworth response can be calculated as

$$R_F = \frac{(A+1)\omega_A}{C_T B W_{3dB}^2} \approx \frac{GBW_A}{2\pi C_T B W_{3dB}^2}$$

(2.10)

where  $C_T$  is the total capacitance at TIA input node consisting of the PD capacitance  $(C_{PD})$  and TIA input capacitance  $(C_{TIA})$ , and  $GBW_A$  is the gain-BW product of the feed-forward amplifier. As shown in Eq. (2.10),  $R_F$  decreases quadratically with  $BW_{3dB}$ . If  $GBW_A$  and  $C_T$  keep constant and  $BW_{3dB}$  becomes n time smaller, then  $R_F$  becomes  $n^2$  time larger, Eq. (2.9) shows  $A_0$  is n

time larger, and  $f_0$  is n time smaller. The main noise contributors of SF-TIA are  $R_F$  and the feed-forward amplifier as illustrated in Figure 2.12 (a). When referred to the TIA input, noise from  $R_F$  appears as white noise while the feed-forward amplifier voltage noise has both  $f^2$  noise and white noise. The input-referred current noise power spectral density (PSD) can be expresses as [18]

$$\frac{\overline{i_{n,in,SF}^2}(f) = \overline{i_{n,RF}^2}(f) + \overline{i_{n,amp}^2}(f) = \frac{4kT}{R_F} + \frac{4kT\gamma}{g_m R_F^2} + 4kT\gamma \times \frac{(2\pi C_T)^2}{g_m} \times f^2$$

$$\approx \frac{4kT}{R_F} + 4kT\gamma \times \frac{(2\pi C_T)^2}{g_m} \times f^2$$

(2.11)

where  $g_m$  is the transconductance of input MOSFETs of the feed-forward amplifier. The output voltage noise PSD of the TIA can be calculated by multiplying  $\overline{i_{n,in,SF}^2}(f)$  by the squared magnitude of TIA transfer function as illustrated in Figure 2.12 (b) and (c). The total input referred current noise power can be expressed as [27]

$$\overline{i_n^2} = \frac{4kT}{R_F} \times I_1 B W_{3dB} + 4kT\gamma \times \frac{(2\pi C_T)^2}{g_m} \times \frac{I_2^3}{3} B W_{3dB}^3$$

(2.12)

where  $\gamma$  is the channel-noise factor, and two Personick integral numbers  $I_I = 1.11$  and  $I_2 = 1.49$  are for Butterworth response. The first term in Eq. (2.12) is due to  $R_F$  and the second term is due to feed-forward amplifier which is minimized when  $C_{PD} = C_{TIA} = 0.5C_T$ . In such case,  $\overline{i_n^2}$  can be expressed as [27]

$$\overline{i_n^2} = 4kT \frac{2\pi C_T}{f_T} BW_{3dB}^3 \times \left( I_1 \times \frac{f_T}{GBW_4} + \frac{I_2^3}{3} \times 2\gamma \right)$$

(2.13)

Eq. (2.13) shows that the noise increases cubically with  $BW_{3dB}$ . If  $GBW_A$  is fixed to be  $f_T/3$ , and  $C_{PD} = C_{TIA} = 80 \, fF$ , then using Eq. (2.9) (2.10) and (2.13), the TIA second order frequency response can be determined by  $BW_{3dB}/n$  and  $f_0/n$ , and the noise at different  $BW_{3dB}$  can be calculated and modelled. In Chapter 3, the SF TIA noise-BW relationship here will be extended to the ORX link to further evaluate the sensitivity enhancement of different post-TIA equalizations.

#### 2.3 Sensitivity Enhancement by Equalization

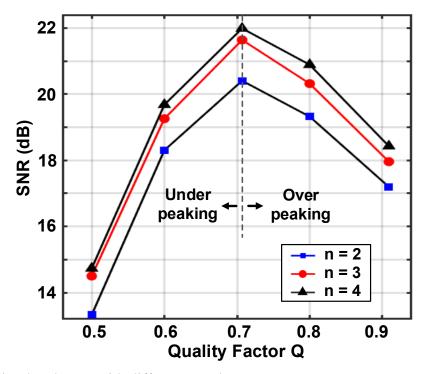

#### 2.3.1 CTLE-Equalized SF TIA

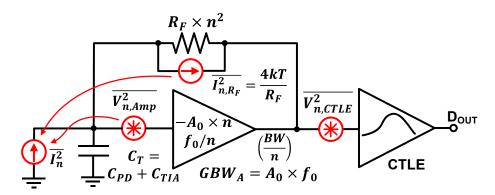

Figure 2.13. CTLE-equalized SF TIA design where a low-BW TIS is followed by a BW recovering CTLE.

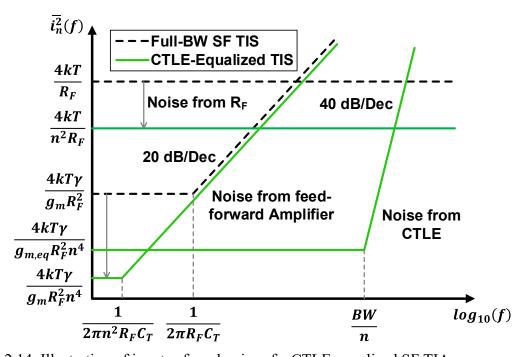

A low-noise design approach is illustrated in Figure 2.13, where the first stage is a low-BW transimpedance stage (TIS) followed by a CTLE to recover the required BW and reduce the ISI of the first stage [28]. The noise reduction insight with the approach considered can be explained as follows. Assuming  $R_F n^2$  as feedback resistor now and the overall BW remains the same as the single SF TIA with a feedback resistor  $R_F$ , then the input-referred noise PSD of the CTLE-equalized SF-TIS  $\overline{i_{n,in,SF}^2|_{CTLE}}(f)$  can be calculated as:

$$\frac{1}{i_{n,in,SF}^{2}|_{CTLE}}(f) = \frac{4kT}{R_{F}n^{2}} + \frac{4kT\gamma}{g_{m}R_{F}^{2}n^{4}} + 4kT\gamma \times \frac{(2\pi C_{T})^{2}}{g_{m}} \times f^{2} + \frac{4kT\gamma}{g_{m.eq}|_{Z_{T}}|^{2}}$$

$$= \frac{4kT}{R_{F}n^{2}} + \frac{4kT\gamma}{g_{m}R_{F}^{2}n^{4}} + 4kT\gamma \times \frac{(2\pi C_{T})^{2}}{g_{m}} \times f^{2} + \frac{4kT\gamma}{g_{m.eq}R_{F}^{2}n^{4}} + \frac{4kT\gamma}{g_{m.eq}R_{F}^{2}n^{4}} \left(\frac{f}{BW_{3dB}/n}\right)^{4}$$

$$= \frac{4kT}{R_{F}n^{2}} + \frac{4kT\gamma}{g_{m}R_{F}^{2}n^{4}} + 4kT\gamma \times \frac{(2\pi C_{T})^{2}}{g_{m}} \times f^{2} + \frac{4kT\gamma}{g_{m.eq}R_{F}^{2}n^{4}} + \frac{4kT\gamma}{g_{m.eq}R_{F}^{2}} \left(\frac{f}{BW_{3dB}}\right)^{4}$$

$$\approx \frac{4kT}{R_{F}n^{2}} + 4kT\gamma \times \frac{(2\pi C_{T})^{2}}{g_{m}} \times f^{2} \qquad (2.14)$$

where  $g_{m.eq}$  stands for the transconductance of input transistors of CTLE. Eq. (2.10) and (2.14) indicate that if the factor n is increased, then all the white noise terms can be reduced, while the  $f^2$  and  $f^4$  color noise terms remain unchanged. As a result, such a low noise design

approach boils down to a trade-off between the choice of the increasing factor n and equalization capability of the CTLE. A large n resulting in reduced TIS BW necessitates a higher peaking from the CTLE to recover overall targeted BW, imposing more stringent demand on the design of CTLEs. Figure 2.14 further illustrates the noise contributions and reduction of the two equations in logarithmic scale. As long as the equalizer can recover a given BW, this approach significantly reduces the white noise, and the colored noise almost remains the same. Input referred noise of a SF-TIA with its BW well equalized and restored by a CTLE can be calculated as

$$\overline{i_{n,in,SF}^2|_{CTLE}} = 4kT \frac{2\pi C_T}{f_T} BW_{3dB}^3 \times \left(\frac{I_1}{n^3} \times \frac{f_T}{GBW_A} + \frac{I_2^3}{3} \times 2\gamma\right)$$

(2.15)

Figure 2.14. Illustration of input-referred noise of a CTLE-equalized SF TIA.

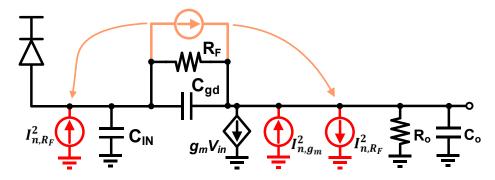

Figure 2.15. Small-signal model of TIS for calculating the output noise.

Again, compared with Eq. (2.13), Eq. (2.15) reveals that CTLE helps reduce  $R_F$  noise contribution by  $n^2$  but does not affect the noise from the feed-forward amplifier. The transfer functions of TIS and CTLE are further derived to calculate the output RMS noise for simulation and analysis. The TIS transfer function is first derived using the small-signal model as shown in Figure 2.15, where the thermal noise from  $R_F$  is split at input and output [29]. The second-order TIS transfer function  $Z_{TIS}$  and its output impedance  $Z_o$  can be derived as

$$Z_{TIS}(s) = \frac{-R_o(g_m n R_F - 1 - s C_{gd} n R_F)}{1 + g_m n R_F + s K_1 + s^2 K_2}$$

(2.16)

$$Z_o(s) = \frac{R_o \left[ 1 + snR_F \left( C_{gd} + C_{IN} \right) \right]}{1 + g_m nR_F + sK_1 + s^2 K_2}$$

(2.17)

where  $K_1 = C_{IN}(R_o + nR_F) + C_oR_o + C_{gd}nR_F(1 + g_mR_o)$ , and  $K_2 = nR_FR_o(C_{IN}C_o + C_{IN}C_{gd} + C_{gd}C_o)$ . The transfer function of an ideal unity-gain CTLE stage that recovers the full BW is given as

$$H_{CTLE}(s) = \frac{1 + g_m R_F + s K_1 + s^2 K_2}{(1 + g_m R_a) \left(1 + \frac{s}{nQ2\pi f_{TIS}} + \frac{s^2}{(n2\pi f_{TIS})^2}\right)}$$

(2.18)

Eq. (2.18) is written as a second-order system with a quality factor of Q. Zeros of the CTLE cancels poles of the TIS. The noise PSD at CTLE output can be obtained by multiplying the  $R_F$  thermal noise term  $I_{n,R_F}^2 = 4kT/nR_F$  and channel thermal noise term  $I_{n,g_m}^2 = 4kT\gamma g_m$  with the corresponding transfer functions

$$S_{CTLE,out}(s) = I_{n,R_F}^2 | (Z_{TIS} - Z_o) \times H_{CTLE} |^2 + I_{n,g_m}^2 | Z_o \times H_{CTLE} |^2$$

(2.19)

And the RMS noise at CTLE output can be calculated as square root of the integrated PSD

$$V_{noise,out} = \sqrt{\int_0^\infty S_{CTLE,out}(s)df}$$

(2.20)

The SNR at CTLE-equalized TIA output is defined as the ratio of the worst PAM-4 eye opening  $V_{ISI}$  to the RMS noise  $V_{noise,out}$

$$SNR = 20log_{10} \left( \frac{V_{ISI}}{V_{noise,out}} \right) \tag{2.21}$$

$V_{ISI}$  is calculated using peak distortion analysis modified for PAM-4 format [29]

$$V_{ISI} = |V_0| - 3\sum_{i \neq 0} |V_i| \tag{2.22}$$

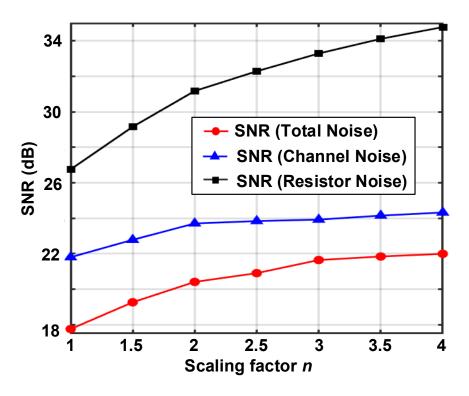

Where  $V_0$  is the main cursor and  $V_i$  is the  $i_{th}$  pre/post cursors. After that, the SNR as a function of  $R_F$  scaling factor n is plotted as Figure 2.16. The quality factor Q is kept  $1/\sqrt{2}$ . The signal to  $R_F$  noise ratio and signal to channel noise ratio are also plotted for comparison. Figure 2.16 reveals that SNR improves as n increases, but when n is larger than 3, channel noise becomes dominated, and the SNR improvement is not pronounced.

Figure 2.16. Simulated SNR with different scaling factor *n*.

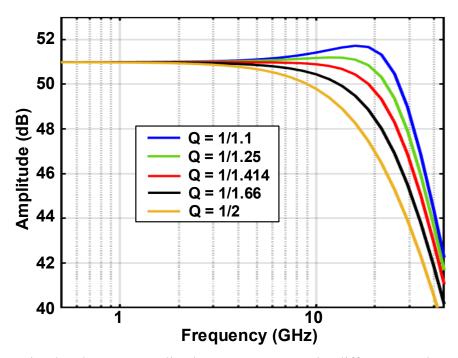

If the CTLE is not well-designed, over or under peaking would happen which also affects the TIA noise. Figure 2.17 depicts the simulated CTLE-equalized TIA responses with scaling factor *n* kept 3 under different Q values to demonstrate the under/over peaking. The SNR as a function of quality factor Q is also simulated and plotted as Figure 2.18. The over or under peaking degrades the SNR, but if the variation of Q is less than 15%, the SNR degradation is less than 2 dB. As a result, peaking tunability is also required for CTLE design.

Figure 2.17. Simulated CTLE-equalized TIA responses under different Q values.

Figure 2.18. Simulated SNR with different Q values.

Increasing  $R_F$  results in a reduced  $BW_{3dB,TIS}$ , which in turn implies that higher peaking from CTLEs is required to recover overall targeted BW. Nevertheless, CTLE with its first-order peaking response (one zero and two poles) cannot adequately compensate for loss introduced by the second-order TIS response profile without introducing in-band peaking. Any such

peaking, however, results in TIA noise enhancement and degrades receiver sensitivity [18]. Therefore, design iterations and optimizations are required to find the right balance between  $R_F$  value and the extent to which CTLE is capable of recovering the desired BW.

## 2.3.2 SF TIA with Post-TIA Equalization

Figure 2.19. ORX design with post-TIA equalizers.

Conventionally, higher data rates in ORXs are achieved by extending the front-end TIA BW using techniques like CTLEs or passive inductive peaking. On the other hand, as an alternative approach, low-noise, high-gain, and low power CMOS ORXs can be designed by reducing the BW of entire TIA, followed by equalization techniques such as FFEs and DFEs as illustrated in Figure 2.19. Reducing TIA BW can help lower its input-referred noise, albeit at the cost of increased ISI. If the ISI penalty can be compensated at the subsequent equalizer with minimal noise penalty, the overall ORX sensitivity can be improved [16]. This approach is particularly attractive and advantageous for ORXs where the TIA and SerDes circuits are integrated into a single CMOS IC.

For NRZ ORX, the sensitivity is limited by TIA noise for BWs larger than 0.5x data rate and by ISI for smaller BWs, demonstrating a fundamental tradeoff between noise and ISI [18]. For PAM-4 ORX, the bit error rate (BER) using a BW-limited TIA with post-TIA equalization can be determined by evaluating the combined impact of noise and ISI. The model in Figure 2.20 is used to explore the effectiveness of post-TIA equalization at 50-Gb/s PAM-4 data rate. A 25-GHz E/O modulator and a 25-GHz PD with a sensitivity of 0.75 A/W are included in the signal path as additional BW-constrained elements. The SF TIA is modelled with a second-order

response, and the noise is calculated based on the BW-noise relationship in section 2.2, followed by the FFE and DFE. Parasitic capacitance of 160 fF and 20 fF are added at input and output of the TIA, respectively. Since it is known that high-frequency jitter is amplified in BW-limited systems, it is important to comprehend this effect when computing the optimal TIA BW. 1-ps random jitter (RJ) and 1.5-ps-pp duty cycle error (DJ) are added at the input of E/O modulator. Latch noise and offset (7 mV in total) are also considered and included in the model.

Figure 2.20. ORX model used to evaluate post-TIA equalizations.

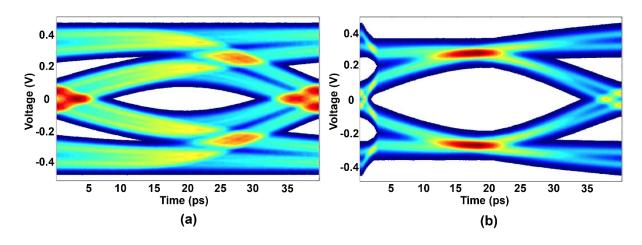

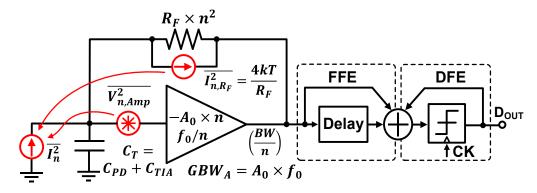

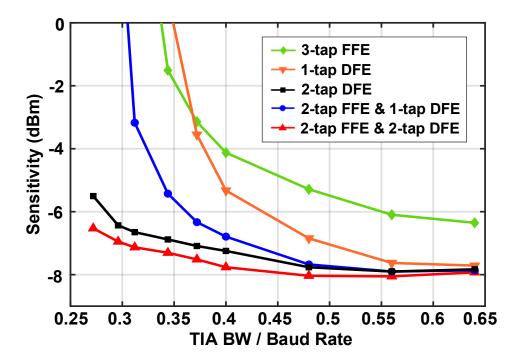

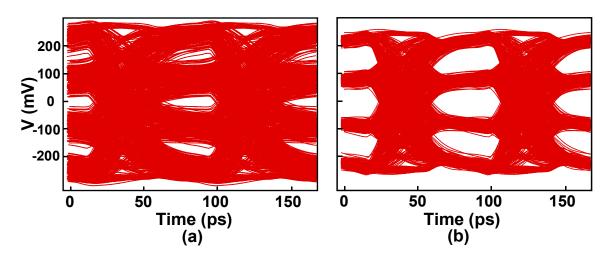

Figure 2.21 illustrates the simulated PAM-4 ORX sensitivity across various post-TIA equalization configurations using a comprehensive model, with TIA BWs normalized to the data rate. For the 3-tap FFE, both a 1-tap precursor and a 1-tap postcursor are used, while in other cases, only a 1-tap precursor is employed. For TIA BWs smaller than 0.45x Baud rate, the sensitivity is primarily limited by ISI, thus both FFEs and DFEs help improve sensitivity, but a combination of a FFE and a DFE shows better improvement than the FFE only. Conversely, for TIA BWs exceeding 0.45x baud rate, noise becomes the dominant limiting factor. Here, the nonlinear DFE demonstrates superior performance compared to the linear FFE, with the combination of a 2-tap FFE and a 2-tap DFE achieving the best results. Although the sensitivity improvement at high TIA BWs is not markedly pronounced compared to using the DFE alone as shown in Figure 2.17, the 2-tap FFE + 2-tap DFE configuration is still preferred in this design because the ISI in both precursor and postcursor can be cancelled, and it leaves more flexibility and margin for TIA design. Besides, adding one-tap FFE and a second-tap DFE to a time-

interleaved ORX does not impose significant overhead.

Figure 2.21. Simulated PAM-4 ORX sensitivity with different configurations of post-TIA equalizations.

# Chapter 3

# A 1.28-pJ/bit 48-Gb/s Inductorless PAM-4 Optical Receiver

#### 3.1 Overview

The growing demand for high-bandwidth memory (HBM) and silicon photonics-based interconnects drives the need for power-efficient, low-latency, and high-density multi-channel optical interfaces. As introduced in Chapter 1, integrating CMOS serializers and samplers with optical interface electronics enhances BW density and power efficiency, making it particularly suitable for short-reach data center applications, as illustrated in Figure 3.1. Prior works have demonstrated the feasibility of integrating TIAs with subsequent SerDes circuits, which provides additional design choices and flexibility to break design tradeoffs and enhance design capability of the front end by leveraging the characteristics and performance of the subsequent circuits.

Figure 3.1. Integration of front-panel transceivers with SerDes circuits in a single CMOS IC.

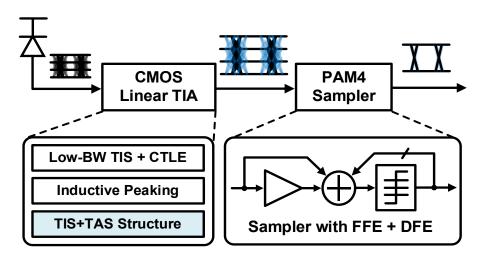

The inherent tradeoffs between gain, noise, BW, and linearity make the power-efficient, low-latency, and high-density PAM4 ORX design highly challenging. As illustrated in Figure 3.2, to break the tradeoffs, a two-stage front-end design method using the CTLE in the TIA to compensate for low-BW TIS is proposed in [28]. At 25-Gb/s, this approach achieves significant noise reduction compared to a single-stage TIA. However, the CTLE has limited ability to

compensate for multiple TIA poles, as excessive compensation can cause in-band peaking and introduce high-frequency noise. Additionally, CTLEs become increasingly power-hungry at higher data rates. For instance, [15] employs a 2-stage CTLE to boost the TIA BW up to 32-GHz in 16-nm CMOS, while resulting in a power efficiency of 0.69-pJ/bit. Inductive multipeaking scheme is another common technique in TIA design [30], [31], but its use of passive inductors poses challenges for compact and high-density implementations due to their large area and limited tunability. For example, [11] demonstrates an impressive BW of 60 GHz in 28-nm CMOS using various inductive peaking techniques, but at the cost of ~0.25 mm<sup>2</sup> area and 0.96-pJ/bit power efficiency.

Figure 3.2. Integrated CMOS linear TIA and PAM-4 sampler with the FFE and the DFE.

Integrating the equalizer into the sampler, rather than the TIA, provides an alternative approach for ORX design, as depicted in Figure 3.2. Previous works, such as [8], [17] and [18], have demonstrated the integration of TIA and sampler with DFEs to address the noise-BW tradeoff, though these designs are limited to NRZ signaling. For instance, [8] combines a low-BW TIA with a 4-tap DFE in 65-nm CMOS, and a very good sensitivity of –16.8 dBm is achieved, but the data rate is limited to 12 Gb/s and the 1.9-pJ/bit energy efficiency is still too high. To support PAM-4 modulation, [16], [19], and [20] further extend this approach by integrating linear TIAs with post-TIA equalizers. However, all these PAM-4 designs suffer from high power consumption and area inefficiency, making them unsuitable for high-density multichannel optical links. For example, [20] implements a 32-Gb/s PAM-4 ORX in 40-nm CMOS

by combining a TIA with a 2-tap DFE. However, the use of a three-stage cascaded amplifier-based TIA, a three-stage cascaded variable gain amplifier (VGA), and a CTLE with inductive peaking results in a high energy efficiency of 4.59-pJ/bit and a rather large area of 0.029 mm<sup>2</sup>. Similarly, [16] achieves the first 100-Gb/s PAM-4 ORX in 28-nm CMOS by designing a low-BW TIA followed by a PAM-4 sampler including a 2-tap FFE and a 2-tap DFE. While the ORX achieves high data rate and good sensitivity, and a distributed current-integrating summer helps close the DFE loop. Nevertheless, the four-stage pre-amplifier and the three-stage post-amplifier (post-amp) with series and shunt peaking in the TIA design and the current-integrating summer contribute a 3.9-pJ/bit power efficiency and an area of 0.45 mm<sup>2</sup>, highlighting the challenges in balancing speed, power, and area.

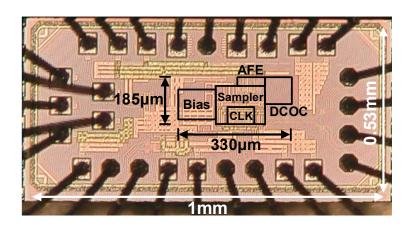

In this chapter, a CMOS linear TIA is integrated with a PAM-4 sampler into a single CMOS IC as illustrated in Figure 3.2. The TIA employs a transadmittance-stage transimpedance-stage (TAS-TIS) topology to replace conventional current-mode logic (CML)-based VGA and post-amp, avoiding CTLE and inductors while preserving linearity and a high gain-BW product for PAM-4 operation. The sampler incorporates a 2-tap FFE and a 2-tap DFE to relieve ISI from the TIA, ensuring correct data recovery, providing favorable data-rate density, and achieving superior energy efficiency among TIA and ORX designs. Timing criteria of DFE loop is achieved up to 30 GBaud by optimizing the clock-to-Q delay of slicers. The proposed ORX is implemented in a 28-nm CMOS technology and is wire-bonded to a commercial PD. Optical measurement results at 48-Gb/s PAM-4 show the ORX achieves -5.1-dBm sensitivity at 2.4e-4 BER consuming 61.4 mW, with only 13.1 mW contributed from the TIA, resulting in 1.28-pJ/bit (0.27 pJ/bit for TIA only) efficiency.

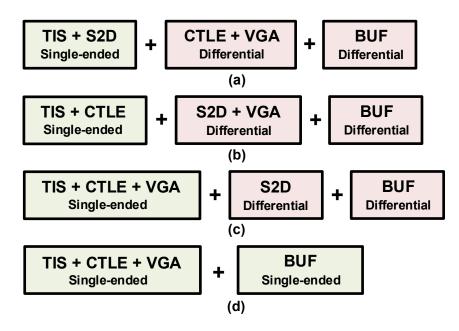

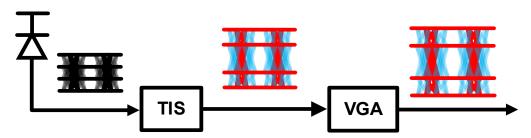

#### 3.2 System Architecture

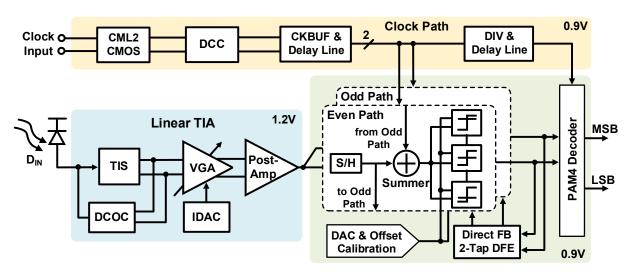

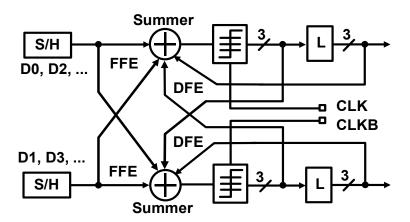

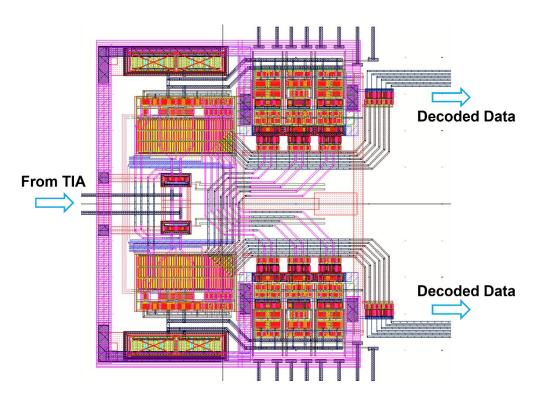

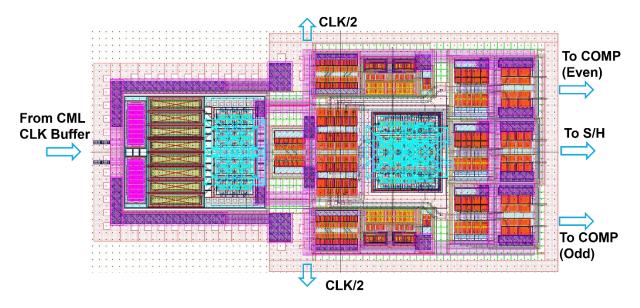

Based on the analysis results in Chapter 2, an ORX composed of a TIA with a BW of 0.5x Baud rate followed by a 2-tap FFE and a 2-tap DFE is designed. The block diagram of the proposed PAM-4 ORX is depicted in Fig. 3.3, which consists of a CMOS linear TIA, PAM-4 samplers, and a clock path. The CMOS linear TIA includes a TIS, a VGA, and a post-amp to accommodate a large input dynamic range with negligible BW variation. The common-mode photocurrent

and input referred offset voltage are subtracted by the dc offset cancellation (DCOC) loop. After two half-rate sample/hold (S/H) circuits and summers, three slicers in odd/even path and a voltage digital to analog converter (DAC) are employed with a 2-tap precursor FFE and a 2-tap DFE to recover the PAM-4 output of TIA to 3-bit digital thermometer codes. The recovered thermometer codes are then converted into 2-bit binary codes, including a most significant bit (MSB) and a least significant bit (LSB) output, which are deserialized and sent to off-chip bit BER testing. The clock path takes external half-rate differential clock signals and amplifies them to rail-to-rail. Voltage-controlled delay lines (VCDL) and dividers are included for data decoding and deserializing.

Figure 3.3. Block diagram of the proposed PAM-4 ORX architecture.

Figure 3.4. Block diagram of the proposed CMOS linear TIA.

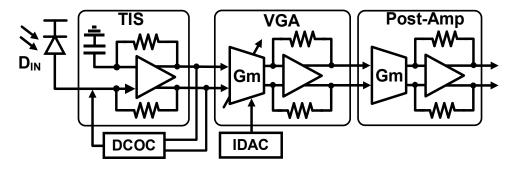

Figure 3.4 shows the block diagram of the CMOS linear TIA. A pseudo-differential TIS is used as the first stage, and therefore the single-ended to differential (S2D) circuit is not needed.

The VGA with the gain controlled by a current DAC (IDAC) provides over 20 dB dynamic range, and the post-amp provides over 10 dB gain. Both the VGA and the post-amp adopt a TAS-TIS topology and use active inductors instead of passive inductors to save area. Passive inductors and CTLE are avoided here, which makes the TIA compact and energy efficient.

## 3.3 Building Blocks

### 3.3.1 PD Interface and TIS

Figure 3.5. (a) Direct connection scheme where noise modulates the input signal. (b) On-chip connection scheme where noise is filtered and ac-coupled to VSS<sub>TIA</sub>. (c) Simulated conversion gain from PD bias to TIA input. (d) Schematic of TIS and DCOC circuits.

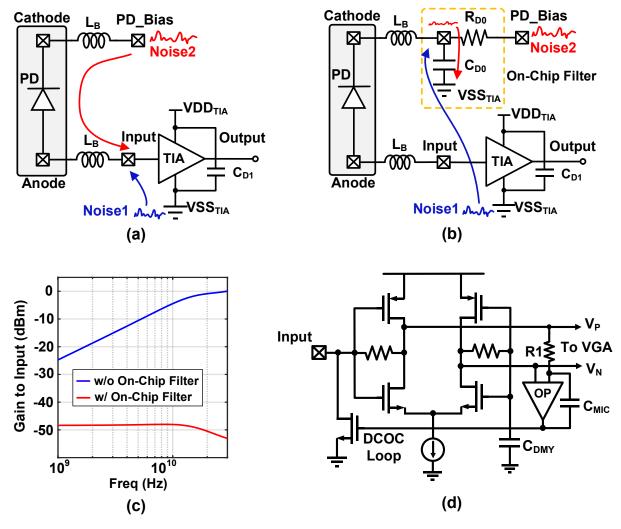

The ORX is designed to interface with an external high-speed PD. At the ORX input, the single-

ended signal amplitude can be as low as 10 mV, which is particularly sensitive to noise. Therefore, the interface between the PD and ORX input should be treated carefully. Either a direct connection scheme or an on-chip connection scheme can be used to provide the bias voltage to the PD. The former one directly connects the bias voltage to the cathode of PD through a bonding wire L<sub>B</sub> as shown in Figure 3.5 (a), and the other one first connects the PD cathode to ORX chip and makes the cathode ac-coupled to TIA ground VSS<sub>TIA</sub> before it is connected to the bias voltage, as illustrated in Figure 3.5 (b). While the direct connection scheme is simple and saves chip pads, it has significant drawbacks. As noted in [8], due to the single-ended nature of the TIA input, noise at the VSS<sub>TIA</sub> (referred to as noise1) affects the input signal since the PD signal is referred to VSS<sub>TIA</sub> rather than the PD cathode at TIA input, and thus only PD anode is modulated by the noise1. Furthermore, the noise at the PD bias voltage (noise2) only modulates the PD cathode and would directly affect the TIA input, severely degrading sensitivity.

Figure 3.6. Simulated gain and phase of the DCOC loop.

In the on-chip connection scheme, PD cathode and  $VSS_{TIA}$  are ac-coupled through a capacitor, ensuring both are modulated by the same noise and improving ground noise rejection.  $R_{D0}$  and  $C_{D0}$  also provide on-chip filtering to attenuate noise2 before it is ac-coupled to  $VSS_{TIA}$ . As shown in Figure 3.5 (c), the on-chip filter effectively reduces the gain from the PD bias to the

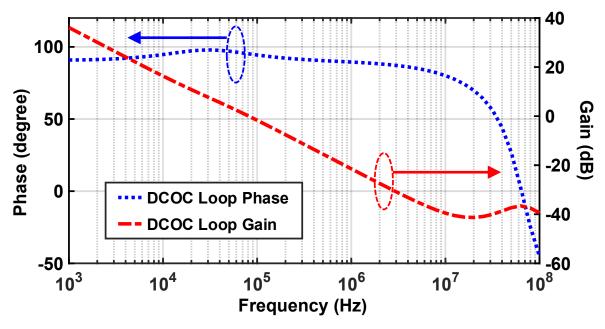

TIA input compared to the unfiltered case. Figure 3.5 (d) illustrates the schematic of the TIS and DCOC circuits. The pseudo-differential push-pull TIS performs single-ended to differential conversion and incorporates a current tail for enhanced supply noise rejection [32]. The DCOC loop, formed by R1,  $C_{MIC}$ , OP, and M1, uses R1 and Miller capacitance  $C_{MIC}$  to create a low-pass filter. This feedback loop removes the DC component from the input signal before it enters the TIS, preventing a dc drop across  $R_F$ . Cutoff frequency of DCOC loop  $f_C$  must be much smaller than the data rate of the received signal to avoid baseline wander or data-dependent jitter, especially in the presence of long sequence of consecutive identical bits. As shown in Figure 3.6, the implemented DCOC loop has a cutoff frequency of 80 kHz with a phase margin of 85°.

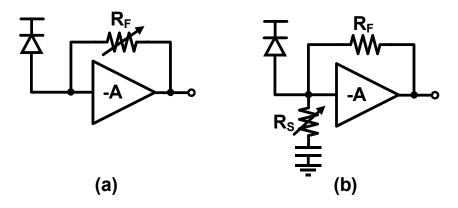

## 3.3.2 VGA and Post-Amp

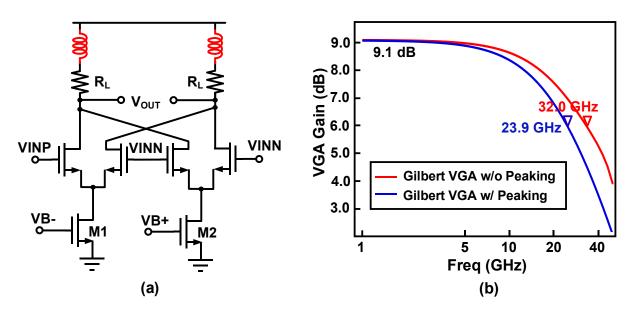

Figure 3.7. (a) Schematic of a conventional Gilbert-cell-based VGA. (b) Simulated frequency responses of VGA with and without inductive shunt peaking.

The VGA and the post-amp are designed to provide over 20 dB of dynamic range, and 10 dB gain, respectively. The Gilbert-cell-based VGA shown in Figure 3.7 (a) is widely used in linear TIAs to achieve a large input dynamic range while maintaining a constant frequency response [11], [33]. Nevertheless, limited by the gain-BW product of the structure, shunt inductive peaking is usually required to expand the VGA BW as shown in Figure 3.7 (b), where two 580-

pH inductors are used to achieve a BW of 32 GHz.

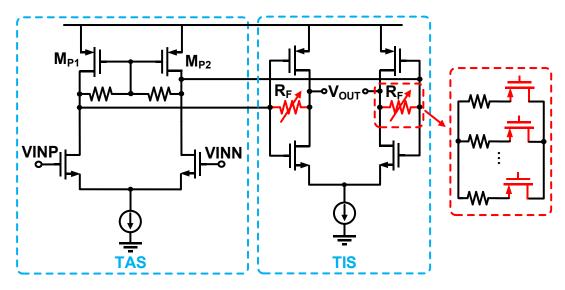

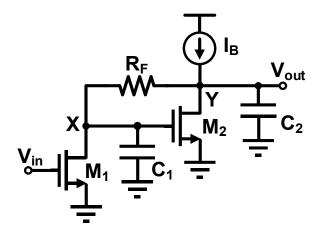

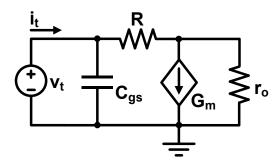

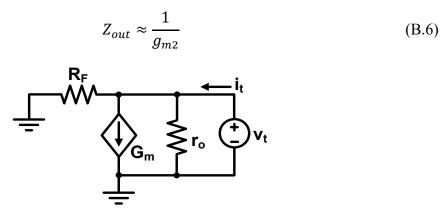

Another type of VGA comprised of a TAS and a TIS is shown in Figure 3.8, which in essence is a modified Cherry-Hooper amplifier [17]. The TAS provides transconductance  $Gm_{TAS}$ , and the TIS with feedback resistor  $R_F$  provides relatively low input resistance as described in Eq. (2.8a). Therefore, the dc gain of the VGA is

$$Gain_{TAS-TIS} = Gm_{TAS} \times \frac{A_{TIS}}{A_{TIS} + 1} R_F \tag{3.1}$$

where  $A_{TIS}$  is the gain of feed-forward amplifier of TIS. The VGA changes the gain by tuning the value of feedback resistor  $R_F$ . Compared to the Gilbert-cell-based VGA, TAS-TIS topology provides much smaller load impedance of TAS which is  $R_F/A_{TIS}$  now, and also provides a smaller load impedance of TIS which is only  $1/Gm_{TIS}$ , resulting a larger capacity for driving the post-amp and a much higher gain-BW product, where  $Gm_{TIS}$  is the transconductance of TIS [34], [35].

Figure 3.8. Schematic of a TAS-TIS topology-based VGA with its gain controlled by the feedback resistor R<sub>F</sub>.

However, the variable resistor  $R_F$  causes BW variations over gain variations. For instance, with a design target of 20-dB tuning range and a constant  $Gm_{TAS}$ ,  $R_F$  needs to have a tuning range of 10 times, so does the load impedance of TAS, and the overall BW of VGA is therefore affected. In addition, the switches for feedback resistor control would bring extra parasitic

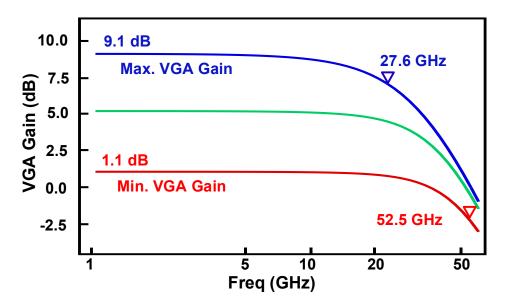

capacitance reducing the BW, which becomes particularly serious when multi-bit control is required to support fine tuning of overall gain. A 3-bit TAS-TIS VGA with a tuning range of 8-dB is designed for evaluation as shown in Figure 3.9. Simulations show that the VGA provides a max. dc gain of 9.1 dB with a corresponding BW of 27.6 GHz, but the BW is over 50 GHz at 1.1 dB gain, resulting in a 25 GHz BW variation across 8 dB gain variation. When the TIA is set to have a low gain, the severe BW variation would cause high-frequency ripples and degrade the signal quality and noise performance.

Figure 3.9. Simulated frequency responses of the TAS-TIS VGA with different gain settings.

Figure 3.10. Schematic of the proposed Gilbert-TIS VGA.

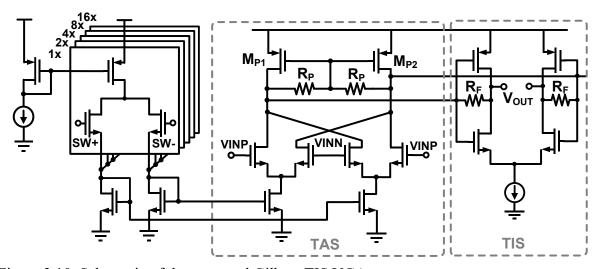

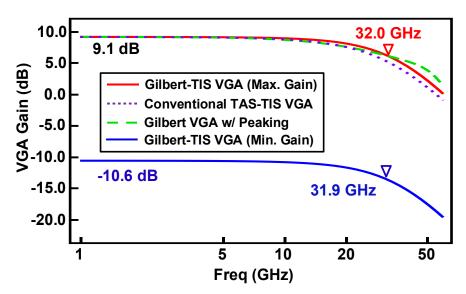

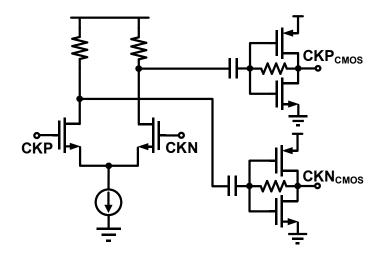

The proposed VGA adopts a TAS-TIS topology, but the gain is controlled by changing the  $Gm_{TAS}$  instead of the feedback resistor  $R_F$  as shown in Figure 3.10. The TAS uses a Gilbert cell controlled by a 5-bit current DAC, and the resistor  $R_F$  is fixed to maintain a constant BW across gain variations, thus combining the advantages of both Gilbert-cell-based VGAs and conventional TAS-TIS VGAs. The fully differential input of the first stage also helps convert pseudo-differential signals from TIS into fully differential ones. Simulation results in Figure 3.11 show that under the same low-frequency gain of 9.1 dB, the proposed VGA achieves the same gain-BW product as the Gilbert-cell-based VGA with two 580-pH inductors, and its BW variation is less than 0.2 GHz over 19 dB gain variation. From another perspective, by splitting the transconductance and loading of the Gilbert cell and replacing the load resistors  $R_L$  in Figure 3.7 (a) with a TIS, the proposed VGA achieves a much higher gain-BW product and is able to remove inductors, with only an additional power consumption 2.7 mW.

Figure 3.11. Simulation results and comparison of frequency responses for three types of VGAs.

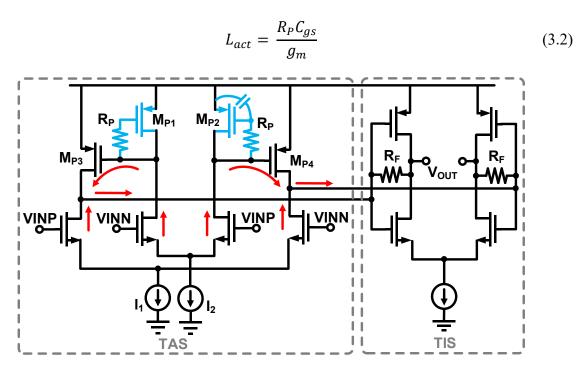

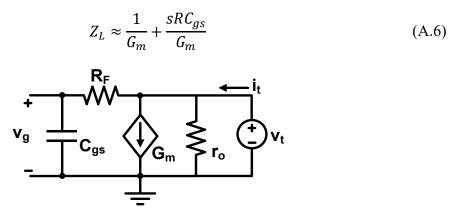

The post-amp also adopts a TAS-TIS topology as shown in Figure 3.12, where the TAS consists of two differential pairs so that the output of  $M_{P1}$  and  $M_{P2}$  at inner pair can be further amplified by  $M_{P3}$  and  $M_{P4}$  at outer pair to achieve higher transconductance [14]. Besides,  $M_{P1}$ ,  $M_{P2}$  with a transconductance of  $g_m$ , parasitic capacitance  $C_{gs}$  and resistor  $R_P$  form active inductors to further extend the BW [36], with inductance given by

Figure 3.12. Schematic of the post-amp.

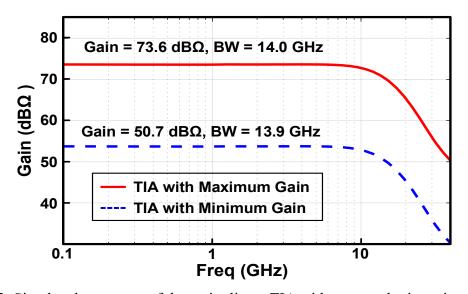

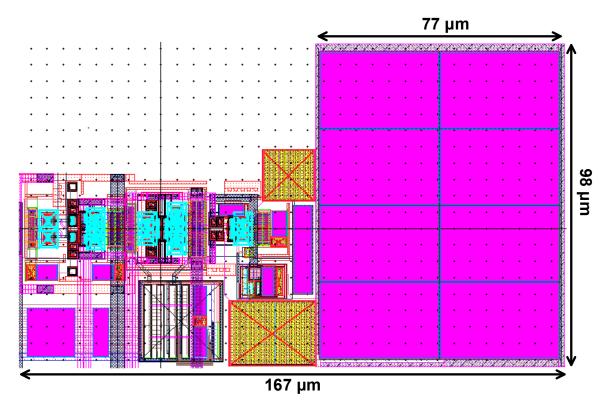

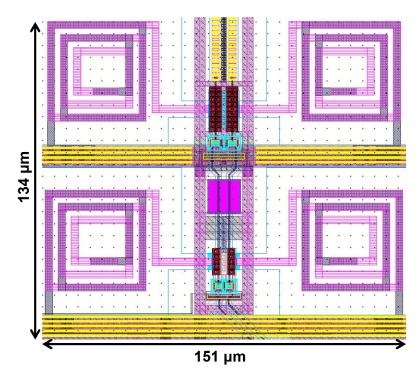

Post-layout simulations in Figure 3.13 show that the entire linear TIA achieves a gain up to 73.6 dB $\Omega$  with a BW of 14 GHz and provides a gain tuning range up to ~23 dB $\Omega$ , with a BW variation of around 0.1 GHz. The layout of the entire TIA, including DCOC circuits and IDAC is given in Figure 3.14 with a compact area of only 0.17 × 0.08 mm² thanks to the adoption of TAS-TIS topologies and active inductors. Capacitors used in DCOC circuits occupy almost half of the TIA area.

Figure 3.13. Simulated responses of the entire linear TIA with max. and min. gain settings.

Figure 3.14. Layout of the TIA with DCOC circuits.

## 3.3.3 Sampler with Integrated Equalizer

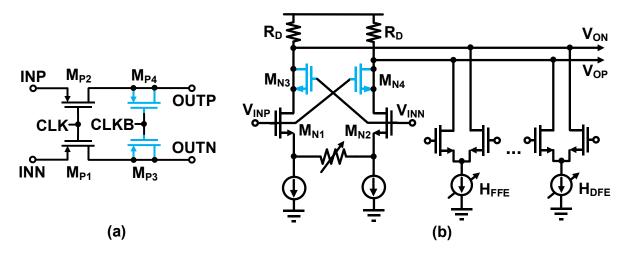

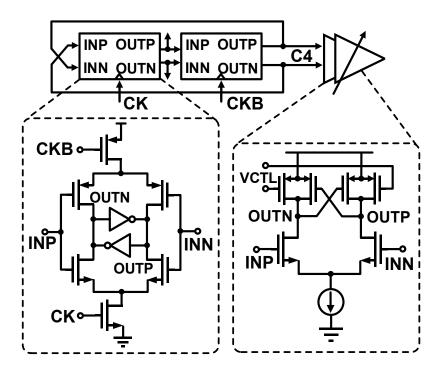

Figure 3.15. Block diagram of the half-rate FFE and DFE.

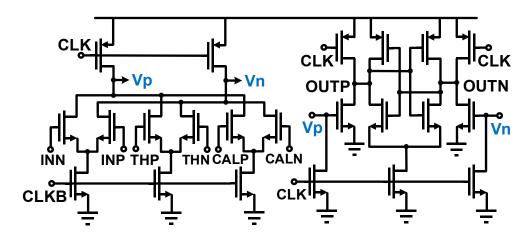

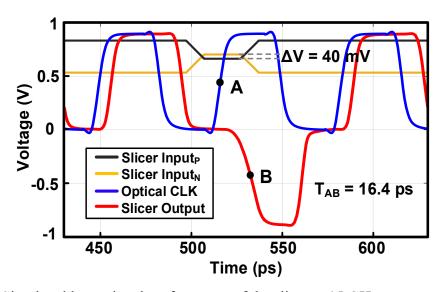

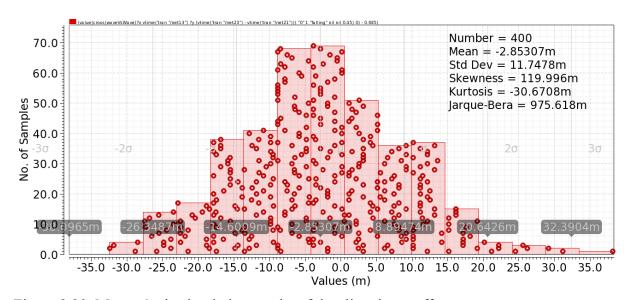

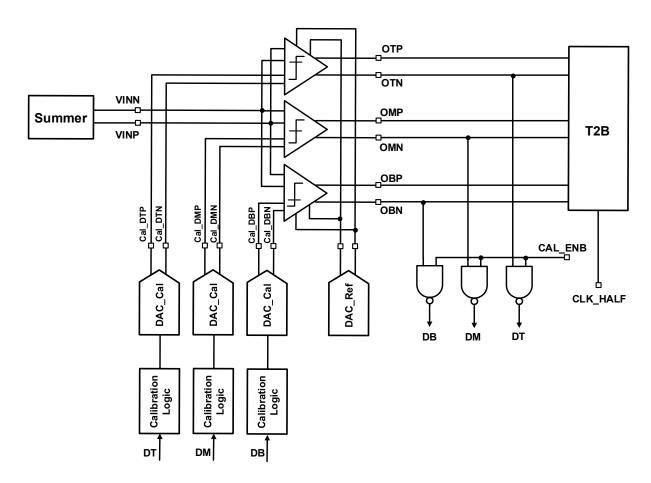

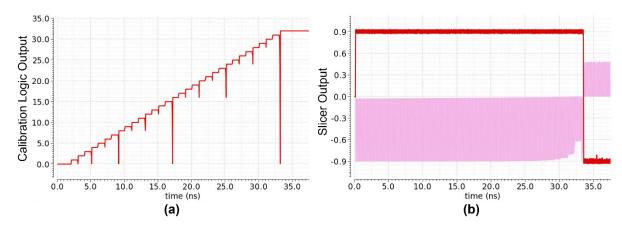

The full-rate input data is converted into two half-rate data streams at TIA output. The block diagram of half-rate PAM-4 sampler with FFE and DFE is shown in Figure 3.15. The precursor FFE is embedded with S/H circuits by a summer that performs summation of consecutive data samples. The 3-bit thermometer outputs, both before and after a set-reset (SR) latch, are fed